Изобретение сугносится к обработ-г ,ке цифровой информации.

Известен преобразователь кода из системы остаточных классов (СОК) в позиционный код, содержащий п каналов, где п - количество модулей чи,сла, выраженного в СОК, блок управления, накапливающий счетчик и многовходовую схему И. Каждый канал включает в себя сумзиирующий счетчик с коэффициентом пересчета, равным соответствующему модулю, приемный регистр остатка и схему сравнения 1

Недостатком этого устройства является низкое быстродействие, так как принцип, положенный в его основу, предусматривает перебор всех воз1 1ожных сочетаний остатков . I Наиболее близким к изобретению по техническому решению является преобразователь кода из системы остаточных классов в позиционный код, содержащий генератор тактовых импульсов, первый и второй элементы И, триггер, группу из п-вычитающих счетчиков, суммирующий счетчик, выход которого является выходом устройства, входы вычитающих счетчиков являются информационными входами устройства, счетные входы вычитаюпдих.

и суммирующего счетчика объеДОнены и подключены к выходу первого элемента И, первый вход которого соединен с выходом генератора тактовых.импульсов , а второй - с единичным выходом триггера, единичный вход . которого является управляющим входом устройства, а нулевой соединен с выходом второго элемента И, входы к610торого соединены с выходами соответствующих вычитающих счетчиков 2.

Недостатком такого устройства является низкое быстродействие, так как процесс преобразования сводится

15 к перебору всех сочетаний остатков.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что преобразователь кода из сис20темы остаточных классов в позиционный код, содержащий генератор тактовых импульсов, первый и второй элементы И, первый триггер, первый, второй, третий модульные счетчики,

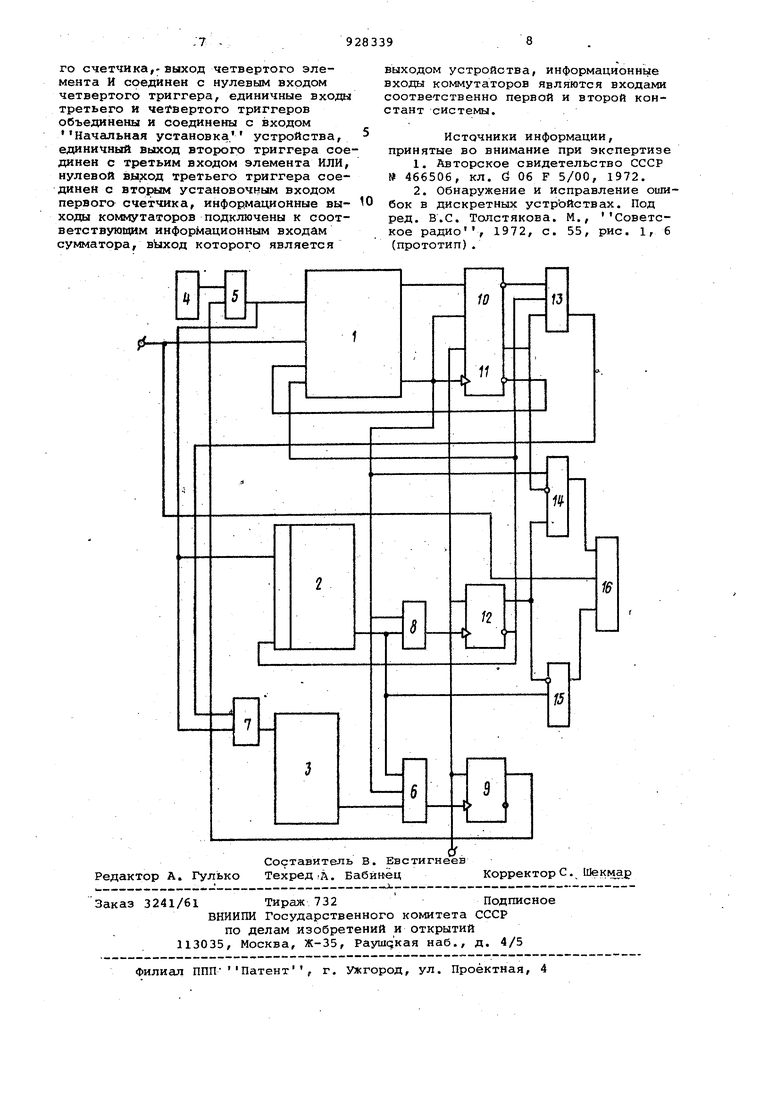

25 счетные входы первого и второго модульных счетчиков соединены между собой и с выходом первого элемента И, первый вход которого соединен с выходом генератора тактовых импуль30сов, а второй - с единичным выходом первого триггера, единичный вход ко торого соединен с входом Начальная установка устройства, а нулевой - с выходом второго элемента И, входы которого соедин ены с первыми Jвыходами соответствующих модульных счетчиков, первые входы которых являются информационными входами устройства, содержит сумматор, первый и второй коммутаторы, три триггера, два элемента И/ элемент ИЛИ, выход которого соединен, с первым входом третьего элемента И, второй вход которого соединен с выходом первого элемента И, а выход - со счетным входом третьего модульного счетчика второй выход первого модульного счетчика соединен с единичным входом второго триггера, нулевой вход которого соединен с единичным входом третьего триггера, с первым выходом первого модульного счетчика, с первым входом четвертого элемента И, с первым управляющим входом первого коммутатора. Второй упрешляющий вход которого соединен с единичным выходом третьего триггера и с первы входом элемента ИЛИ, второй вход которого соединен с первыми установочными входами первого и второго Модульных счетчиков и с нулевым выходом четвертого триггера, единичный выход которого соединен с треть им управляющим входом первого коммутатора и с первым управляющим вхо дом второго коммутатора, второй управляющий вход которого соединен со вторым входом Четвертого элемента И и перрым выходом второго модульного счетчи са, выход четвертого элемента И соединен с нулевым в&одом четвертого триггера, единичные входы третьего и четвертого триггеров объединены и соединены с входом Начальная установка устройства, единичный выход второго триггера соединен с третьим входом элемента ИЛИ, нулевой выход третьего триг гера соединен с вторым установочный входом первого счетчика, информационные выходы коммутаторов подключены к соответствующим информационн входам сумма;тора, выход которого является выходом устройства, информационные входы коммутаторов являют ся вхоДалви соответственно первой и второй констант системы. На чертеже представлена блок-схе ма предлагаемого преобразователя.: Блок-схема;содержит первый, второй и третий модульные счетчики 1-3 генератор тактовых импульсов 4, пер вый, второй, третий и четвертый эле менты И 5-8,, первый, второй, третий и четвертый триггеры 9-12, элемент ИЛИ 13, первый и в торой коммутаторы 14 и 15, сумматор l€. Преобразователь работает следующим образом. Для работы преобразователя необходимо модульные счетчики 1-3 расположить так, чтобы выполнялись следующие условия: Щ ..Рг/ щ т, и /А,, /г /т t / га где т, - наибольший модуль. Очевидно, что эти условия выполняются при любом наборе трех модулей, так как mi, У / Д® j 1, 2,3. Перед началом процесса преобразования в модульные счетчики 1-3 заносятся остатки преобразуемого числа а,, аг,аз по соответствующим модулям т ,iri2r iHj, образующим основание СОК. Одновременно,число ау заносится в сумматор 16. После этого сигнал Начальная установк,а .устанавливает в единичное состояние триггеры 9, 11, 12; в результате чего открывается элемент , закрываются коммутаторы 14 и 15°, а элемент ИЛИ 13 разрешен единичным сигналом с единичного выхода триггера 11 и своим выходным сигналом открывает третий элемент И 7. С выхода генератора тактовых импульсов 4 через открытый элемент И 5 непосредственно на вйчитающие входы счетчиков 1 и 2 и через элемент И 7 - на счетный вход модульного счетчика 3 начинают поступать вычитающие импульсы, дод воздействием которых модульные счетчики 1-3 меняют свои состояния причем сигнал с выхода МОДУЛЬНОГО счетчика 1, устанавливающий триггер 10 в единичное состояние, не влияет.в данный момент на работу преобразователя, так как элемент ИЛИ 13 разрешен сигналом с выхода триггера 11. Через q импульсов модульный счетчик 1 переходит в нулевое состояние, а на его первом выходе формируется сигнал, который обнуляет триггер 10 и опрашивает элемент И 6. В случае неравенства нулю содержимого одного из модульных счетчиков 2 и 3 триггер 9 остается в единичном состоянии и процесс преббраэовсшия продолжается. Спад сигнала на первом выходе счетг чика 1 обнуляет триггер 11, в результате чего элемент ИЛИ 13 начинает управляться сигналом с единичного выхода триггера 10 г а также снимается запрет с коммутатора 14. В основу принципа действия преобразователя положен тот факт, что при условии т roj, и т,, . Щд результат от пода чи на вход Модульных счетчиков 2 и 3 с коэффициентом пересчета соответственно т., , т и га импульсов идентичен результату подачи на их входы соответственно /mi /m и /пц /mj импульсов. Аналогичным ооразом результат подачи in -тг импульсов на

вход модульного счетчика 3 с коэффТГ циентом пересчета т эквивалентен подаче на его вход /т, mj,/m импульсов. Обнуленный триггер 11, воздействуя сигналом со своего нулевого выхода на второй управляющий вход модульного счетчика 1, меняет его коэффициент пересчета с величины га, на значение . Поскольку m I . /m-f/m, такая смена значения коэффициента пересчета не требует увеличения объема модульного счетчика 1, так как по услсэвию /m-r/mt , то сигнал на втором выходе модульного счетчика 1 поя.вляется раньше, чем модульный счетчик 1 достигает в очередной раз своего нулевого состояния. Этот сигнсш каждый раз устанавливает в единичное состояние триггер 10 и сигнал с выхода элемента ИЛИ 13 закрывает элемент И 7.Таким образом, за каждый цикл работы модельного счетчика 1 на счетный (вычитедащий) вход модульного счетчика 2 подается . импульсов, а на счетный (вычитающий) вход модульного счетчика 3 - . импульсов. В конце каждого цикла сигнал с первого выхода модульного счетчика 1 открывает коммутатор кодов 14, и на сумматор. 16 поступает константа щ, которая суммируется с содержимым сумматора 16. Одновременно этот сигнал опрашивает состояния модульных счетчиков 2 и 3 на элементе И б и отдельно - состояние модульного счетчика 2 на элементе И 8. При одновременном обнулении модульных счетчиков 1 и 2 на выходе элемента И 8 форвгаруется сигнал, после окончания которого триггер 12 обнуляется и сигналом со своего нулевого выхода устанавливает коэффициенты пересчета модульных х:четчиков 1 и 2 равными /m -mj/mj. Одновременно этот сигнал разрешает элемент ИЛИ 13 по третьему входу независимо от состояния, триггера 10, а

сигнал с единичного выхода триггера 12 закрывает коммутатор14 и снимает запрет с коммутатора 15. Модульные счетчики 1 и 2 начинают работать параллельно, и за каждый цикл их работы на счетный (вычитающий) вход модульного счетчика 3 подается /т, импульсов. В конце каждого дйкла сигнал с выхода модульного счетчика 2 открыв-ает коммутатор 15,/ и на сумматор 16 поступает коНстантг m.m, , которая суммируется с содержимым сумматора 16. Этот же сигнал вместе с сигналом на первом выходе счетчика 1 опрашивает состояние модульного счетчика 3 и при одновременном обнулении всех трех модульных счетчиков 1-3 на выходе элемента И 6 формируется сигнал, после

окончания которого триггер 9 обнуляется, и подача импульсов через 1элемент И 5 прекращается. На STOW процесс преобразования заканчивается, а позиционный код преобразуемого числа снимается с выхода сумматора 16.

Таким образом, применение модульных счетчиков с переменными коэффициентами пересчета, сумматора, коммутаторов , трех триггеров, двух элементов И и элемента ИШ с соответствующими связями позволяет существенно сократить время преобразования.

Формула изобретения Преобразователь кода из системы остаточных классов в позиционный код, содержащий генератор тактовш импульсов, первый и второй элементы И, первый триггер, первый, второй, третий модульные счетчики счетные входы первого и второго модульных счетчиков соединены между собой и с выходом первого элемента И,, первый вход -которого соединён с выходом генератора тактовых импульсов, а второй - с единичным выходом первогч триггера; единичный вход которого соединен с входом Начальная установка устройства, а нулевой - с выходом второго элемента-И, вхорл которого соединены с первыми а всодами соответствующих модульных счет чиков, первые йходы которых являются информационны7«м входами устройства, отличающийся тем, что,

5 с целью повьаиения быстродействия, он содержит сумматор, первый к второй коммуTaTOpfji, три триггера, дна элемента И, элемент ИЛИ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом первого Элемента И, а выход - со счетным входом третьего модульного счетчкка, второй выход первого модульного счетчика соединен с единичным входом второго триггера, нулевой вход а которого соединен с единичным входом третьего триггера, с перовым выходом первого модульного счетчика, с первым входом четвертого элемента И, с первым управляющим входом , первого коммутатора, второй управляющий вход которого соединен с единичным выходом третьего и с первым входом элемента ИЛИ, второй вход которого соединен с первыми установочными входами первого и второго модульных счетчиков и с нулевым выходом четвертого триггера, единичный выход КОТОРОГО соединен с третьим упрёшляющим входом первого коммутатора и с первым управляющим входом вторюго коммутатора, второй управляющий вход которого соединен с вторым входом четвертого элемента

5 И и первым выходом второго модульно

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода из системы остаточных классов в позиционный код | 1984 |

|

SU1200430A1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU924695A1 |

| Преобразователь непозиционного кода в двоичный код | 1984 |

|

SU1179547A1 |

| Преобразователь непозиционного кода в двоичный код | 1982 |

|

SU1083179A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1984 |

|

SU1257850A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь кода | 1982 |

|

SU1019435A2 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Устройство для преобразования числа из системы остаточных классов в позиционный код | 1985 |

|

SU1290536A1 |

Авторы

Даты

1982-05-15—Публикация

1980-06-05—Подача