Изобретение относится к вычислительной технике, в частности, к устройствам микропрограммного управления и может быть использовано при построении цифровых вычислительных машин и контроллеров с микропрограммным управлением. Известно микропрограммное устройст во управления, содернащее память микрокоманд, регистр микрокоманд, регист адреса, оперативную помять, регистр возврата 1 , Недостатком этого устройства является большой формат микрокоманды, необходимый для управления микропрограммным устройством. Наиболее близким к предлагаемому является устройство, содержащее блок памяти микрокоманд, регистр микрокоманд, блок управления, регистр адреса, регистр кода операции, первый, второй и третий элементы И, элемент ИЛИ, причем выход блока памяти микрокоманд соединен с входом регистра микрокоманд, первый выход которого соединен с первым входом второго элемента И, а второй выход -г с первым управляющим входом блока управления, , выход блока управления соединен с вторым входом второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, первый вход третьего элемента И соединен с выходом регистра кода операции, выход третьего элемента И соединен с третьим входом элемента ИЛИ, выход которого соединен с первым входом регистра адреса, выход регистра адреса соединен с. входом блока памяти микрокоманд (21. Недостатком такого устройства является большое количество оборудования . Цель изобретения - сокращение оборудования устройства, Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд.

регистр адресд, регистр кода операции, первый, второй и третий элементы И и элемент ИЛИ, причем выход блока памяти Микрокоманд соединен с входом регистра микрокоманд, выход первого элемента И соединен с первым входом элемента ИЛИ, второй и третий входы и выход которого соединены соответственно с выходами второго и третьего элементов И и первым входом регистра адреса, выход которого соединен с входом блока памяти микрокоманд, первый вход второго элемента И соединен с первым выходом регистра микрокоманд, первый вход третьего элемента И соединен с выхо дом регистра кода операции, вхрд которого является кодовым входом устройства, введены блок логического управления, блок блокировки кода операции, .регистр возврата и четвёртый элемент И, причем первый выход регистра микрокоманд соединен с кодовым входом блока блокировки кода операции, вход кода Пустая команда которого соединен с первым выходом блока логического управления, третий вход блока блокировки кода операции является установочным .входом, а выход - вьгходом устройства, второй выход регистра кода операции соединен с первым управляющим входом блока логического управления, второй упра яющий вход которого является входом логических условий устройства второй, третий, четвертый, пятый и щестой выходы блока логического управления соединены соответственно с первыми входами первого и 4etвертого элементов И, с вторыми входами второго и третьего элементов И и вторым входом регистра адреса, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с входом регистра возврата, выход которого соединён с вторым входом первого элемента И, при этом блок логического управления содер) .первый, второй, и третий элементы НЕ, первый, второй, третий, четвертый, пятый и шестой элементы И и первый, второй я третий элементы ИЛИ, причем входы первого, второго и третьего элементов НЕ являются первым управляю1ц,им входом блока, пер вый, второй и третий входы первого элемента И соединены соответственно с входом второго и с выходами первого и третьего элементов НЕ, первый и второй входы второго элемента .И соединены соответственно с входом первого и с выходом третьего элементов НЕ, первый, второй и третий входы третьего элемента И соединены соответственно с входами первого и второго и выходом третьего элементов НЕ, первый, второй и третий входы четвертого элемента И соединены соответственно с выходами первого и второго и входом третьего элементов НЕ, первый, второй и третий входы пятого элемента И соединены- соответственно с входом первого, выходам второго и входом третьего элементов НЕ, четвертый вход пятого элемента И является вторым управляющим входом блока, первый, второй и третий входы элемента И соединены соответственно с выходом первого и с входами второго и третьего элементов НЕ, первый и второй входы первого элемента ИЛИ соединены соответственно с выходами первого и второго элементов И, первый и. второй входы второго элемен та ИЛИ соединены соответственно с выходами четвертого и пятого элементов И, первый и второй входы третьего элемента ИЛИ соединены соответственно с выходами второго и пятого элементов И, выходы первого элемента ИЛИ, первого и третьего элементов И, второго элемента ИЛИ, шестого элемента И и третьего элемента ИЛИ являются, соответственно первым вторым, третьим, четвертым, пятым и шестым входами блока, при этом блок блокировки кода операции содержит п элементов 2И-2ИЛИ-НЕ и (n+l) элементов НЕ, причем первые входы элементов 2И-2ИЛИ-НЕ являются кодовым входом блока, а выходы соединены соответственно с входами-п элементов НЕ, выходы которых являются выходом блока, вторые входы элементов 2И2ИЛИ-НЕ соединены с входом .(п+1 )-го элемента НЕ, а третьи входы является установочным входом блока, выход (п+1)-го элемента НЕ соединен с четвертыми входами элементов 2И-2ИЛИ-НЕ вход {r.+i)-ro элемента НЕ является входом кода Пустая команда блока.

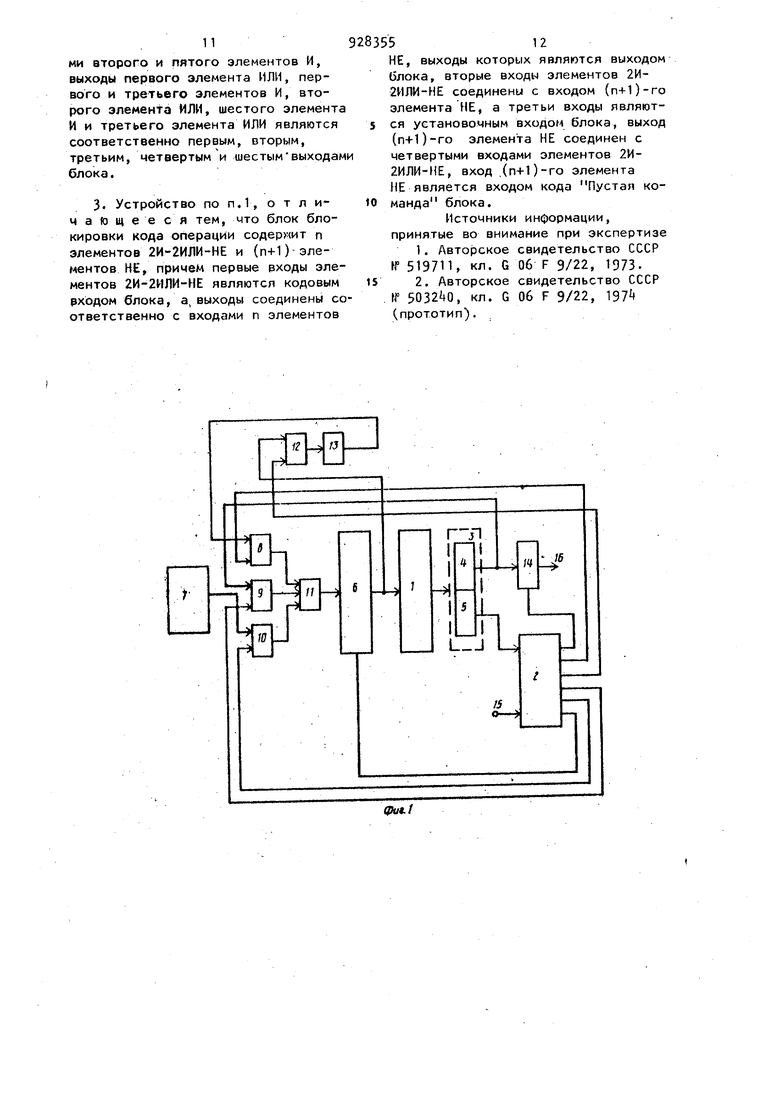

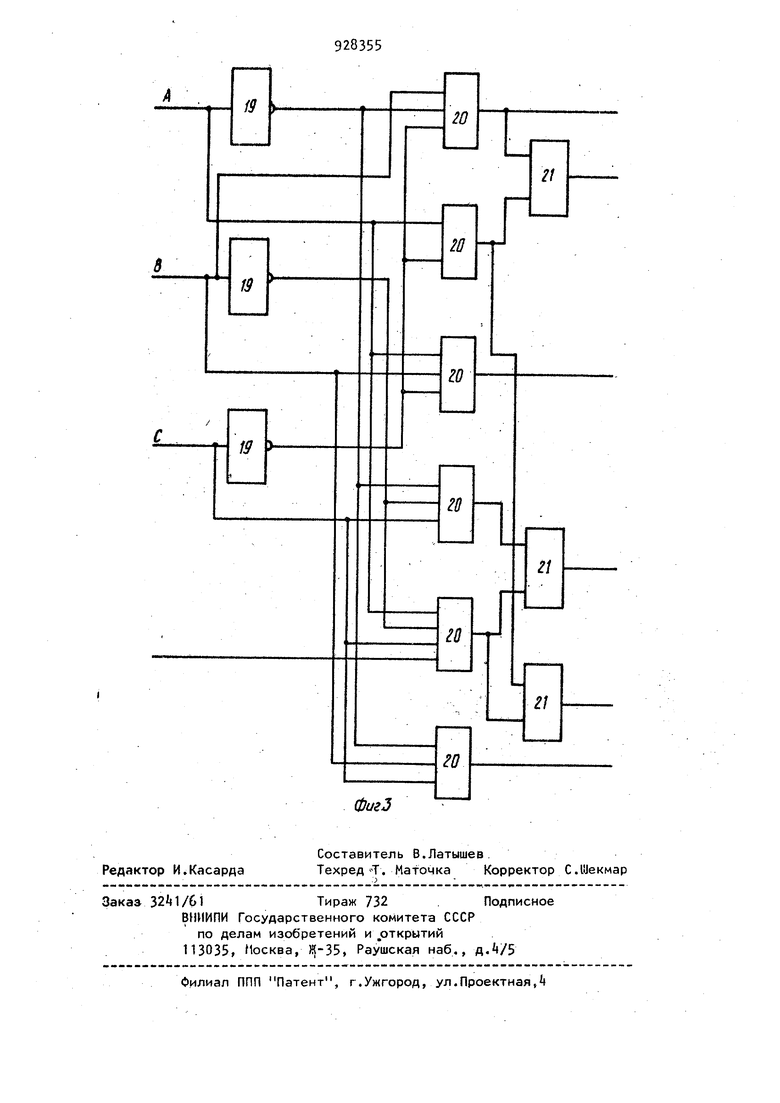

На фиг.1 представлена структурная схема Микропрограммного устройства . управления; на фиг.2 - структурная схема блока блокировки кода операции

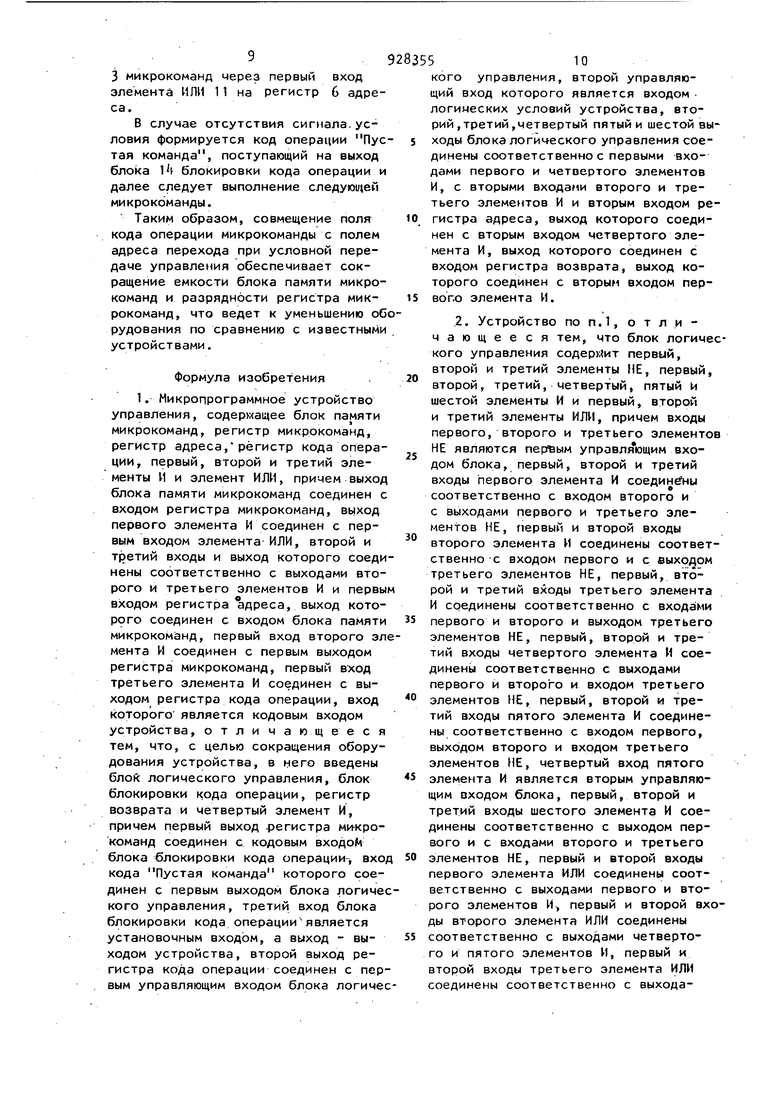

на фиг.З - структурная схема блока логического управления.

Микропрограммное устройство управления содержит блок 1 памяти микрокоманд, блок 2 логического управления, регистр 3 микрокоманд, содержащий поле. кода операции, совмещенное с полем адреса перехода и управляющее поле 5, регистр 6 адреса, регистр 7 кода операции, первый элемент И 8, второй элемент И 9, третий элемент И 10, элемент ИЛИ 11, четвертый элемент И 12, регистр

13возврата, блок It блокировки кода операции, вход 15 устройства, выход 1б устройства.

; Работа микропрограммного устрой- . ства управления осуществляется путем выборки микрокоманд из блока 1 памяти микрокоманд в регистр 3 микрокоманд. Регистр 3 микрокоманд содержит поле 1 кола операции микрокоманды, совмещенное с полем адреса перехода и управляющее поле 5, предназначенное для организации работы блока 2 управления. Код управляющего поля 5 из регистра 3 микрокоманд поступает на первый управляющий вход блока 2 логического управления и совместно с сигналом условия, поступающим на второй управляющий вход блока 2 логического управления, вырабатывает сигнал на соответствующем выходе этого блока.

Адрес текущей микрокоманды формируется в регистре 6 адреса, который может работать как счетчик микрокоманд.

Передача на выход устройства кода операции управляется блоком k блокиpoвkи кода операции. Схема блока

14блокировки кода операции функционально реализуется на базе N-ro количества мультиплексоров Два в один Пример конкретной реализации данного блока изобра ; ен на фиг.2. Этот блок может быть выполнен на базе элементов К155ЛР1, реализующих логическую функцию 2И-2ИЛИ-НЕ 17, и элементов К155ЛН1, реализующих логическую функ цию НЕ 18.

Взаимосвязи между указанными элементами в статике следующие.

В этом блоке вход Л соответствует первому входу блока k блокировки кода операции 14 (фиг.1), вход В соответствует второму входу блока k блокировки кода операции (фиг.1),

а выход С соответствует выходу 16 блока 14 блокировки кода операции

(фИГ;1).

Логические сигналы кода операции поступают на первые входы логических элементов 2И-2ИЛИ-НЕ 17. На вторые входы этих логических элементов поступает сигнал со входа В. Этот сигнал после инверсии элементом НЕ поступает на четвертые входы логических элементов 2И-2ИЛИ-НЕ 17. На третьи входы логических элементов 2И-ИЛИ-НЕ 17 постоянно подан код, соответствующий коду операции Пустая команда, который формируется подачей определенной комбинации сигналов логического нуля или логической единицы по входам Д1...ДИ для каждой KOHKpeTHOvi реализации, С выходов логических элементов 2И-2ИЛИ-НЕ 17 сигналы через инверторы, реализующие функцию НЕ, поступают на вход 16 блока 14 блокировки кода операции.

При поступлении логических сигналов кода операции по входу А и при наличии на входе В сигнала, имеющего уровень логической единицы, на выход С передается код операции. При подаче на вход В сигнала, имеющего уровень логического нуля, на выход С блока блокировки кода операци передается кодоперации Пустая команда.

Блок 2 логического управления функционально является преобразователем кода и монет быть выполнен па основе программируемого постоянного запоминающего устройства (ППЗУ), в частности на микросхеме К155РЕЗ, либо в виде комбинационной логической схемы (элементы НЕ 19, И 20 и ИЛИ 21), (фиг. 3).

Логика работы данного блока представлена в таблице истинности, где О - уровень логического О, 1 - уровень логической 1, X - неопределенное (ост. ,

В СD Qi О. гО. jQi, QS йб

А О О

01X О О О 1 О О

10X 11-0000

Продолжение таблицы

Взаимосвязи между указанными элементами в статике следующие.

При поступлении соответствующих крдов по первому и. второму управляющим входам блока 2 управления на его выходах появляются сигналы согласно таблице истинности.

Работает микропрограммное устройство управления следующим образом

В начальный момент работы в регистре 3 микрокоманд находится микрокоманда, в управляющем поле 5 ког торой содержится код, который поступает на первый управляющий вход блока вырабатывает на первом выходе блока 2 сигнал, позволяющий прохождение кода операции 1устая команда на ВЫХОД блока 14 блокировки кода операции. По окончании выполнения этой микрокоманды на пятом выходе блока управления вырабатывается сигнал, поступаюи ий на«второй вход третьего элемента И 10 и позволяющий передачу начального адреса микропрограммы с регистра 7 кода операции через третий вход /элемента ИЛИ 11 на регистр 6 адреса. С регистра адреса начальный адрес микропрограммы поступает в блок 1 памяти микрокоманд, из которого выбирается микрокоманда начала микропрограммы. Эта микрокоманда записывается в регистр 3 микрокоманд, с; управляющего поля 5 которого код поступает на первый вход блока 2 управления и при этом на первом вь1ходе блока 2 появляется сигнал, поступающий на второй вход блока k блокировки кода операции, что позволяет прохождение кода операции микрокоманды через блок Il блокировки кода операции на вход 16 устройства. По окончаний выполнения этой микрокоманды на шестом выходе блока управления появляется сигнал, разрешающий работу регистра 6 адреса в режиме работы счетчика микрокоманд, Далее следует выполнение последовательности микрокоманд по программе,

При построении микропрограмм часто возникает ситуация, когда микропрограмма содержит в себе микроподпрограммы. Для организации входа в в микроподпрограмму в поле кода операции регистра 3 микрокоманд записывается начальный адрес микроподпрограммы, а в управляющем поле 5 содержится код, который поступает на первый управляющий вход блока 2, на первом выходе которого появляется сигнал, поступаю1ций на второй вход блока И блокировки кода операции, что позволяет прохождение кода операции Пустая команда на выход устройства. По окончании выполнения этой микрокоманды адрес перехода поступает со второго выхода регистра 3 микрокоманд через второй элемент И 9 и элемент ИЛИ 11 на регистр 6 адреса. Адрес текущей микрокоманды, увеличенный на два, запоминается в регистре 13 возврата. В конце выполнения, микроподпрограммы последняя микрокоманда содерж1|Т в управляющем поле 5 код, который поступает на первый вход блока 2 и вырабатывает на втором выходе блока 2 сигнал, обеспечивающий прохождение текущего адреса микропрограммы с регистра 13 возврата через первый вход элемента ИЛИ 11 на вход регистра 6 адреса.

При наличии в микропрограмме микрокоманд с условием, в поле ( кода операции записывается адрес перехода по условию, а управляющее поле 5 содержит код,Который поступает на первый вход блока 2 логического управления, на первом выходе которого появляется сигнал, поступающий на второй вход блока 14 блокировки кода операции, что позволяет прохождение кода операции Пустая команда на выход устройства блокировки, По окончании выполнения этой микрокоманды код адреса перехода поступает с первого выхода регистра 3 микрокоманд через первый вход 6 адреэлемента ИЛИ 1 1 на регистр са. В случае отсутствия сигнала.условия формируется код операции Пус тая команда, поступающий на выход блока 1t блокировки кода операции и далее следует выполнение следующей микрокоманды. Таким образом, совмещение поля кода операции микрокоманды с полем адреса перехода при условной передаче управления обеспечивает сокращение емкости блока памяти микрокоманд и разрядности регистра микрокоманд, что ведет к уменьшению об рудования по сравнению с известными устройствами. Формула изобретения 1. Микропрограммное устройство управления, содержащее блок памяти микрокоманд, регистр микрокоманд, регистр адреса,регистр кода операции, первый, второй и третий элементы И и элемент ИЛИ, причем выход блока памяти микрокоманд соединен с входом регистра микрокоманд, выход первого элемента И соединен с первым входом элемента ИЛИ, второй и третий входы и выход которого соеди нены соответственно с выходами второго и третьего элементов И и первы входом регистра 1здреса, выход которого соединен с входом блока памяти микрокоманд, первый вход второго эл мента И соединен с первым выходом регистра микрокоманд, первый вход третьего элемента И соединен с выходом регистра кода операции, вход которого является кодовым входом устройства, отличающееся тем, что, с целью сокращения оборудования устройства, в него введены блок логического управления, блок блокировки кода операции, регистр возврата и четвертый элемент И, причем первый выход .регистра ми-крокоманд соединен с кодовым входом блока блокировки кода операции, вхо кода Пустая команда которого соединен с первым выходом блока логиче кого управления, третий вход блока блокировки кода операцииявляется установочным входом, а выход - выходом устройства, второй выход регистра кода операции соединен с пер вым управляющим входом блока логиче 10 кого управления, второй управляющий вход которого является входом логических условий устройства, вторий,третий,четвертый пятый и шестой выходы блока логического управления соединены соответственное первыми входами первого и четвертого элементов И, с вторыми входами второго и третьего элементов И и вторым входом регистра адреса, выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с входом регистра возврата, выход которого соединен с вторым входом первогю элемента И. .2. Устройство по п. 1, о т л и чающееся тем, что блок логического управления содерх ит первый, второй и третий элементы НЕ, первый, второй, третий, четвертый, пятый И шестой элементы И и первый, второй и третий элементы ИЛИ, причем входы первого, второго и третьего элементов НЕ являются первым управляющим входом блока, первый, второй и третий входы первого элемента И соединёны соответственно с входом второго и с выходами первого и третьего элементов НЕ, первый и второй входы второго элемента И соединены соответственно с входом первого и с третьего элементов НЕ, первый, второй и третий входы третьего элемента И соединены соответственно с входами первого и второго и выходом третьего элементов НЕ, первый, второй и третий входы четвертого элемента И соединены соответственно с выходами первого и второго и входом третьего элементов НЕ, первый, второй и третий входы пятого элемента И соединены соответственно с входом первого, выхЬдом второго и входом третьего элементов НЕ, четвертый вход пятого элемента И является вторым управляющим входом блока, первый, второй и третий входы шестого элемента И соединены соответственно с выходом первого и с входами второго и третьего элементов НЕ, первый и второй входы первого элемента ИЛИ соединены соответственно с выходами первого и второго элементов И, первый и второй входы второго элемента ИЛИ соединены соответственно с выходами четвертого и пятого элементов И, первый и второй входы третьего элемента ИЛИ соединены соответственно с выходами второго и пятого элементов И, выходы первого элемента ИЛИ, первого и третьего элементов И, второго элемента ИЛИ, шестого элемент И и третьего элемента ИЛИ являются соответственно первым, вторым, третьим, четвертым и шестымвыхода блока. 3. Устройство по П.1, отличающееся тем, что блок блокировки кода операции содержит п элементов 2И-2ИЛИ-НЕ и (n+l) элементов НЕ, причем первые входы элементов 2И-2ИЛИ-НЕ являются кодовым рходом блока, а, выходы соединены со ответственно с входами п элементов 5 НЕ, ВЫХОДЫ которых являются выходом блока, вторые входы элементов 2И2ИЛИ-НЕ соединены с входом (п+1)-го элемента НЕ, а третьи входы являются установочным входом блока, выход (n-f1)ro элемента НЕ соединен с четвертыми входами элементов 2И2ИЛИ- 1Е, вход ,(п+1)-го элемента НЕ является входом кода Пустая команда блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР И° 5197П, кл. G 06 F 9/22, 1973. 2.Авторское свидетельство СССР № , кл. G 06 F 9/22, 197 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Устройство для отладки многомодульной ЦВМ | 1987 |

|

SU1564630A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Устройство микропрограммного управления | 1986 |

|

SU1339560A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

19

20

Авторы

Даты

1982-05-15—Публикация

1980-02-26—Подача