(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ПАМЯТИ о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения характеристик сетей | 1984 |

|

SU1242980A1 |

| Устройство для формирования адресов памяти | 1984 |

|

SU1256027A2 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Многоканальный коммутатор | 1979 |

|

SU809291A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

| Устройство для определения координат центра изображения | 1980 |

|

SU991452A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для гистограммной обработки изображений объектов | 1989 |

|

SU1667106A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ ЛЕКСИЧЕСКИХ МНОЖЕСТВ | 1990 |

|

RU2022354C1 |

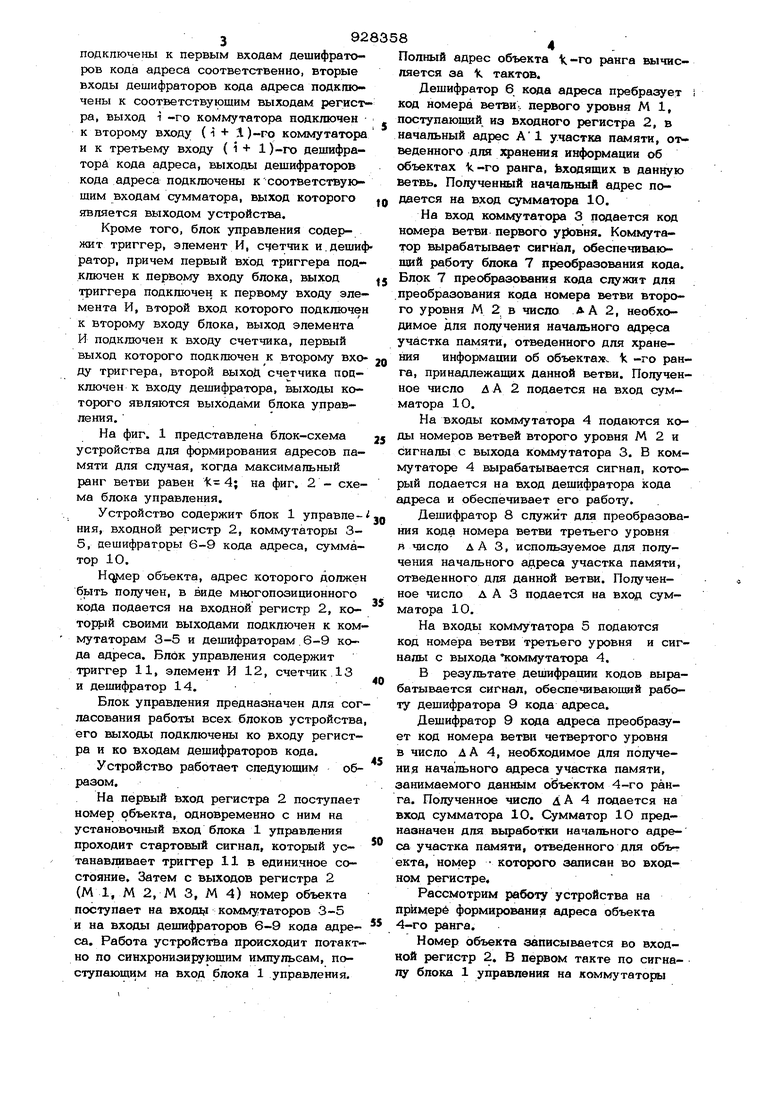

Т зобретение относится к вычислительной технике и может применяться дпя фо мирования адресов, по которым хранится информация в памяти. Известно устройство содержащее коммутаторы; счетчики, дешифраторы и ключи 1. Недоста тком такого устройства является то,что оно может использоваться только в тех случаях, когда данные располагаются в виде таблиц. Наиболее близким по технической сущ ности к предпагаемому, является устройство, содержащее входные адресные .шины, выходные считывающие шины, регист ры, дешифраторы, коммутаторы и ключи 23. Недостатками данного устройства являются низкое быстродействие и большие аппаратурные затраты, связанные с тем, что искомое слово может быть выбрано только по сигналу, полученному после де шифрации последней буквы заданного адресного слова. Цель изобретения - расширение функциональных возможностей устройства, за i счет обеспечения формирования адресов по заданным словам в тех случаях, когда объекты образуют древовидную струк-о туру, а запрос может быть за объект любого ранга. Поставленная.цель достигается тем, что в устройство, содержащее блок управления регистр и группу из (fc -1) коммутаторов (где V максимальный ранг адреса), причем первый вход регистра подключен к информационному входу устройства, выходы с первого по ( - 1)-й регистра подключены к первым входам коммутаторов соответственно, введены сумматор и i. дешифратороэкоааацреса, причем первый вход блока управления яв ляется установочным входом устройства, второй вход блока управления является входом синхронизации устройства, первый выхоа блока управления подключен к управляющему входу регистра, выходы блока управления со второго по ( 1 )-й

подключены к первым входам дешифраторов кода адреса соответственно, вторые входы дешифраторов кода адреса подкпвочены к соответствующим выходам регистра, выход -i -го коммутатора подключен к второму входу (i + 1)-го коммутатора и к третьему входу ( 1 + 1 )-го дешифратора кода адреса, выходы дешифраторов кода адреса подключены к соответствующим входам сумматора, выход которого является выходом устройства.

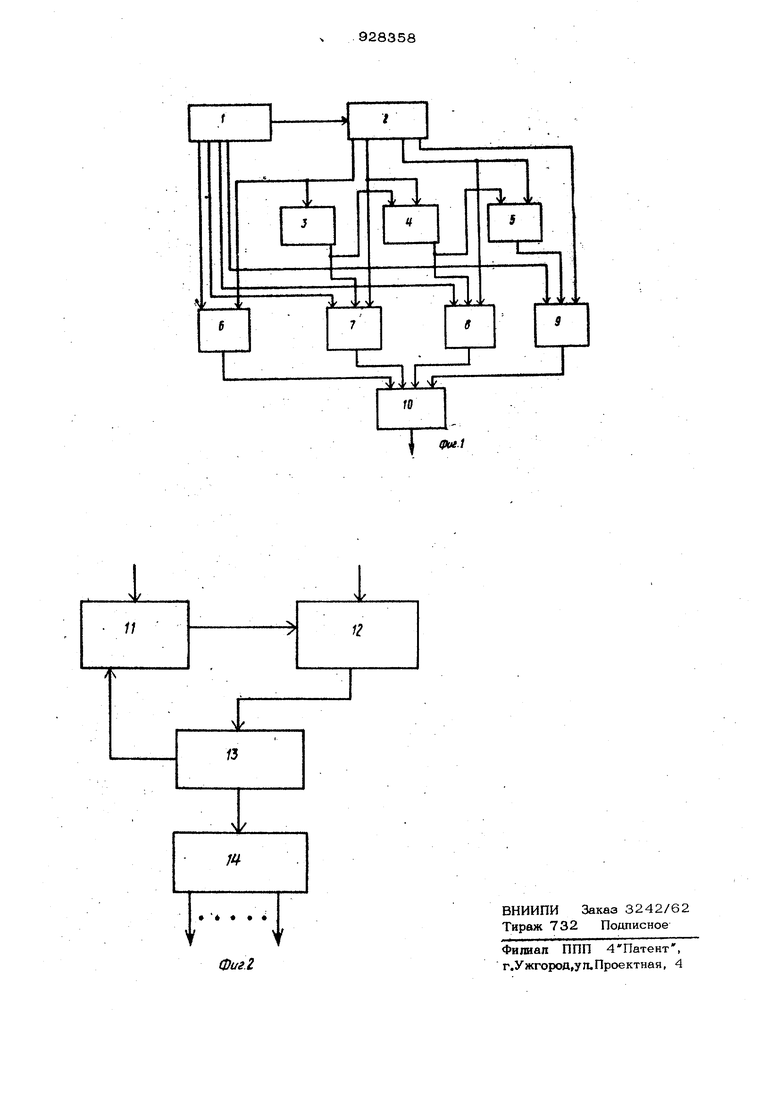

Кроме того, блок управления содержит триггер, элемент И, счетчик и.дешифратор, причем первый вход триггера подключен к первому входу блока, выход триггера подключен к первому входу элемента И, второй вход которого подключен к второму входу блока, выход элемента И подключен к входу счетчика, первый выход которого подключен к второму входу триггера, второй выхоД счегчика подключен к входу дешифратора, выходы которого являются выходами блока управления, На фиг. 1 представлена блок-схема устройства для формирования адресов памяти для случая, когда максимальный ранг ветви равен 1 4; на фиг. 2 - схема блока управления. Устройство содержит блок 1 управпения, входной регистр 2, коммутаторы 35, дешифраторы 6-9 кода адреса, сумматор 10. HqMep объекта, адрес которого должен бь1ть получен, в виде многопозиционного кода подается на входной регистр 2, кото1Лз1й своими выходами подключен к коммутаторам 3-5 и дешифраторам. 6-9 кода адреса. Блок управления содержит триггер 11, элемент И 12, счетчик . 13 и дешифратор 14. Блок управления предназначен для сог ласования работъ всех блоков устройства его выходы подключены ко рходу регистра и ко входам дешифраторов кода. Устройство работает следующим образом. На первый вход регистра 2 поступает номер объекта, одновременно с ним на установочный вход блока 1 управления проходит стартовый сигнал, который устанавливает триггер 11 в единичное состояние. Затем с выходов регистра 2 (М 1, М 2, М 3, М 4) номер объекта поступает на вхош коммутаторов 3-5 и на входы дешифраторов 6-9 кода адреса. Работа устройства происходит потакт- но по синхронизирующим импульсам, поступающим на вход блока 1 управления.

Полный адрес объекта It -го ранга вычисляется за 1 тактов.

Дешифратор 6 кода адреса пребразует i код номера ветви-, первого уровня М 1, поступающий из входного регистра 2, в начальный адрес А1 участка памяти, от веденного для хранения информации об объектах k-ro ранга, Ьходяших в данную ветвь. Полученный начальный адрес подается на вход сумматора 1О,

На вход коммутатора 3 подается код номера ветви первого уровня. Коммутатор вырабатывает сигнал, обеспечиваюший работу блока 7 преобразования кода, Блок 7 преобразования кода служит для преобразования кода номера ветви второго уровня М 2 в число ДА 2, необходимое для получения начального адреса участка памяти, отведенного для хранения информации об объекта -. Ч -го ранга, принадлежащих данной ветви. Полученное число 4 А 2 подается на вход сумматора Ю. На входы коммутатора 4 подаются номеров ветвей второго уровня М 2 и Сигналы с выхода коммутатора 3. В коммутаторе 4 вырабатывается сигнал, который подается на вход дешифратора кода адреса и обеспечивает его работу. Дешифратор 8 служит для преобразования кода номера ветви третьего уровня я число дА 3, используемое для получения начального адреса участка памяти, отведенного для данной ветви. Полученное число Д А 3 подается на вход сумматора 10. На входы коммутатора 5 подаются код номера ветви третьего уровня и сигналы с выхода коммутатора 4. В результате дешифрации кодов вырабатывается сигнал, обеспечиваюший работу дешифратора 9 кода адреса. Дешифратор 9 кода адреса преобразует код номера ветви четвертого уровня в число ДА 4, необходимое для получения начального адреса участка памяти, занимаемого даннь1м объектом 4-го ранга. Полученное число дА 4 подается на вход сумматора 1О. Сумматор 10 предназначен для выработки начального адре- са участка памяти, отведенного для объгекта, номер которого записан во входном регистре. Рассмотрим работу устройства на примере формирования адреса объекта 4-го ранга, Номер объекта записывается во входной регистр 2. В первом такте по сигна У блока 1 управления на коммутаторы 3-5 и дешифраторы 6-9 подаются коды номеров ветвей. При этом с выхода коммутаторов 3-5 на дешифраторы подаются сигналы, обеспечивающие их работу, а с выхода дешифратора 6 на сумматор 1О подается число А 1. Таким образом, в сумматор записан начальный адрес, соот ветствующий номеру ветви первого уровн Во втором такте по сигналу блока 1 управления с выхода дешифратора 7 на сумматор подается число д А 2. В сум маторе 10 образуется начальный адрес, соответствующий номеру ветви второго уровня (А2 А1+ лА 2). В третьем такте с выхода дешифратора 8 на cyMMaiop Ю подается число Д А 3 и в последнем образуется начальный адрес, соответствующий номеру ветви третьего уровня (А 3 А 1 + А 2 + + ДА 3). В четвертом такте с выхода дешифратора 9 на сумматор lO подается шсло Д А 4 и в сумматоре начальный адрес o6beKTaf четвертого ранга (А 4 А1+ ЛА2+ДАЗ+ДА4). Очевидно, что для формирования начального адреса объекта 1с,-го ранга необходимо 1 .тактов. Если объект имеет j)aHr i -го, то соответствующий ,ему Начальный адрес дет получен не в /k -ом такте, а ранее. Количество элементов, используемъ1Х для построения дешифратора пропорционально разрядностивходного слова. Так в пирамидальном дешифраторе количество элементов И определяется зависимостью (2 - 1) где S - количество элементов И; - количество разрядов. Использование нескольких дешифраторов в формировании адреса объекта, заданного словом, уменьшает количество оборудования в устройстве. Таким образом, предлагаемое устройство o6ecne4HBaet формирование адресов по заданным словам в тех случаях, когда объекты образуют древовидную структуру, а запрос может быть сделан за объект шобого ранга. Кроме того, предпагаемое устройство требует меньших затрат оборудования по сравнению с извест ными... Формула изобретения 1. Устройство для формирования адресов памяти, содержащее блок управления, регистр и группу из { - 1) коммутатор ров, причем первый вход регистра подключен к информационному взюду устройства, выходы с первого по (V - 1 )-й регистра подключены к первым входам коммутаторов соответственно, отличающееся тем, что, с целью рао тирания функциональных возможностей за счет обеспечения формирования адресов по заданным словам, в него введены сумматор и дешифраторов кода адре Р ° управления является установочным входом устройства, второй вход блока управления, является входом синхронизации устройства, первый выход блока управления подключен к управляющему входу регистра, выходы блока управления со второго по (V. 1 )-й подключены к первым входам дешифраторов кода адреса соответственно, вторые входы дешифраторов ко; адреса подключены к соответствующим выходам регистра, выход i -го коьлмутатора подключей к второму входу (i + 1 )-га коммутатора и к третьему входу ( л + 1 )-го дешифратора кода адреса, выходы дешифраторов кода адреса подключены к соответствующим входам сумматора, выход которого является выходом устройства. 2. Устройство, по п. 1, отличающее с я тем, что блок управления содержит триггер, элемент И, счетчик и дешифратор, причем первый вход триггер а подключен к первому входу блока, выход триггера подключен к первому входу элемента И, второй вход которого подключен к второму входу блока, выход элемента И подключен к входу счетчика, первый выход которого подключен к второму входу триггера, второй выход счет- чика подключен к входу дешифратора, выходы которого являются выходами блока управления. Источники информации, принятые во внимание при экспертизе 1.Патент США N 3678461, кл. G Об F 15/4О,. опублик. 1972. 2.Авторское свидетельство СССР NO 447375, кл. Q 11 С 7/Ор, 1974 (прототип).

If f

11

j (JM.l

Авторы

Даты

1982-05-15—Публикация

1980-01-04—Подача