(5t) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1552229A1 |

| Запоминающее устройство | 1987 |

|

SU1532976A1 |

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| Устройство для поиска информации | 1989 |

|

SU1686464A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Запоминающее устройство | 1987 |

|

SU1483492A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

. I Изобретение относится к запоминаю щим устройствам и, может быть использовано для создания систем оперативной памяти для решения информационнологических задач.

Известно запоминающее устройство, содержащее одноразрядные блоки памяти, параллельно соединенные по адресным шинам и управляющим шинам Чтение/запись и Выбор кристалла, причем информационное слово подается параллельно на информационные входы и считывается с выходов блоков памяти Гп.

Недостатком известного устройства является невозможность применения его для решения инфррмационно-логи- ческих и других задач, оперирующих таблицами.

Наиболее близким техническим решением к данному изобретению является запоминающее устройство, содержащее одноразрядные блоки памяти, параллельно соединенные по управляющим

и cooтвefcтвyющим адресным входам, регистр слова и коммутатор, одни из входов которого соединены с шиной управления, другие входы - с информационными входами устройства, а выходы ко;амутатора соединены соответственно со входами регистра слова Г2

Недостатками этого устройства являются невозможность применения его .для решения задач, оперирующих табtoлицами, например, задач матричной алгебры и информационно-логических, так как оно не обеспечивает возможность параллельного чтения/записи одноименных разрядов слов в смежных

«5 ячейках памяти за один цикл работы, а также низкое быстродействие.

.- , . Целью изобретения является повышение быстродействия и расширения

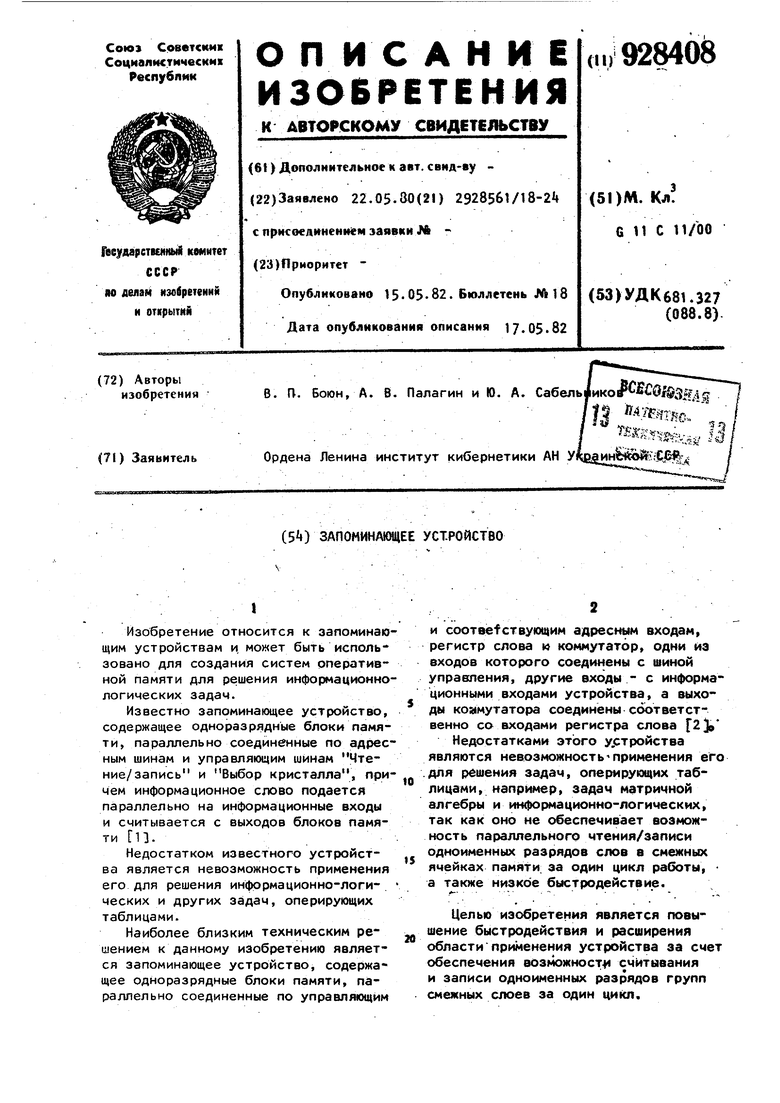

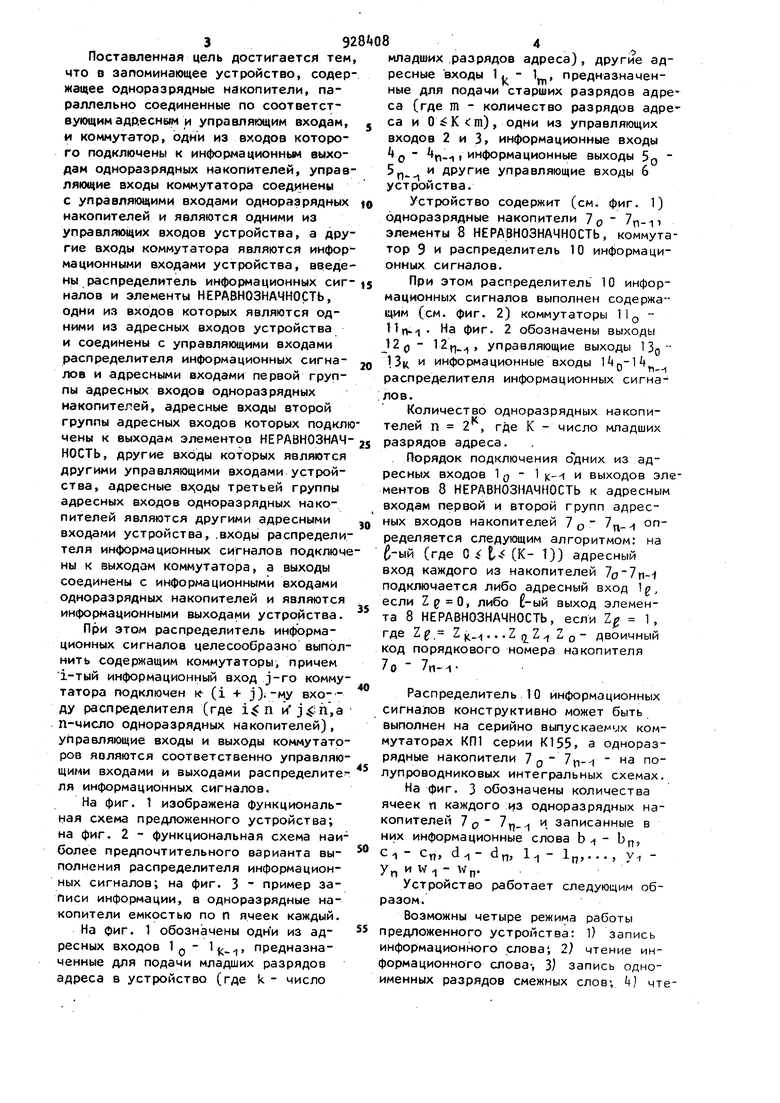

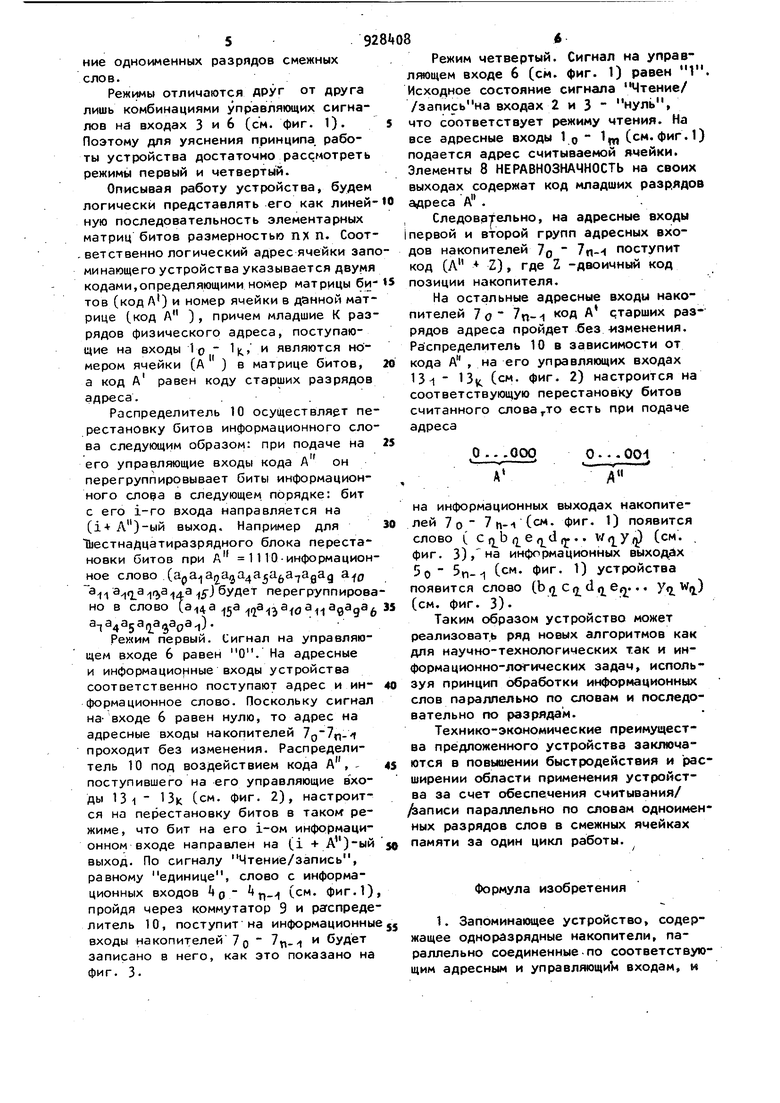

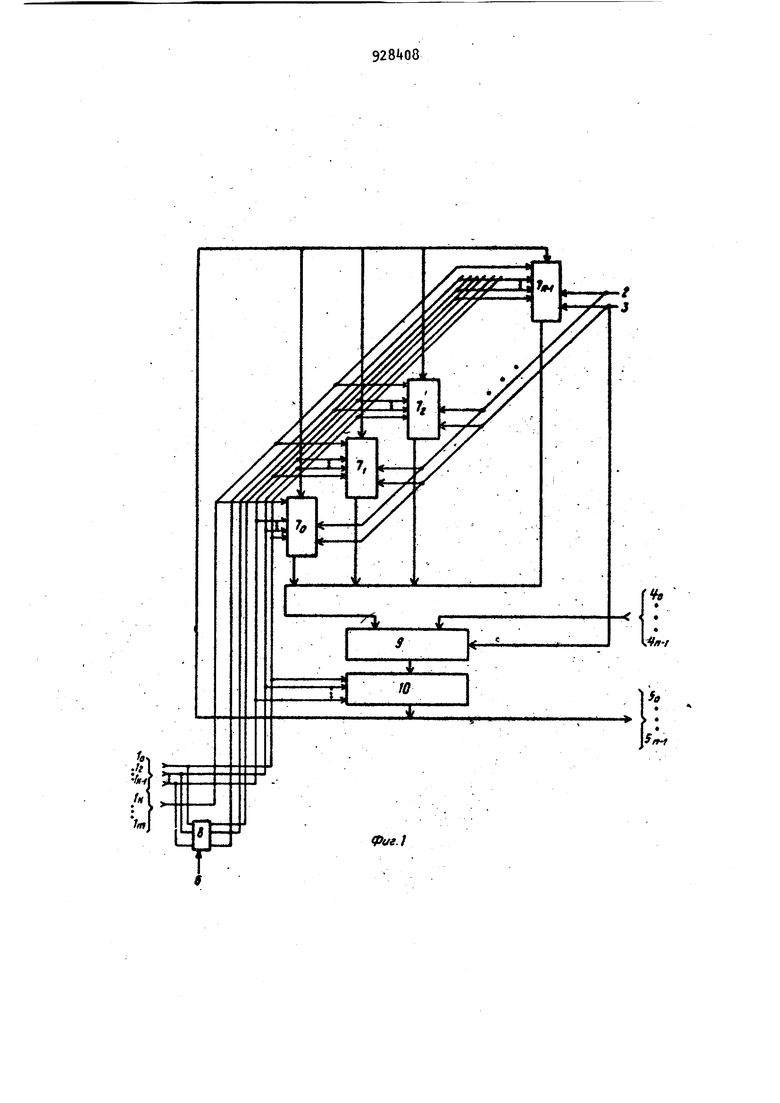

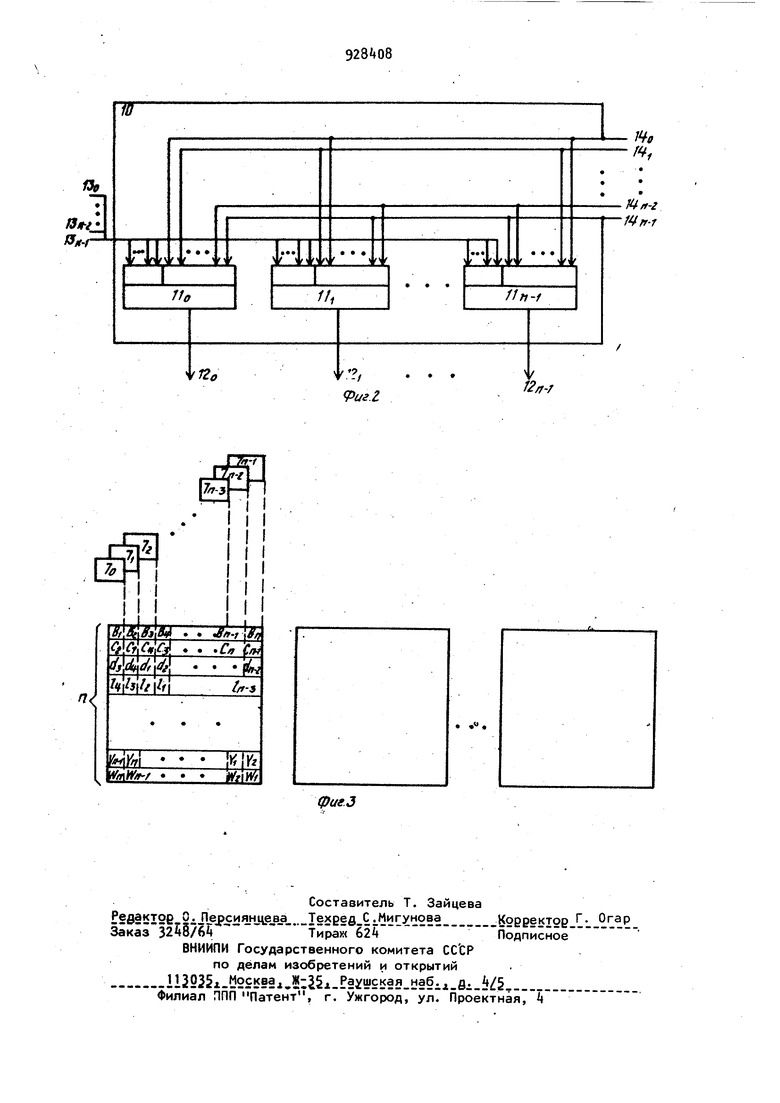

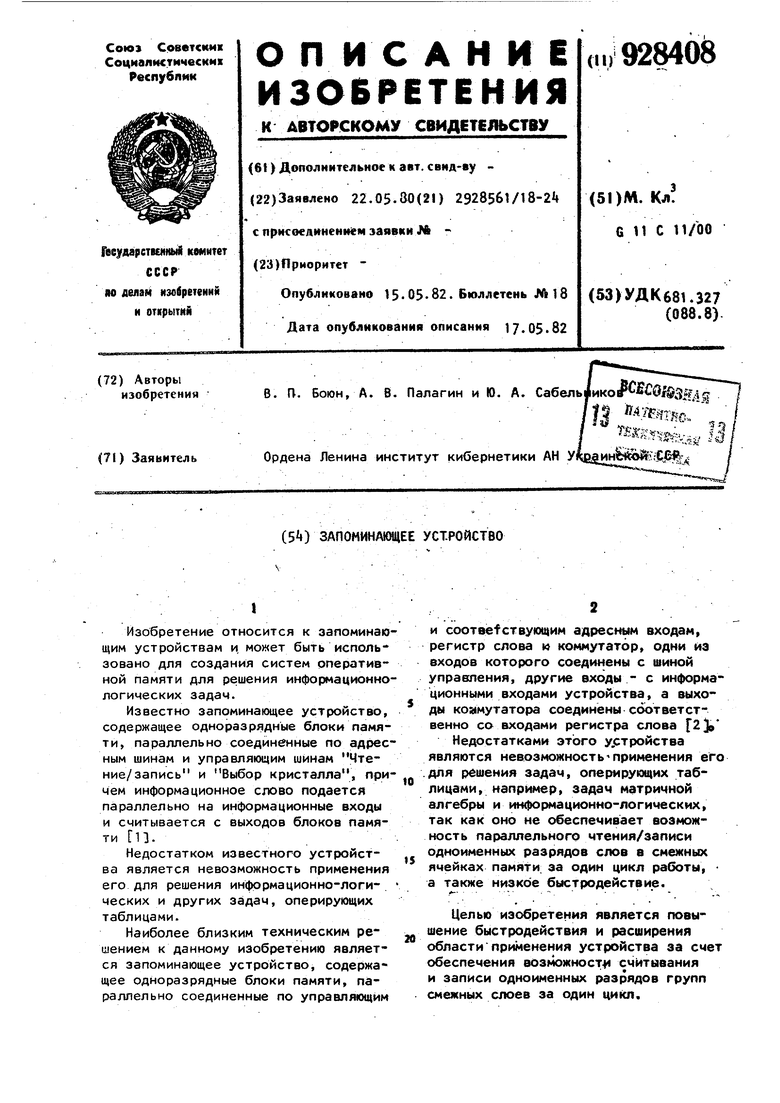

20 областиприменения устройства за счет обеспечения возможности считывания и записи одноименных разрядов групп смежных слоев за один цикл. 92 Поставленная цель достигается тем, что в запоминающее устройство, содержащее одноразрядные накопители, параллельно соединенные по соответствующим аддесньм и управляющим входам, и коммутатор, одни из входов которого подключены к информационным выходам одноразрядных накопителей, управляющие входы коммутатора соединены с управляющими входами одноразрядных накопителей и являются одними из управлгаощих входов устройства, а другие входы коммутатора являются информационными входами устройства, введв ны распределитель информационных сигналов и элементы НЕРАВНОЗНАЧНОСТЬ, одни из входов которых являются однмми из адресных входов устройства и соединены с управляющими входами распределителя информационных сигнаж в и адресными входами первой группы адресных входов одноразрядных накопителей, адресные входы второй группы адресных входов которых подклю чены к выходам элементов НЕРАВНОЗНАЧНОСТЬ, другие входы которых являются другими управляющими входами устройства, адресные третьей группы адресных входов одноразрядных накопителей являются другими адресными входами устройства, .входы распределителя информационных сигналов подключе ны к выходам коммутатора, а выходы соединены с информационными входами одноразрядных накопителей и являются информа44ионными выходами устройства. При этом распределитель информационных сигналов целесообразно выполнить содержащим коммутаторы, причем i-тый информационный вход j-ro коммутатора подключен к (i + j).-му вхо-ду распределителя (где i п ,a П-число одноразрядных накопителей), управляющие входы и выходы коммутаторов являются соответственно управляющими входами и выходами распределите ля информационных сигналов. На фиг. 1 изображена функциональная схема предложенного устройства; на фиг. 2 - функциональная схема наиболее предпочтительного варианта выполнения распределителя информационных сигналов; на фиг. 3 - пример записи информации, в одноразрядные накопители емкостью по п ячеек каждый. На фиг. 1 обозначены одни из адресных входов Q предназначенные для подачи младших разрядов адреса в устройство (где k - число младших .разрядов адреса), другие адресные входы 1 i - , предназначенные для подачи старших разрядов адреса (где m - количество разрядов и т), одни из управляющих входов 2 и 3, информационные входы I 1°Р зционные выходы 5о 5р. и другие управляющие входы 6 устройства. Устройство содержит (см. фиг. 1) одноразрядные накопители 7о элементы 8 НЕРАВНОЗНАЧНОСТЬ, коммутатор 9 и распределитель 10 информационных сигналов. При этом распределитель 10 информационных сигналов выполнен содержащим (см. фиг. 2) коммутаторы llg 1п.-1 з фиг. 2 обозначены выходы 120 - 12f , управляющие выходы 13 13ц и информационные входы распределителя информационных сигнаКоличество одноразрядных накопителей п 2 , где К - число младших разрядов адреса. Порядок подключения одних из адресных входов 1 Q - 1 IC--1 и выходов элементов 8 НЕРАВНОЗНАЧНОСТЬ к адресным входам первой и второй групп адресных входов накопителей 7о определяется следующим алгоритмом: на |5-ый (где О t- (К- 1)) адресный вход каждого из накопителей подключается либо адресный вход Ig, если , либо Е-ЫЙ выход элемента 8 НЕРАВНОЗНАЧНОСТЬ, если Z 1, где Zf . Z li. ... Z Q Z f Z 0 - двоичный код порядкового номера накопителя 7о 7|1--1Распределитель.10 информационных сигналов конструктивно может быть выполнен на серийно выпускаемых коммутаторах КП1 серии К155, а одноразрядные накопители 7 - ) - на полупроводниковых интегральных схемах. На фиг. 3 обозначены количества ячеек п каждого ;из одноразрядных накопителей 7о Ч записанные в них информационные слова b - Ь, с - с, d, 1 П . Устройство работает следующим образом. Возможны четыре режима работы предложенного устройства: 1) запись информационного слова , 2 чтение информационного слова-, 3) запись одноименных разрядов смежных слов-, l чтение одноименных разрядов смежных слов. Режимы отличаются ДРУг от друга лишь комбинациями управляющих сигналов на входах 3 и 6 (см. фиг. 1). Поэтому для уяснения принципа работы устройства достаточно рассмотреть режимы первый и четвертый. Описывая работу устройства, будем логически представлять его как линейную последовательность элементарных матриц битов размерностью пх п. Соот. ветственно логический адрес ячейки зап минающего устройства указывается двумя кодами,определяющими номер матрицы битов (код л ) и номер ячейки в данной матрице (код А ), причем младшие К разрядов физического адреса, поступающие на входы 1о 1 и являются но мером ячейки (А ) в матрице битов, а код А равен коду старших разрядов адреса. . . Распределитель 10 осуществляет перестановку битов информационного слова следующим образом: при подаче на его управляющие входы кода А он перегруппировывает биты информационного споеа в следующем порядке: бит с его i-ro входа направляется на ( Л)-ый выход. Например для Шестнадцатиразрядного блока перестановки битов при А 1110-информационное слово ( () перегруппирова но в слово ( 5 ЗтЭдасападалаи) i S fl y o Режим первый. Сигнал на управляющем входе 6 равен О. На адресные и информацио нные входы устройства соответственно поступают адрес и информационное слово. Поскольку сигнал на- входе 6 равен нулю, то адрес на адресные входы накопителей 7о-7п-Ч проходит без изменения. Распределитель ГО под воздействием кода А, поступившего на его управляющие входы 13 1 - 13)с (см. фиг. 2), настроится на перестановку битов в таком режиме, что бит на его i-ом информационном входе направлен на (i + А)-ый выход. По сигналу Чтение/запись, равному единице, слово с информационных входов 0 - - (см. фиг.1), пройдя через коммутатор 9 и распределитель 10, поступит на информационные входы накопителей 7о - будет записано в него, как это показано на фиг. 3. 92 86 Режим четвертый. Сигнал на управляющем входе 6 (см. фиг. 1) равен 1. Исходное состояние сигнала Чтение/ /запись на входах 2 и 3 нуль, что соответствует режиму чтения. На все адресные входы 1 Q - 1 (см.фиг.1) подается адрес считываемой ячейки. Элементы 8 НЕРАВНОЗНАЧНОСТЬ на своих выходах содержат код младших разрядов адреса А . , Следовательно, на адресные входы тервой и второй групп адресных входов накопителей Уд - 7n- поступит код (Л Z) , где Z -двоичный код позиции накопителя, На остальные адресные входы накопителей 7о 7n--i ОА А дтарших разрядов адреса пройдет без -изменения. Распределитель 10 в зависимости от кода А , на его управляющих входах 01 - 3 (см. фиг. 2) настроится на соответствующую перестановку битов считанного словауТО есть при подаче адреса .0 .. .000 О..001 А на информационных выходах накопителей 7о 7 п-( фиг. I) появится слово ( c,b,.. (см. , фиг. 3),на информационных выходах 5о (см. фиг. 1) устройства появится слово (Ь C(j ,.., У« Wq) (см. фиг. 3). Таким образом устрюйство может реализовать ряд новых алгоритмов как для научно-технологических так и информационно-логических задач, ислользуя принцип обработки информационных слов параллельно по словам и последовательно по разрядам. Технико-экономические преимущества предложенного устройства заключаются в повышении быстродействия и расширении области применения устройства за счет обеспечения считывания/ aпиcи параллельно по словам одноименных разрядов слов в смежных ячейках памяти за один цикл работы. Формула изобретения 1. Запоминающее устройство, содержащее одноразрядные накопители, параллельно соединенные.по соответствующим адресным и управляющий входам, м коммутатор, одни из входов которого подключены к информационным входам одноразрядных накопителей, управляющие входы коммутатора соединены с управляющими входами одноразрядных накопителей и являются одними из управлйющих входов устройства, а другие входы коммутатора являются инфор мационными входами устройства, от личающееся тем, что, с целью повышения быстродействия и расширения области применения устройства за счет обеспечения возможности считывания и записи одноименных разрядов групп смежных слов за один цик оно содеркит распределитель информационных сигналов и элементы НЕРАВНОЗНАЧНОСТЬ, одни из входов которых яв ляются одними из адресных входов уст ройства и соединены с управляющими входами распределителя информационных сигналов и адресными входами пер вой группы адресных входов одноразрядных накопителей, адресные входы второй группы адресных входов которых подключены к выходам элементов НЕРАВНОЗНАЧНОСТЬ, другие входы которых являются другими управляющими вх 9 дами устройства,адресные входы третьей группы Адресных входов одноразрядных накопителей являются другими адресными входами устройства, входы распределителя информационных сигналов подключены к выходам коммутатора, а выходы соединены с информационными входами одноразрядных накопителей и являются информационными выходами устройства. 2. Устройство по п. 1, о т л и мающееся тем, что распределитель информационных сигналов содержит коммутаторы, причем i-ый информационный вход j-ro коммутатора подключен к ()-«-j )-му входу распределителя (где 1 п и , а п-число на копителей) ,управляющие входы и выходы коммутаторов являются соответственно управляющими входами распределителя информационных сигналов. Источники информации, принятые во внимание при экспертизе 1.Электроника. 1973, N 7, с. 45 2.Авторское свидетельство СССР по заявке « 2863208/18-2, кл. Q 11 С 15/00, 03.01.80 (прототип),

Фиг.}

IW

№L

WmtKf/ mWf

Авторы

Даты

1982-05-15—Публикация

1980-05-22—Подача