So

So

У

СП СП Ю

Ю го

со

Изобретение относится к запоминающим устройствам и может быть испол1 %зовано для создания систем оператив ной памяти вычислительных устройств для решения информационно-логических задач.

Цель изобретения - повышение быстродействия и расширение области при- мененил за счет многоформатного доступа,

1

На фиг.1 приведена функциональная

схема устройства; на фиг„2 - функ- циональная схема распределителя информационных сигналов; на фиг.З - -byнкциональная схема преобразователя

АОДОВ.

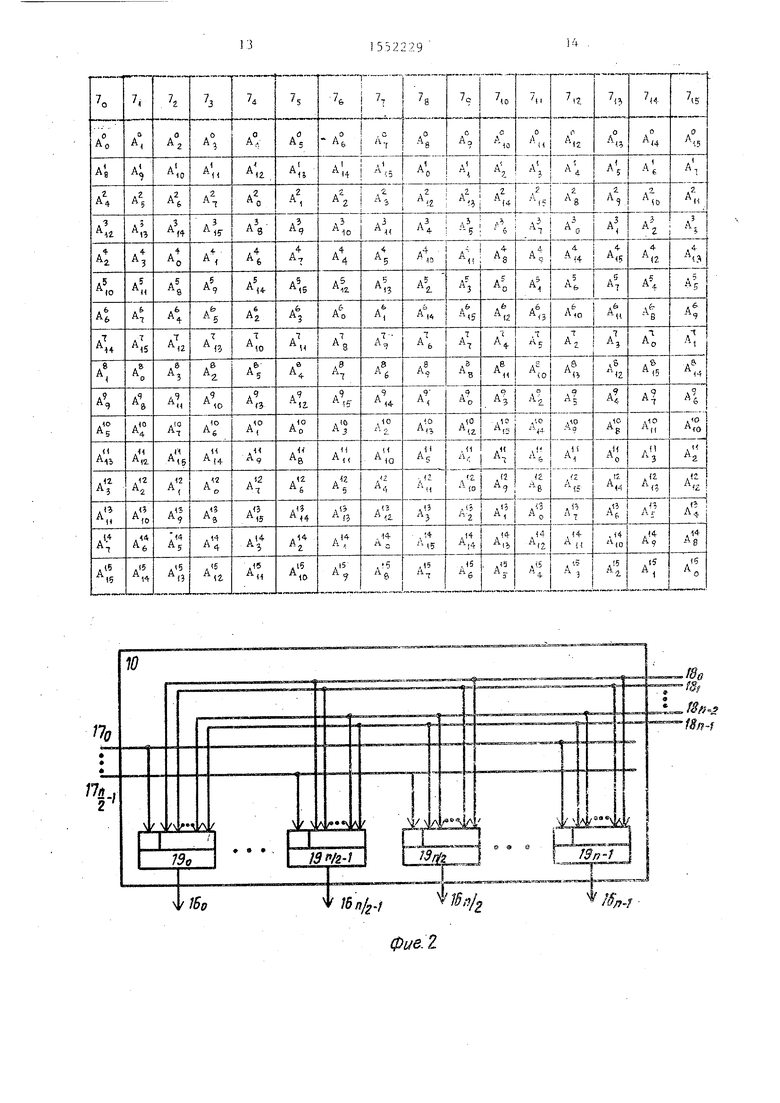

В таблице приведен пример записи информации в 16 одноразрядных накопителей одинаковой емкости I6 бит в

каждом.

На фиг.1 обозначены адресные входы 10 , 1(1К, для подачи

младших разрядов адреса (где k - число младших разрядов адреса), другие адресные входы 1, 1К+, ,..., lm предназначенные для подачи старших разрядов адреса (m+1 количество разрядов адреса), управляющие входы 2 и 3, информационные входы 4е,

4(, , ц-5 информационные выходы 50, ..., 5 „„., (п 2 ) и другие управляющие входы 60, 61, ,.., 6е, определяющие тип формата, где

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU928408A1 |

| Запоминающее устройство | 1987 |

|

SU1532976A1 |

| Ассоциативная запоминающая матрица | 1980 |

|

SU920841A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Оперативное запоминающее устройство | 1989 |

|

SU1705870A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Запоминающее устройство | 1980 |

|

SU920832A1 |

Изобретение относится к запоминающим устройствам и может быть использовано для создания систем оперативной памяти вычислительных устройств для решения информационно-логических задач. Цель изобретения - повышение быстродействия и раширение области применения за счет многоформатного доступа. Устройство содержит адресные 1, управляющие 2, 3, информационные 4 входы, информационные 5 выходы, управляющие входы 6, одноразрядные накопители 7, элементы НЕРАВНОЗНАЧНОСТЬ 8, распределитель 10 информационных сигналов, группу 11 управляющих коммутаторов, инверторы 12, преобразователь кодов 13, группу 14 адресных коммутаторов, операционный коммутатор 15. 1 з.п. ф-лы, 3 ил. 1 табл.

е Iog2(k+l)-l, если Iog2(k+l) - целое число; (k+l)J - если ) - не целое

Устройство содержит (фиг.1) одно™ разрядные накопители , . ..,7М,, , элементы НЕРАВНОЗНАЧНОСТЬ группы 8, коммутатор 9, распределитель 10 информационных сигналов, группу 11 управляющих коммутаторов, инверторы 12, преобразователь 13 кодов, группу 14 адресных коммутаторов и операционный коммутатор 15

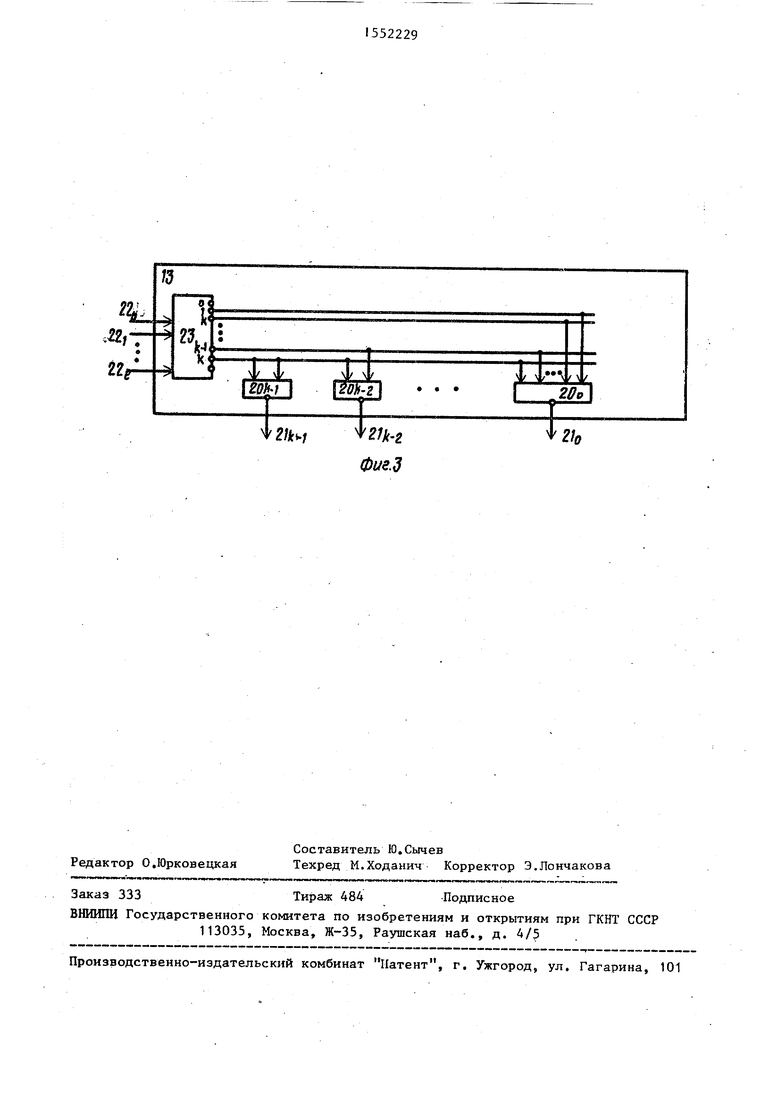

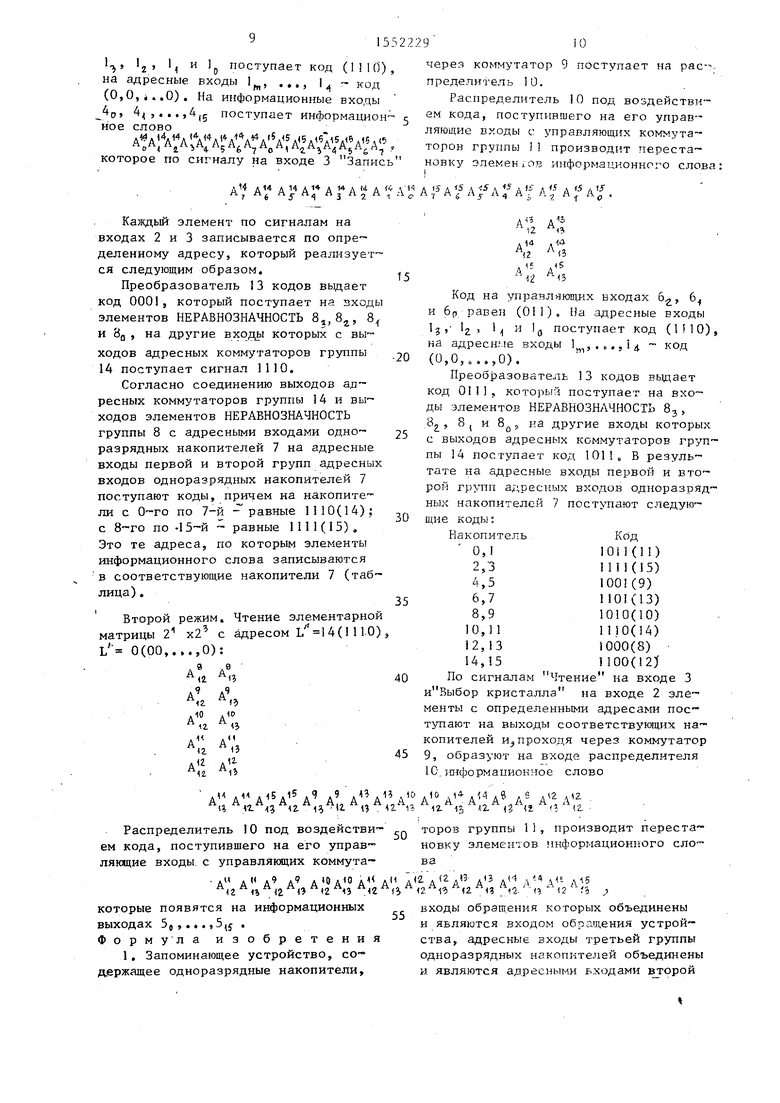

Распределитель 10 информационных сигналов (фиг,2) содержит выходы 16, . управляющие 17 и информационные 18 входы и коммутаторы 19. Преобразова- тель кодов (фиг.З) содержит элементы И-НЕ 20, выходы 21, входы 22 и дешифратор 23.

Приведенная таблица отражает фи зическое расположение информационных

СЛОВ AQ, А., . о « 5 A )f. , Ар, А , , а , А ,5, ...,А|,5, А1 , ;.,, в 16 одноразрядных накопителях 7С, Т4 ,,..,7& где в каждом накопителе показаны первые 16 ячеек, далее идет повторение с периодом в 16 ячеек.

Устройство работает следующим образом.

Возможны 2(k+l) режимов работы предложенного устройства: k+1 режи™ мов записи различных форматов входной информации и k+1 режимов чтения. Возможные форматы определяются значением k и представляются в виде эле ментарных матриц размерностью х2 элементов, где i принимает целые значения от 0 до k и различным

число.

Q

5

п

5

i соответствуют различные типы фор матов Режимы отличаются друг от друга лишь комбинациями управляющих сигналов на входах 3, определяющих, чтение или запись информации следует произвести, и на входах 60, 6f, ..., 6е определяющих тип формата. Поэтому для уяснения принципа работы устройства достаточно рассмотреть чтение, запись каких-либо двух форматов для конкретного k.

Входную инсЬормацию представляют в виде таблицы, в m-й строке которой расположено n-разрядное информационное слово А0, , ..., А, . Таким образом, столбцы таблицы составляют одноименные разряды слов. Представив эту таблицу как последовательность квадратных матриц размерностью п хп, можно рассмотреть расположение в запоминающем устройст ве лишь одной квадратной матрицы п х п с последующим периодическим повторением через п строк такого расположения для следующих квадрат- ных матрицо

Вводят координаты элемента (где элементом является определенный разряд,бит, определенного информационного слова) в квадратной матрице п х п; хг номер строки (слова); х - номер столбца (разряда), при этом 0 Ј: х{, х fe n-i . Для того, чтобы иметь возможность многоформат- ного доступа к фрагментам инйюрма-

ции в виде элементарных матриц раз-мерностью 2 х 2, состоящих из п элементов, за I цикл работы устройства с полным покрытием без пересечений исходной таблицы этими фрагментами определенного формата, коорцина ты элемента при расположении в за- Поминающем устройстве должны преобразовываться по следующему закону:

х Х1 ® °г

I

Х2 Х2.

где сг означает операцию двоичной

инверсии;

х номер ячейки накопителя; х номер накопителя, в которьн будет записан элемент (.бит) с координатами х , х « Элементы внутри элементарной мат™ рицы нумеруются слева на-право и сверху вниз„ Эпементарные матрицы внутри квадратной матрицы п х п нумеруются так же слева направо и сверif

ху вниз от 0 до 2 1 .Соответственно логический адрес элементарной ма .-рм- цы внутри таблицы указывается двумя кодами, определяющими номер квадратной матрицы п х п, в которой расиоло жена данная элементарная матрица (код I/ )s и номер элементарной матрицы в данной квадратной матрице (код L;/), причем младшие k разрядов физического адреса, поступающие на

входы 1Q, 1Ч, „.., 1К , и являются номером элементарной матрииы (I/) в квадратной матрице п х ns а код L равен коду старших разрядов адреса на входах к, ,.,, 1 устройства., Распределитель 10 осуществляет перестановку элементов (битов) эле A A «W « ,f 1 . Ч J4 . , i .(4 И AU

Ao A A2 AJ A4 AS A6 A7 A8 A, A1Q V( A,2 Af} A

15

A A A 5 A A A J A7 A A« С A1;, A J A A1

9

перестановка при чтении:

A A- A- A7 A A A J A A- A A A- .

i

При i , j j элементарная матрица выглядит следующим образом:

.14 (4, (4i

О 5 Т:

.5Г. (5.

А„А,АлА.

А ,4 А .4 А(

д1

L5 .(5

А А

Чосле нумерадич внутри элемент ар™ ной матриць: элементов слева направо и сяерху вниз получге ся следующая последовательность5 которая подается на распределитель информационных сигналов;

- А А « А« А« А;1 А« А1 А А | А( 4 А А Л , перестановке при записи:

А« .14- . 4 /1 1 ,1 . Л /,5 , 15 . 5 Л15 . --5 , 6

A, A fe А5 А , A j А2 А А0 А Ag А5 А а э А ,, , А0 .

ментарнои матрицы при записи или обратную перестановку при чтении. Пул подаче на его управляющие входы сода перстановкн, который получается в результате определенного преобразования над I, в зависимости от управляющих сигналов на входах 60, 6(5 . . &е, определяют тип формата,

- ° определяют значение i в записи х2 сигнал,, с. входа 3 определяющего чтение, запись. Таким образом, элемент (i r) на его jt й гыход (г,с на j-и накопитель) поступает

5 с (-L © J)TO входа при записи, где i означает опепаиию двоичной инверсии первых i старших разрядов, и злзпент (бит) на его выход пос упгет с (L 01 j)-ro (т.е, с

0 | о { о

(.L © j)ro накопителя) входа при чтении, где о i означает операцию двоичной инверсии первых i младших разрядов s

5 Например, для 16-разрядного блоха перестановки битов (элементов) где k-4 при L illO(lu), (7),

.5 i определяется i, для i 0„1

0 L ОП1(7), для 2 L 1011 (11).

л.

для i 3, L 1101(3), для i 4,

о .

1110(14).

Таким образом получаются следую- 5 цие перестакочки.

При х i

j j при записи:

i - 0, i.O, I ,2, ..., 15,

О

I/

7S L 7 перестановка

15

9 S

715522298

перестановке при чтении:

АМ АН д(4-А 4-д 4-д14 н 14- (6 «5 .15 (5 д(5 .15 .1 А0 А1 А2. AJ А4 А5 А& А7 АоА1 Аг Аэ А4 А5 А6 А7

При i 2, j 0,1,215,до д A1 A1

Г,0; 2 3 8 9 10 11 4 5 6 7 12 АД A AS ди

и,14,15 элементарная матрица выгля-А8 АЧ А« Ам

дит следующим образом:д 5 ,15 ,15

A12 A12 Au8 ° «

Я8 А9 Ац

После нумерации Аи А41 А А12- АП А° А1 А А1 А14 А14

Ад л, A,, Ag A, AJOAH A,2 Ag А, А,0АИ А9 АЮ АМ

перестановка при записи:

A A i А А , А « А- А, А« А« А« А« А А А« А.

перестановка при чтении:

,а .12 .г лч Aii . .1 и . . н .5 , s iff Ав А, А,0А4 А„ А, Ам А„ А% А, АЈА „ Ag A1, A| A J%

При i - 3,j 0,1,2,3,4,5,6,7,A /ZА Л

8,9,10,11,12,13,13,15 элементарнаяА ,|А4Л

матрицаА4|А4,}

А а А,АЈAJ

А9,г А „A;t

A7t A r После нумерации

t

Лв А8 Л9 А9 А4 ДИ АМ A1Z-A Z Л1 А Л1 Д А12 } А1 А12 2 « 2 1 U 4 О

перестановка при записи:

А А«г Ai Aiz А А«г А Aiz An Ai2 Ai An Ai перестановка при чтении:

А9 А8 А9 Л9 А М А« А11 А А л 1В

Аа Ai Au Au Au Ai А1г А А(г А А« А}г А f

4°

При i 4, j 0,8,4,12,2,10,6,

14,1,9,5,13,3,11,7,15 элементарная .

матрица

A°A

A,4A44

A1 После нумерации

лО A л2 д А А5 А6 А7 А6 А А А А1 Л А„ Ai4Af4AJ4Af4AM.A44A,4A44 АцАцА 4А14.А44А44 Ан перестановка при записи:

А А 5 А А1 А 5 AW А1 А9 А ЛИ Л2 Л1° Л A 1Z A° A9

АНА14-А«А14 A A 4AHAWA 4A 4 A 4AHA «A14Af4A 4

перестановка при чтении:

А UA(4A14A (4 A 4A14Af4AH A14A14 A1 A ( А14

Рассмотрим работу устройства в А О А А А А14 Af Af

двух режимах для k 4.55 1S 5 ,5 д15 д15 дГб

Первый режим. Запись элементар- о « г 3 4- 5 т ной матрицы 2 х2 с адресомКод на управляющих входах 6, 6

L 14(1110), L 0(000...0): и 6Л равен (001). На адресные входы

Ц 2 и 0 поступает код (II 10), на адресные входы lm, ..., ц - код

(0,0,,..0). На информационные входы .4о 4,,,..., 4 (6 поступает информацией- с ное слово

AtA 44A;44A;4A f45AfA A-.

которое по сигналу на входе 3 Запись

А1/ А А;4 А А А Л У А А 5

5

Каждый элемент по сигналам на входах 2 и 3 записывается по определенному адресу, который реализуется следующим образом.

Преобразователь 13 кодов выдает код 0001, который поступает на входы элементов НЕРАВНОЗНАЧНОСТЬ 8,,8г, 8., и 80 , на другие входы которых с выходов адресных коммутаторов группы 14 поступает сигнал 1110.

Согласно соединению выходов адресных коммутаторов группы 14 и выходов элементов НЕРАВНОЗНАЧНОСТЬ группы 8 с адресными входами одноразрядных накопителей 7 на адресные входы первой и второй групп адресных входов одноразрядных накопителей 7 поступают коды, причем на накопители с 0-го по 7-й - равные 1110(14); с 8-го по -15-й - равные 1111(15). Это те адреса, по которым элементы информационного слова записываются в соответствующие накопители 7 (таблица) .

Второй режим. Чтение элементарной матрицы 21 х23 с адресом (11 0) L1 - 0(000):

а в А

А;, А%

А%

А А

г

ъ

г

А ,1 А,

Ж, О А Х ХЛ

Распределитель 10 под воздействием кода, поступившего на его управ™ ляющие входы с управляющих коммута-

А. А А9. А9„ А $ A All А1; А А % А , А1,3, АЈ Л А« А %

15

2 которые появятся на информационных выходах 59 ,..., 5,j . Формула изобретения

55

А У

( П и 42 5

входы обращения которы и являются входом обра ства, адресные входы т одноразрядных накопите и являются адреиными г

4ю

через коммутатор 9 поступает на рас- предепитель 10.

Распределитель 10 под воздействием кода, поступившего на его управляющие входы с управляющих коммутаторов группы 1 производит перестановку элемент информационного слова;

5 5

А.

Afi At5 A A /

г

. 15 Ч

13 14 (3 (5 в

Код на управляющих ьходах 6, 6 6р равен (011). На адресные входы

1

и

поступает код (140),

0

41 J

I4 КОД

на адреснме входы (0,0,...,0).

Преобразователь 13 кодов рыдает код 0111. который поступает на входы элементов НЕРАВНОЗНАЧНОСТЬ 8,

5

- 2.

8, и

J3 на другие входы которых

0

5

0

5

с выходов адресных коммутаторов группы 4 поступает код 1011е В результате на адресные входы первой и второй групп адресных входов одноразрядных накопителей V поступают следующие кодЬ :

НакопитегьКод

0,11011(11)

2531111(15)

4,5100(9)

6,71101(13)

8,91010(10)

10,111110(14)

12,131000(8)

14,151100(12)

По сигналам Чтение на входе 3 и Выбор кристалла на входе 2 элементы с определенными адресами поступают на выходы соответствующих накопителей и проходя через коммутатор 9, образуют на входе распределителя 1C информациончое слово

И2 И2.

50

торов группы 11, производит переста новку элементов информационного слова

А % А , А1,3, АЈ Л А« А %

15

А У

( П и 42 5 ,)

входы обращения которых объединены и являются входом обращения устройства, адресные входы третьей группы одноразрядных накопителей объединены и являются адреиными гходами второй

группы устройства, коммутатор, инфор- мационные входы первой группы кото™ рого соединены с соответствующими выходами одноразрядных накопителей, информационные входы второй группы коммутатора являются информационными входами устройства, входы записи- чтения одноразрядных накопителей со единены с управляющим входом комму™ татора и являются входом записи чте ния устройства, распределитель инфор мационных сигналов, входы которого соединены с соответствующими выходами коммутатора, выходы распределителя информационных сигналов соедгнены с соответствующими информаиион11г1мр входами одноразрядных накопителей ч яв™ ляются информационными выходами устройства, о гличающееся

тем, что, с целью повышения быстро-™ действия и расширения области приме- нения устройства за счет многоформэт™ ного доступа, в него введены группа адресных коммутаторов, преобразова™ тель кодовf группа инверторов, операционный коммутатор s группа управ- ляющих коммутаторов и группа элемен- тов НЕРАВНОЗНАЧНОСТЬ, выходы которых соединены с адресными входами второй группы одноразрядных накопителей, информационные входы первой группы операционного коммутатора являются адресными входами первой гиуппы устройства, управляющий вход операцчюн™ ного коммутатора соединен с входом записи-чтения устройства, информационные входы группы адресных коммутаторов являются соответствующими адресными входами первой группы уст- ройства, выходы адресных коммутато™ ров соединены с адресными входами первой группы одноразрядныг накопи™

0

5 0 5 0

телейа входами первой группы элементов НЕРАВНОЗНАЧНОСТЬ группы, входы второй группы которых соединены с выходами преобразователя кодов, входы которого соединены с управляющими входами адресных и управляющих коммутаторов группы и являются входами группы задания режима устройства, выходы управляющих коммутаторов группы соединены с соответствующими входами группы распределителя информационных сигналов, выходы адресных коммутаторов группы соединены с информационными входами второй группы операционного коммутатора, выходь которого соединены с соответствующн- ми входами инверторов группы и с информационными входами первой группы управляющих коммутаторов группы, информационные ВХОДЫ ВТОРОЙ ГРУППЫ К07 торых соединены с входами инверторов группыо

2в Устройство по п.1, с т н и чающееся тем5 что распределитель информационных сигналов содержит две группы -коммутаторов, управляющие входы j-ro коммутатора первой группы (0 j . - 5 где k - количество младших разрядов адреса) соединены с управляющими входаки Г( l) коммутатора второй группы и являются управляющими входами распределителя,, i-й информационный вход распределителя соединен с i-м информационным входом коммутатора первой группы и с (2 -)-jl-M информационным входом коммутаторов второй группы (0 i 2k -)j выходы коммутаторов явпяются информа ционными выходами распределителя информационных сигналов,

t-«t

SI

z/aSl&

-/

i-frgi

°9t

| Электроника, 1973, № 7, с | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Запоминающее устройство | 1980 |

|

SU928408A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-03-23—Публикация

1987-12-03—Подача