(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО Изобретение относится к вычисли-тельной технике и может быть использовано при разработке однокристальных БИС ЗУ и построению на их базе систем оперативной «памяти различных устройств. Известно запоминающее устройство, представляющее собой линейный массив произвольно адресуемых ячеек, содержащее ряд одноразрядных блоков полупроводниковых ЗУ, параллельно соед ненных по адресам и управляющим шинам Г1. Наиболее близким к предлагаемому по технической сущности является запоминающее устройство, содержащее. одноразрядные блоки ЗУ, параллельно соединенные по адресньлм шинам |и управляющим шинам Чтение/Запись Выборка адреса столбца, Выборка а адреса строки, где информационное слово параллельно подается на информ ционные входы и считывается с информ ционных выходов блоков ЗУ. Применяем в данной системе памяти блоки ЗУ содержат J9eшифpaтopы адреса строки и столбца, матрицу запоминающих элемен тов., блок- усилителей считывания и ве тилей ввода-вывода, узел управления 21. . Подобные системы памяти исключают возможность параллельного чтения/записи за один цикл работы одноименных разрядов слов в смежных ячейках памяти, поскольку данные одноименных разрядов размещаются в одном блоке ЗУ. В ряде же задач матричной алгебры, а также в информационно-логических задачах, оперирующих таблицами, возникает такое требование. Цель изобретения - расширение функциональных возможностей системы памяти за счет обеспечения возможности записи и считывания одноименных разрядов группы слов. Указанная цель достигается тем, что в запоминающее устройство, содержащее блоки памяти, адресные и управлякщие входы которых являются соответственно адресными и управляющими входами устройства, введены коммутатор, одни входы которого подключены к выходам блоков памяти, а другие входы коммутатора являются информационными входами устройства, блок циклического сдвига, одни входы которого подключены к выходам коммутатора, а выходы - к информационным входам блоков памяти, и регистр, входы которого подключены к адресны.м

входам блоков памяти, а выходы - к другим входам блока циклического сдвига, управляющие входы коммутатор и блока циклического сдвига являются соответствующими управляющими входам устройства.

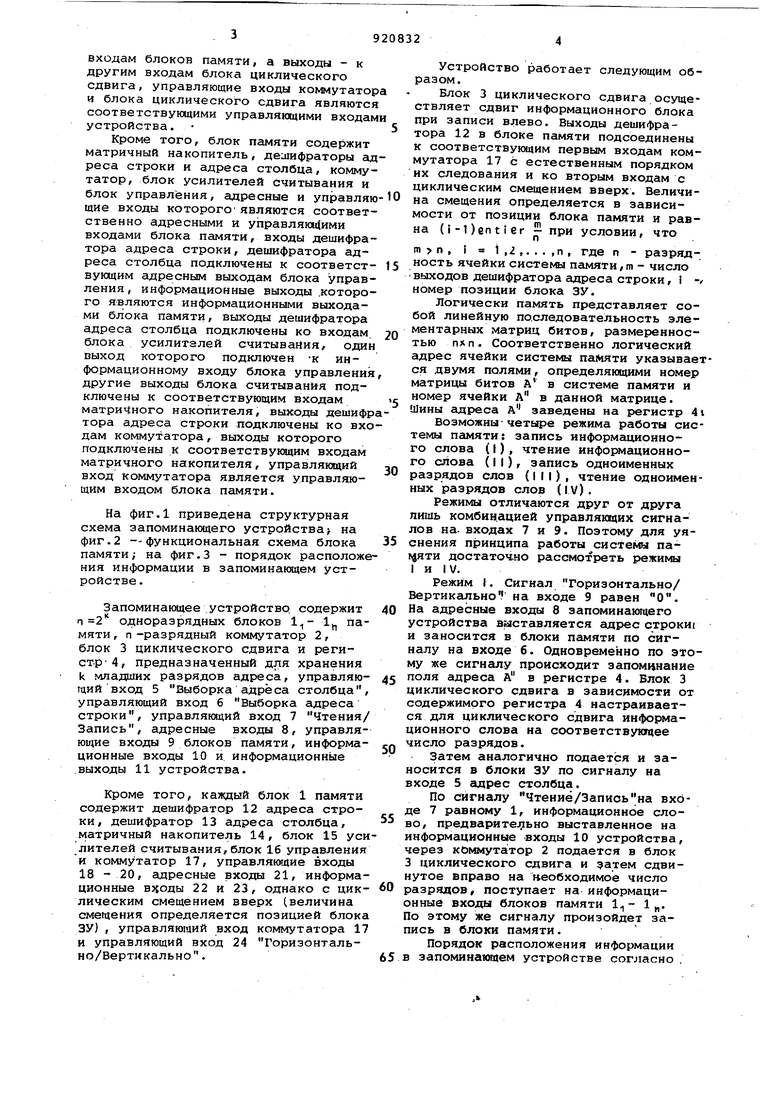

Кроме того, блок памяти содержит матричный накопитель, дешифраторы адреса строки и адреса столбца, коммутатор, блок усилителей считывания и блок управления, адресные и уп равляю щие входы которогоявляются соответственно адресными и управляюи|ими входами блока памяти, входы дешифратора адреса строки, дешифратора адреса столбца подключены к соответствующим адресным выходам блока управления, информационные выходы .которого являются информационными выходами блока памяти, выходы дешифратора адреса столбца подключены ко входам блока усилителей считывания, один выход которого подключен -к информационному входу блока управления другие выходы блока считывания подключены к соответствующим входам матричного накопителя, выходы дешифртора адреса строки подключены ко входам коммутатора, выходы которого подключены к соответствуклцим входам матричного накопителя, управляющий вход коммутатора является управляющим входом блока памяти.

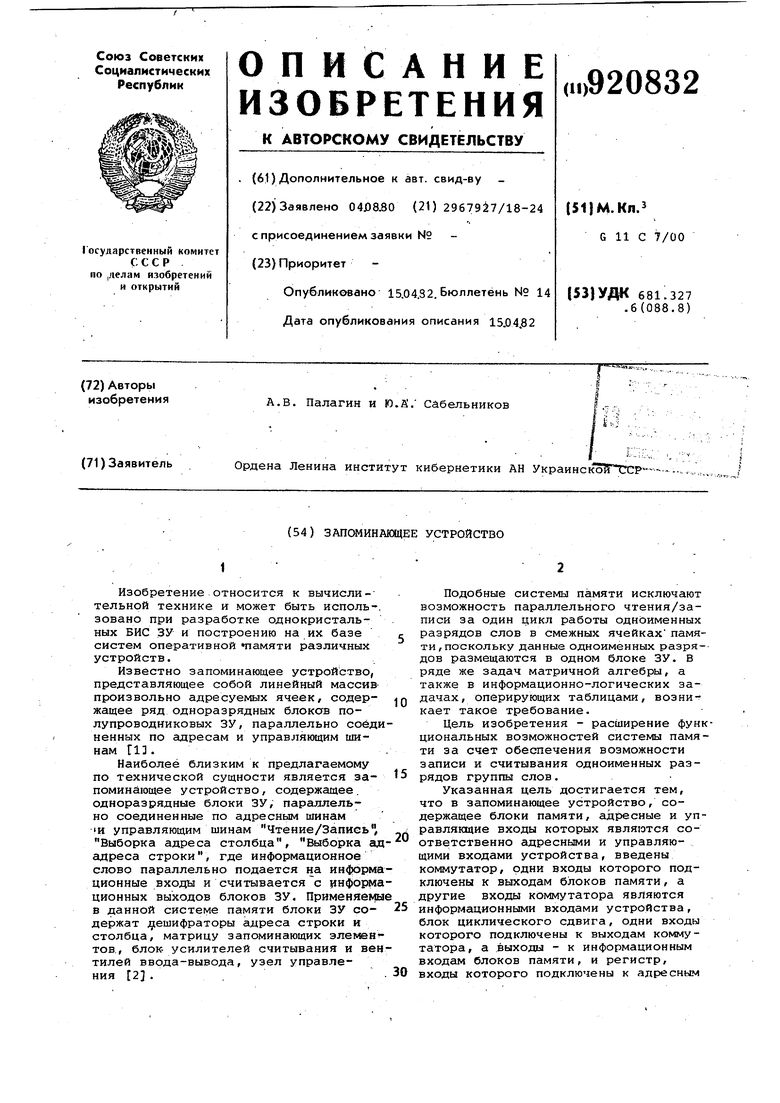

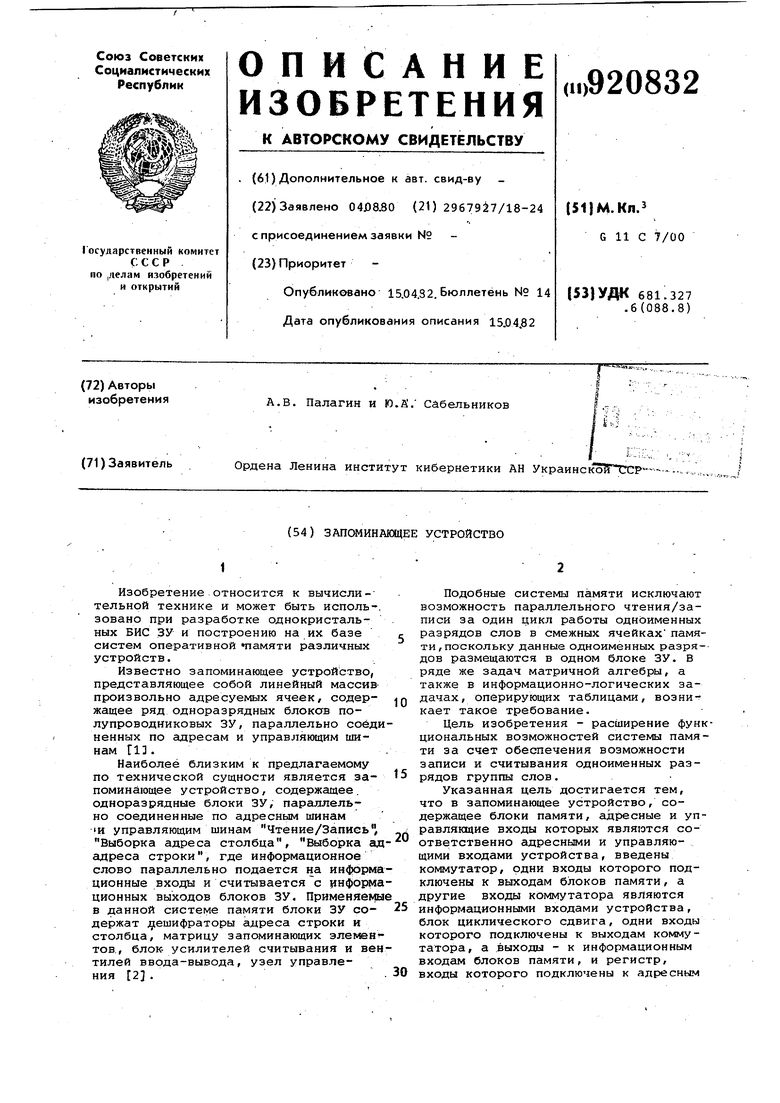

На фиг.1 приведена структурная схема запоминающего устройства на фиг.2 --функциональная схема блока памяти; на фиг.3 - порядок расположения информации в запоминающем устройстве.

Запоминакмцее устройство, содержит одноразрядных блоков 1 памяти , п-разрядный коммутатор 2, блок 3 циклического сдвига и регистр 4, предназначенный для хранения k младших разрядов адреса, управляюгций вход 5 Выборка адреса столбца, управляющий вход б Выборка адреса строки, управляющий вход 7 Чтения/ Запись, адресные входы 8, управляющие входы 9 блоков памяти, информационные входы 10 и. информационные .выходы 11 устройства.

Кроме того, каждый блок 1 памяти содержит дешифратор 12 адреса строки, дешифратор 13 адреса столбца, матричный накопитель 14, блок 15 усилителей считывания,блок 16 управления и коммутатор 17, управляющие входы 18 - 20, адресные входы 21, информационные В350ДЫ 22 и 23, однако с циклическим смещением вверх величина смещения определяется позицией блока ЗУ), управляющий вход коммутатора 17 и управляющий вход 24 Горизонтально/Вертикально.

Устройство работает следующим образом.

Блок 3 циклического сдвига осуществляет сдвиг информационного блока при записи влево. Выходы дешифратора 12 в блоке памяти подсоединены к соответствукхцим первым входам коммутатора 17 с естественным порядком их следования и ко вторым входам с циклическим смещением вверх. Величина смещения определяется в зависимости от позиции блока памяти и равна (i-l)entier - при условии, что

, i s i,2,...,n, где п - разрядность ячейки системы памяти,m - число выходов дешифратора адреса строки, I номер позиции блока ЗУ.

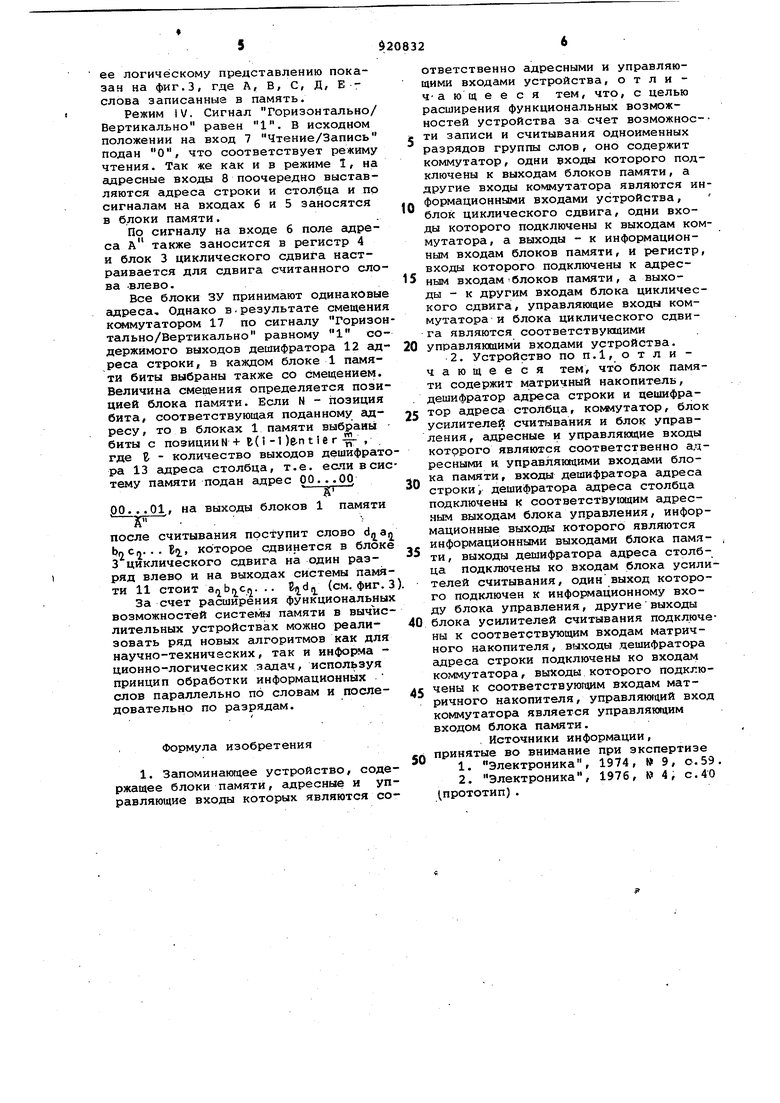

Логически память представляет собой линейную по.следовательность элементарных матриц битов, размеренностью пхп. Соответственно логический адрес ячейки системы памяти указываеся двумя полями, определяющими номер матрицы битов А в системе памяти и номер ячейки А в данной матрице. Шины адреса А заведены на регистр 4

Возможны четыре режима работы системы псмяти: запись информационного слова (I), чтение информационного слова (II), запись одноименных разрядов слов (1М), чтение одноименных разрядов слов (IV),

Режимы отличаются друг от друга лишь комбинацией управляющих сигналов на- входах 7 и 9. Поэтому для уяснения принципа работы системы достаточно рассмотреть режимы I и IV,

Режим (. Сигнал Горизонтально/ Вертиксшьно на входе 9 равен О. На адресные входы 8 запоминающего устройства выставляется адрес строки и заносится в блоки памяти по сигналу на входе 6. Одновременно по этому же сигналу происходит запоминание поля адреса А в регистре 4. Блок 3 циклического сдвига в зависимости от содержимого регистра 4 настраивается для циклического сдвига информационного слова на соответствующее число разрядов.

Затем аналогично подается и заносится в блоки ЗУ по сигналу на входе 5 сшрес столбца.

По сигналу Чтение/Запись на входе 7 равному 1, информационное слово, пред вари те/1ь но выставленное на информационные входы 10 устройства, через кОммута тор 2 подается в блок 3 циклического сдвига и затем сдвинутое вправо на необходимое число разрядов, поступает на информационные входы блоков памяти 1„. По этому же сигналу произойдет запись в блоки памяти.

Порядок расположения информации в запоминающем устройстве согласно . ее логическому представлению показан на фиг.З, где А, В, С, Д, Е слова записанные в память. Режим IV. Сигнал Горизонтально/ Вертикально равен 1. В исходном положении на вход 7 Чтение/Запись подан О, что соответствует режиму чтения. Так же как и в режиме I, на ёщресные входы 8 поочередно выставляются адреса строки и столбца и по сигналам на входах б и 5 заносятся в блоки памяти.. По сигналу на входе 6 поле адреса А также заносится в регистр 4 и блок 3 циклического сдвига настраивается для сдвига считанного слова -влево. Все блоки ЗУ принимают одинаковые адреса. Однако в.результате смещения ксялмутатором 17 по сигналу Горизон тально/Вертикально равному 1 содержимого выходов дешифратора 12 гщраса строки, в каждом блоке 1 памяти биты выбраны также со смещением. Величина смещения определяется позицией блока памяти. Если N - позиция бита, соответствующая поданному адресу, то в блоках 1 памяти выбраны биты с поэицииЫ + Е(1 -1 )еП t ie г , где V, - количество выходов дешифрато ра 13 сшреса столбца, т.е. есливсис тему памяти подан адрес 00...00 .Ор. . .01., на выходы блоков 1 памяти после считывания поступит слово bnCrt. .. BI, которое сдвинется в блоке 3 циклического сдвига на один разряд влево и на выходах системы памяти 11 стоит . .. (см. фиг. За счет расширения функциональных возможностей системы памяти в вычис лительных устройствах можно реализовать ряд новых алгоритмов как для научно-технических, так и информа ционно- логических задач, используя принцип обработки информационных слов параллельно по словам и последовательно по разрядам. Формула изобретения 1. Запоминающее устройство, соде ржащее блоки памяти, адресные и уп равляющие входы которых являются со ответственно адресными и управляющими входами устройства, о т л и ч-а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет возможноети записи и считывания одноименных разрядов группы слов, оно содержит коммутатор, одни входы которого подключены к выходам блоков памяти, а другие входы коммутатора являются информационными входами устройства, блок циклического сдвига, одни входы которого подключены к выходам коммутатора, а выходы - к информационным входам блоков памяти, и регистр, входы которого подключены к адресным входамблоков памяти, а выходы - к другим входам блока циклического сдвига, управляющие входы коммутатора- и блока циклического сдвига являются соответствующими управляющими входами устройства. 2. Устройство по п.1, о т л и чающееся тем, что блок памяти содержит матричный накопитель, дешифратор адреса строки и дешифратор адреса столбца, коммутатор, блок усилителей считывания и блок управления , сщресные и управляющие входы которого являются соответственно адресными и управляющими входами блока памяти, входы дешифратора адреса строки, дешифратора адреса столбца подключены к соответстйующим адресным выходам блока управления, информационные выходы которого являются информационными выходами блока памяти, выходы дешифратора адреса столбца подключены ко входам блока усилителей считывания, один выход которого подключен к информационному входу блока управления, другиевыходы блока усилителей считывания подключены к соответствующим входам матричного накопителя, выходы дешифратора адреса строки подключены ко входам коммутатора, выходы которого подключены к соответствуюпщм входам матричного накопителя, управляю1ций вход коммутатора является управляющим входом блока памяти. . Источники информации, принятые во внимание при экспертизе 1. Электроника, 1974, 9, о.59. 2. Электроника, 1976, 4, с.4О пpoтoтип).

w w

2D

21

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Запоминающее устройство | 1979 |

|

SU826418A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Полупроводниковое запоминающееуСТРОйСТВО | 1979 |

|

SU822290A1 |

| Запоминающее устройство с исправлением ошибок | 1980 |

|

SU955207A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Запоминающее устройство с диагональной адресацией | 1986 |

|

SU1399819A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1793475A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

Авторы

Даты

1982-04-15—Публикация

1980-08-04—Подача