йены с входами первого элемента ИЛИ, выход которого соединен с тактовым входом регистра входной информации, информационный вход которого, а также информационные входы первого и второго блоков выдачи адреса подключены к информационной шине ЦВМ, выход регистра входной информации соединен с первым информационным входом третьего коммутатора и первым входом команды блока управления, второй информационньй вход третьего коммутатора соединен с выходом кода состояния блока управления, выход третьего коммутатора соединен с параллельньм информационным входом преобразователя последовательного кода- в параллельный и обратно,- параллельный выход которого соединен,с информационным входом регистра выходной информации, выход которого соединен с вторым входом команды блока управления и первым информационным входом второго коммутатора, тактовьй вход регистра выходной информации соединен с выходом второго,элемента ИЛИ, входы которого соединены с выходами разрешения приема выходной информации блока управлен1-1я и блока прямого доступа в память, первьй и второй выхода1 разрешения вьщачи адреса которого coeд шeны с соответствутощими входами первого и второго блоков вьщачи адреса соответственно, входа выбора которых соединены с третьим и четвертым выходами дешифратора соответственно, выходы первого и второго блоков выдачи адреса соединены с вторым и третьим информационными выходами второго коммутатора, четвертый информационный вход которого соединен с выходом регистра состояния, вход которого соединен с информационным выходом блока управления, входы запроса на прерывание и запроса доступа в память блока прерываний и блока прямого доступа в память соответственно соединены с выходами соответствующих разрядов регистра состояния, вход режима прямого доступа в память блока прямого доступа в память соединен с выходом соответствующего разряда регистра режимов, вход триггера выбора канала соединен с выходом соответствующего разряда регистра режимов, прямой и инверсный выходы триггера выбора канала соединены с разрешающими входами первого и второго приемоперадатчиков, причем блок управления содержит дешифратор, коммутатор, счетчик, первый, второй и третий регистры, элемент И, элемент, задержки, причем первый второй и третий входы дешифратора являются соответственно входом режима передачи, входом разрешения приема и входом сопровождения входной информации блока управления, первый и второй информационные входы коммутатора соединены соответственно с первой и второй группами входов дешифратора и являются первым и вторым входами команды блока управления, четвертый вход дешифратора, счетный вход счетчика, тактовые входы второго и третьего регистров соединены между собой и являются входом конца преобразования блока управления, первый выход дешифратора соединен с входом элемента задержки, выход которого соединен с тактовым входом первого регистра и первым входом элемента И, второй вход которого соединен с вторым выходом дешифратора, а выход элементаИ соединен с входом записи счетчика, информационньй вход которого соединен с выходом коммутатора, третий информационный вход которого соединен с первой группой выходов дешифратора, выход счетчика соединен с пятым входом дешифратора., вторая группа выходов дешифратора соединена с информационным входом первого регистра, выход которого соединен с информационньм входом второго регистра, первьй и второй выходы которого являются выходом разрешения передачи, выходом начала преобразования блока управления, третий выход соединен с шестым входом дешифратора, группа выходов второго регистра является информационным выходом блока управления, третья группа выходов дешифратора соединена с информационным входом третьего регистра, первый второй выходы которого являются выходами разрешения приема входной информации и выходной ийформации блока соответственно, группа выходов третьего регистра является, выходом

кода состояния блока, причем блок прямого доступа в память содержит регистр запросов, .первый и второй элементы И, элемент ИЛИ, дешифратор, в-ход регистра запросов является входом запросов прямого доступа в памят

блока, выходы регистра соединены с группой входов дешифратора и с входами элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, второй вход первого элемента И соединен с выходом первого триггера, а выход первого элемента И соединен с установочны входом второго триггера, сбросовый вход которого соединен с первым выходом дешифратора, а инверсный выход второго триггера соединен с первьм входом дешифратора и сбросовым входом первого триггера, установочный йход которого соединен с вторым входом дешифратора и является входом разрешения прямого доступа в память блока, первый, второй, третий и четвертый выходы дешифратора являются первьм и вторым выходами разрешения выдачи адреса блока и выходами приема входной информации и вькодной информации блока, второй вход второго элемента И является входом режима прямого доступа в память блока,а выход второго элемента И, единичный

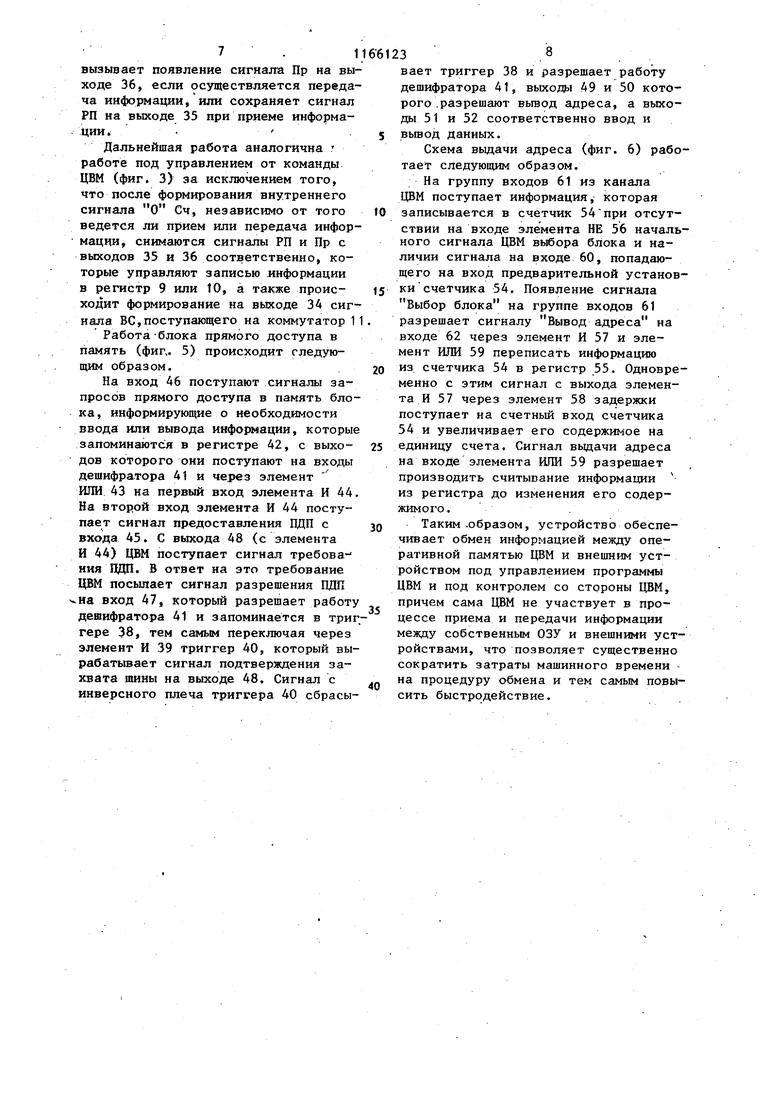

выход второго триггера и шесто й выход дешифратора образуют выход требования прямого доступа в память блока, причем блок выдачи адреса содержит счетчик, элемент НЕ, первый и второй элементы И, элемент ИЛИ, элемент задержки, регистр, первый вход первого элемента И и вход элемента НЕ образуют вход выбора блока, второйвход первого элемента И соединен с выходом элемента НЕ, а выход первого элемента И соединен с входом ;записи счетчика, информационный вход которого является информационным входом блока, счетный вход счетчика соединен с выходом элемента задержки, выход счетчика соединен с информационным входом регистра, выход которого является выходом блока, а тактовый вход регистра соединен с выходом элемента. ИЛИ, первьй вход которого соединен с входом элемента задержки и выходом второго элемента И, первый вход которого и второй вход элемента ИЛИ образуют вход вьщачи адреса, а второй вход второго элемента И соединен с входом выбора блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Устройство для восстановления информации при сбоях в блоках ЦВМ | 1983 |

|

SU1124314A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ЛИНИЯМИ СВЯЗИ, содержащее дешифра- s тор, регистр режимов, блок прерываНИИ, блок управления, первый и второй коммутаторы, первый, второй блоки приемопередатчиков, преобразог ватель последовательного кода в параллельный и обратно, причем информационный вход регистра режимов и выход первого коммутатора подключены к выходной и входной информационным шинам ЦВМ, вход дешифраторд соединен с адресной шиной ЦВМ, выход запроса на прерывание блока прерьшаний и выход сопровождения выходной информации блока управления соединены с одноименньми входными шинами ЦВМ, вход ответа на прерывание блока пр рьгоаний и вход сопровождения входной информации соединены с выходными одноименными шинами ЦВМ, шинные входы и вькоды первого и второго блоков приемопередатчиков подключены к первой, и второй линиям связи, информационнью входы первого и второго блоков приемопередатчиков соединены с последовательным выходом преобразователя последовательного кода в параллельньй и обратно, информационные выходы первого и второго блоков приемопередатчиков соединены соответственно с первым и вторым входами первого коммутатора, выход которого соединен с последовательным входом преобразователя последовательного кода в параллельный и обратно, вход разрешения преобразования и выход конца преобразования которого соединены с соответствующими выходом и входом блока управления, первый и второй выходы дешифратора соединены соответственно с входами разрешения. . приема регистра режимов и блока управления, управляющий вход второго (Л коммутатора соединен с выходом разрешения передачи блока управления, вход режима передачи блока управления соединен с выходом соответствуюлцего разряда регистра режимов, вход разрешения прерывания блока прерьтаний соединен с выходом Соответствующего разряда регистра режимов, о т -г личающее ся тем, что, с целью повьшения быстродействия, в него введены блок прямого доступа в паМять, первый и второй блоки вьщачиадреса, регистр состояния, регистр входной информации, регистр выходной информации, третий коммутатор, триггер выбора канала, первый и второй элементы ИЛИ, причем выход требования прямого доступа в память и вход разрешения прямого доступа в память блока прямого доступа в память подключены к одноименным входу и выходу ЦВМ, выходы разрешения приема входной информации блока прямого доступа в память и блока управления соеди-.

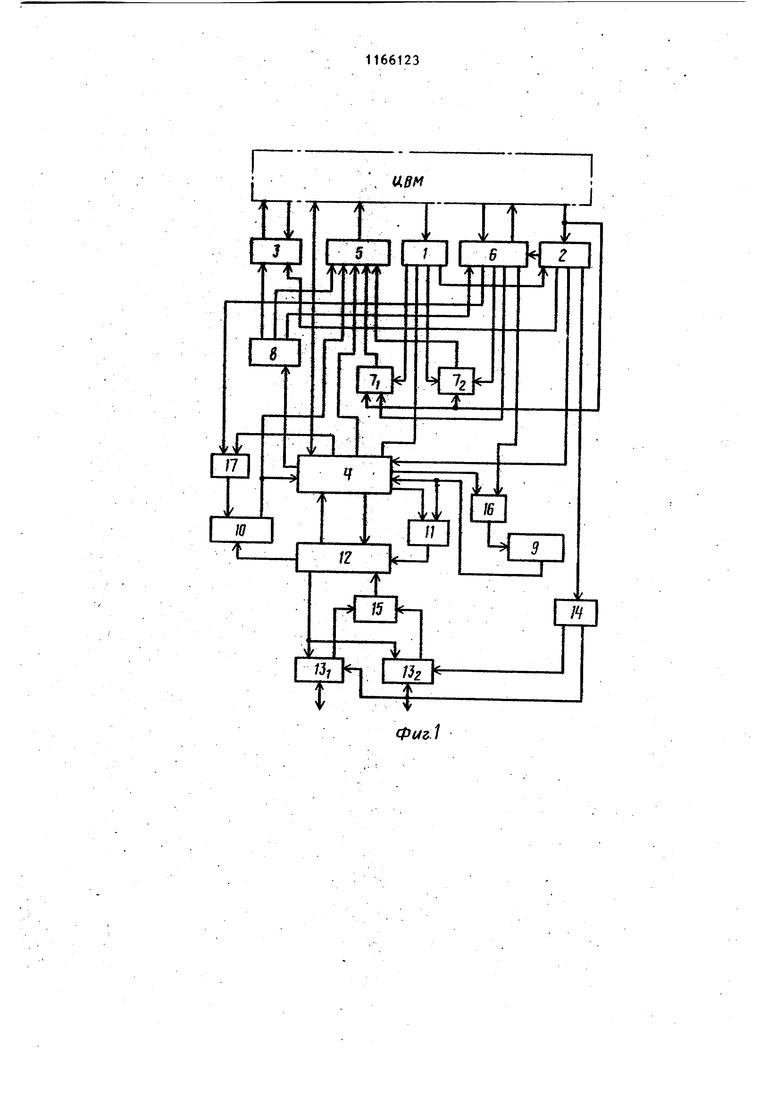

Изобретение относится к вычислительной технике и может быть использовано для сопряжения вычислительных машин с интерфейсами типа общая шина с последовательными линиями связи, например Манчестер-П, объединя щими ЦВМ и абонентов в информационно-измерительные и автоматизированные системы управления. Цель изобретения - повьшгение быстродействия устройства. На фиг. 1 - представлена блоксхема устройства; на фиг. 2 - функциональная схема блока управления; на фиг. 3 и 4 - временные диаграммы блока управления; на фиг. 5 - функциональная схема блока прямого доступа в память; на фиг. 6 - функциональная схема блока вьщачи адреса. Устройство содержит дешифратор t регистр 2 режимов, предназначенный для хранения сигналов, определяющих режим работы устройства, блок 3 прерываний, осуществляющий вьщачу сигналов запроса прерываний в ЦВМ и передачу векторов прерьшания, блок 4 управления, управляющий oпepaциkми обмена информацией между ЦВМ и линией связи под управлением команды, полученной в ЦВМ, или от линии связи, коммутатор 5, осуществляющий коммутацию информации, поступающей от различных источников под управлением сигналов от блока управления обменом информации, блок 6 прямого доступа в память, осуществляющий пРием из ЦВМ и выдачу в ЦВМ сигналов,обеспечивающих работу устройства в ОЗУ ЦВМ без участия центрального процессора,блоки 7, и 7 выдачи адреса,осуще.ствляющие хранение адресов ячеек ОЗУ, с которыми будет производиться обмен информацией и автоматическое изменение адресов при каждом цикле обмена, регистр 8 состояния, предназначенный для хранения результатов действий, выполненных устройством, регистр 9

входной информации, предназначенный для временного хранения команды и информации, передаваемой в линию свя зи, регистр 10 входной информации, служащий для временного хранения при нятой информации и команды, коммутатор 11, осуществляющий передачу информации на вход преобразователя информации, преобразователь 12 последовательного кода в параллельный и оёратно, служащий для преобразования последовательного кода в параллельный при приеме информации и преобразования параллельного кода в последовательный при выдаче информации устройством, блоки 13 и 13 приемопередатчиков , осуществляющие прием передачу информации и согласование уровней сигналов между устройством и линией связи, триггер 14 выбора канала, обеспечивающий выбор рабочего канала, коммутатор 15, обеспечивающий подключение нужного приемника к последовательному входу преобразовательного кода в параллельньй и обратно, элементы ИЛИ 16 и 17.

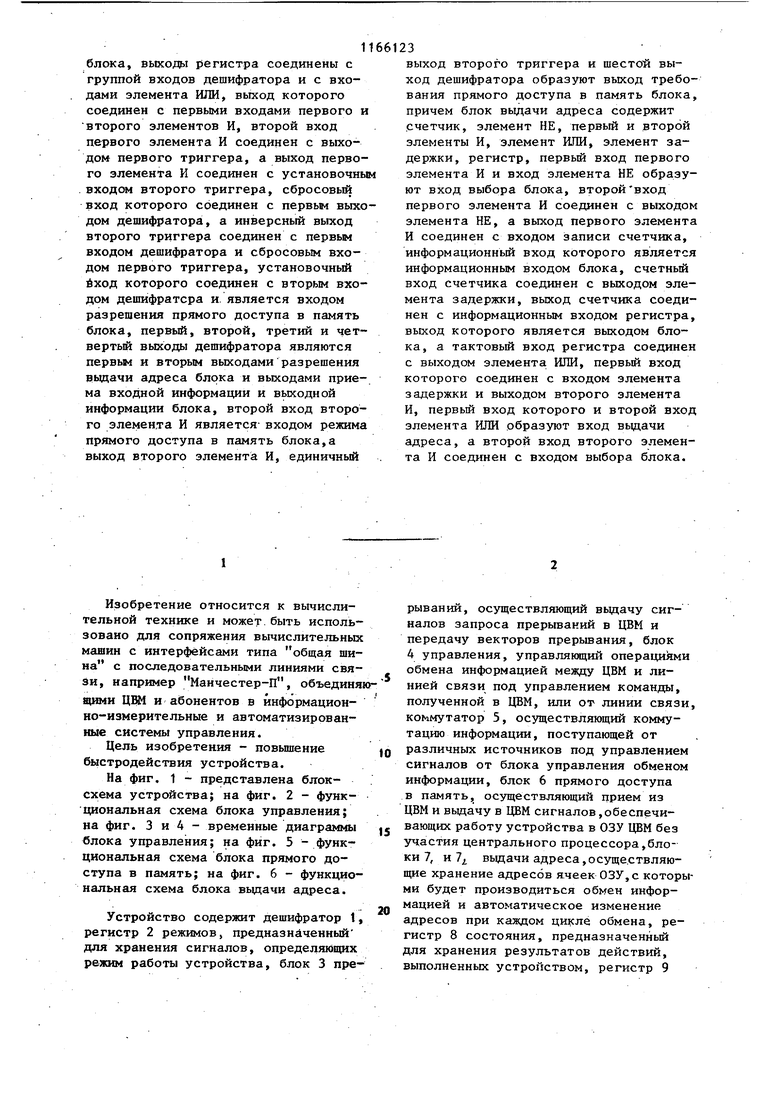

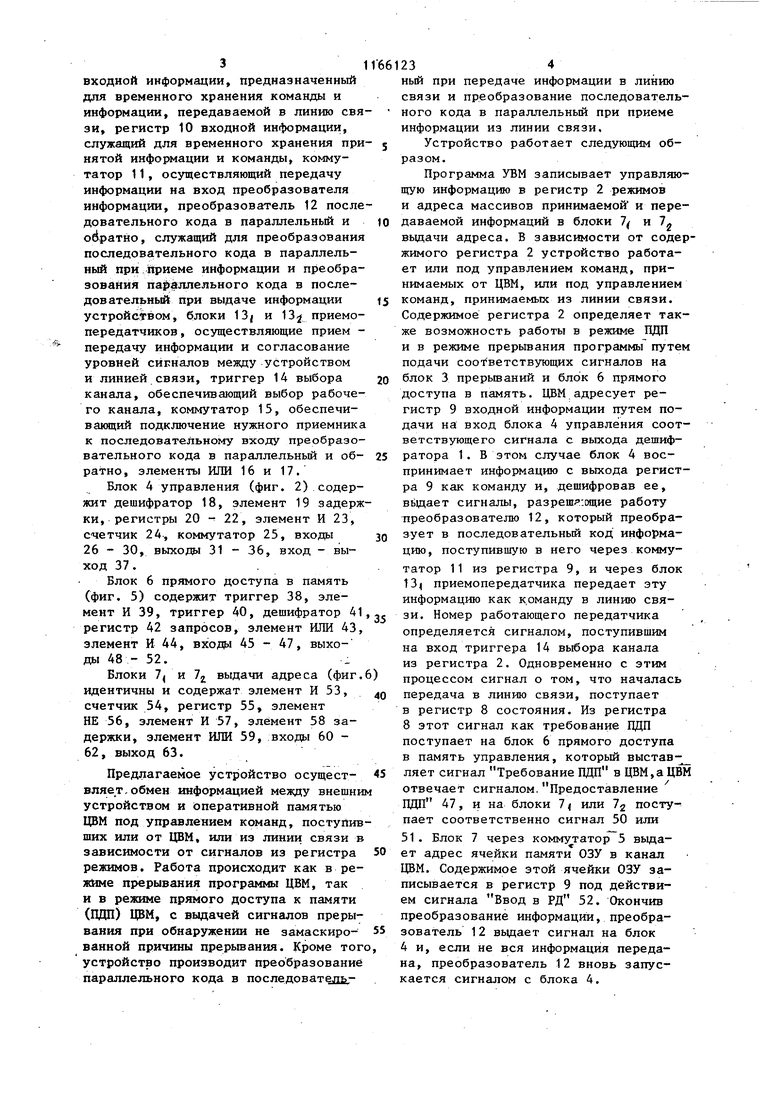

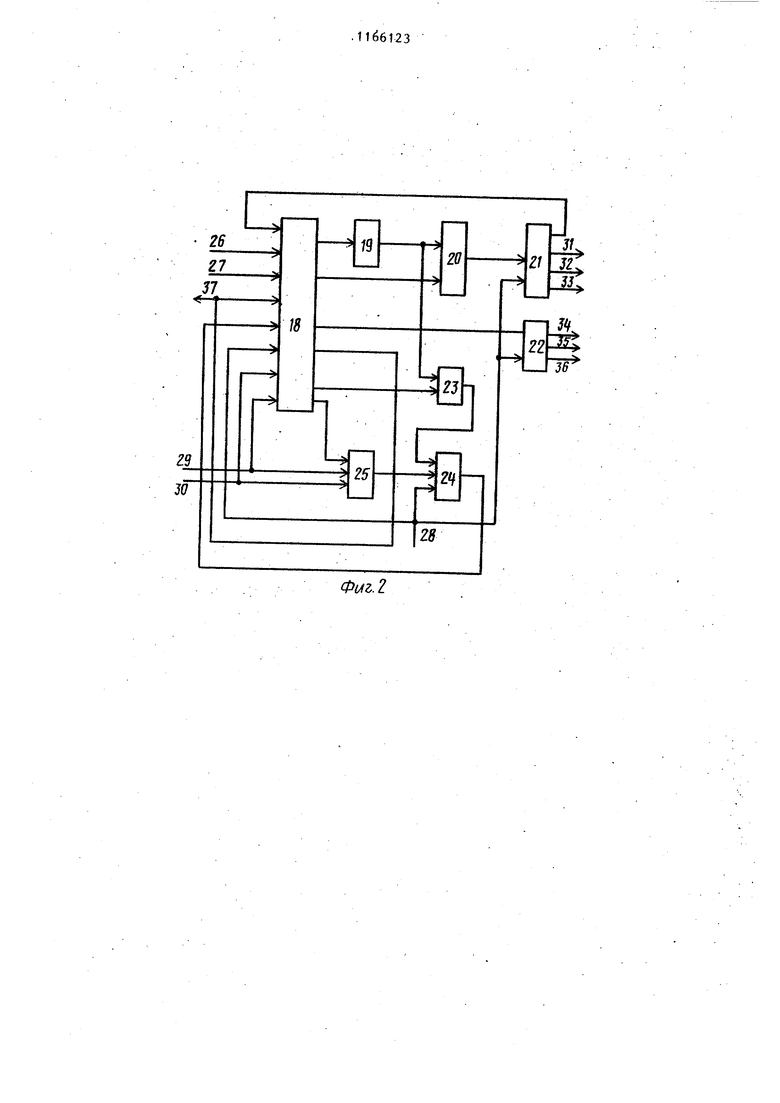

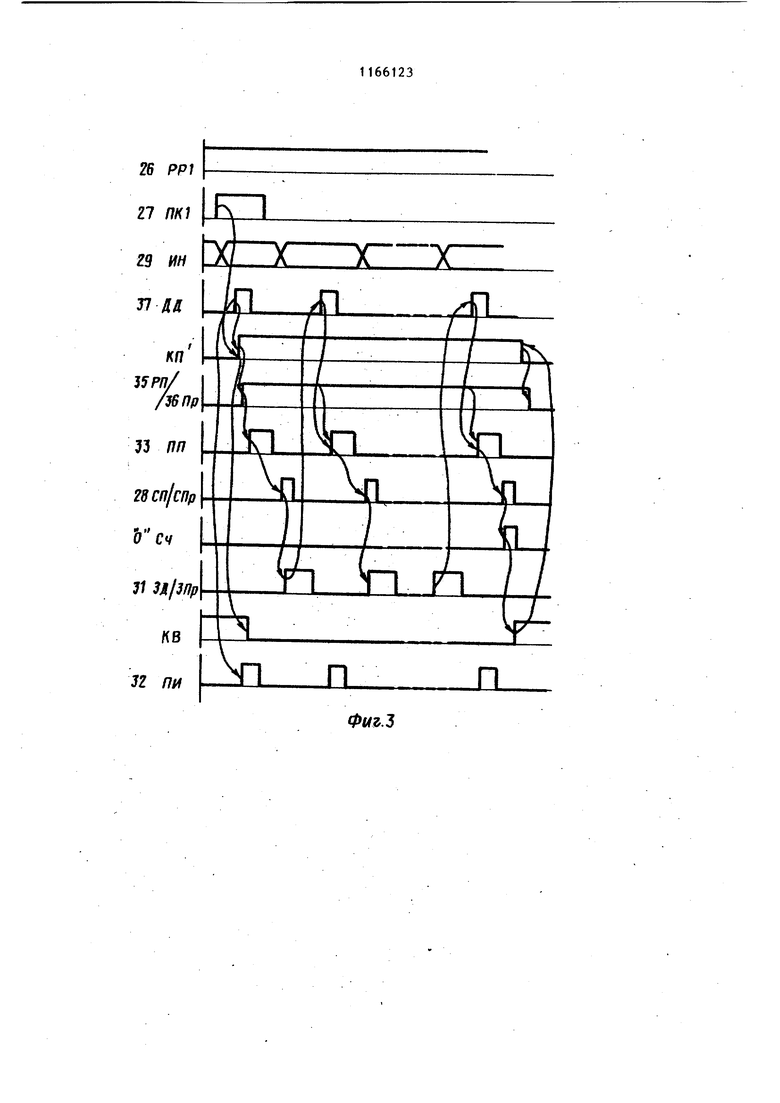

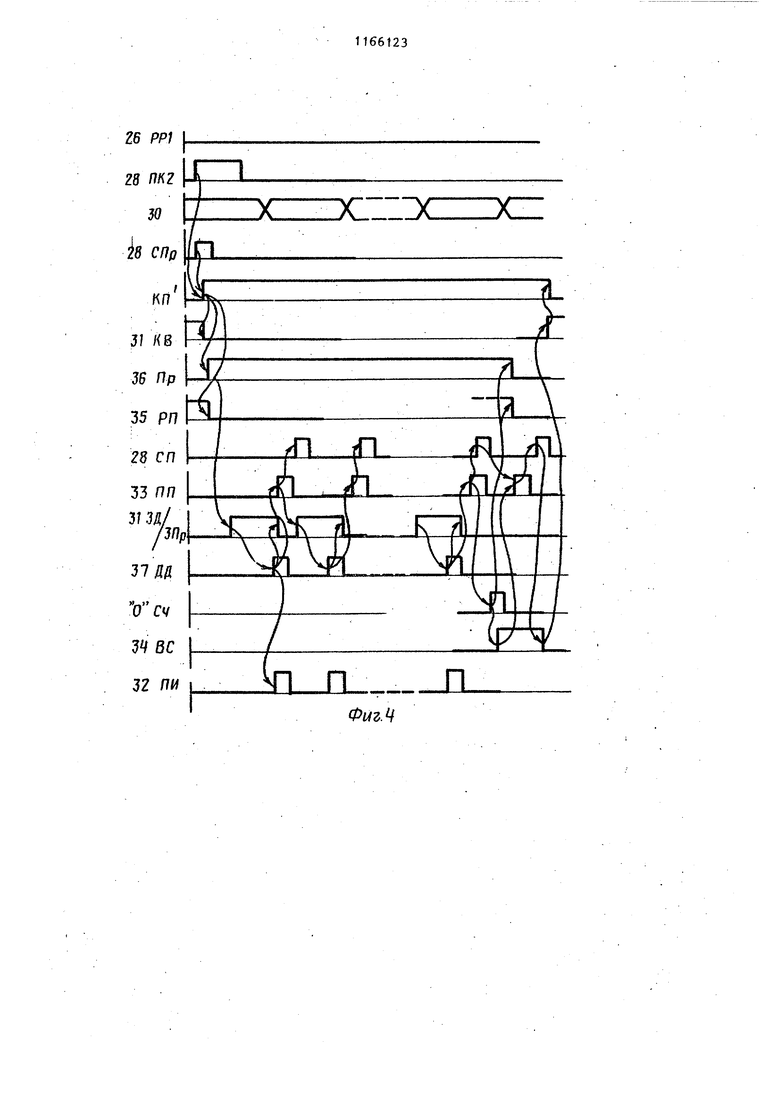

Блок 4 управления (фиг. 2) содержит дешифратор 18, элемент 19 задержки, регистры 20 - 22, элемент И 23, счетчик 24, коммутатор 25, входы 26 - 30, выходы 31 - 36, вход - выход 37..

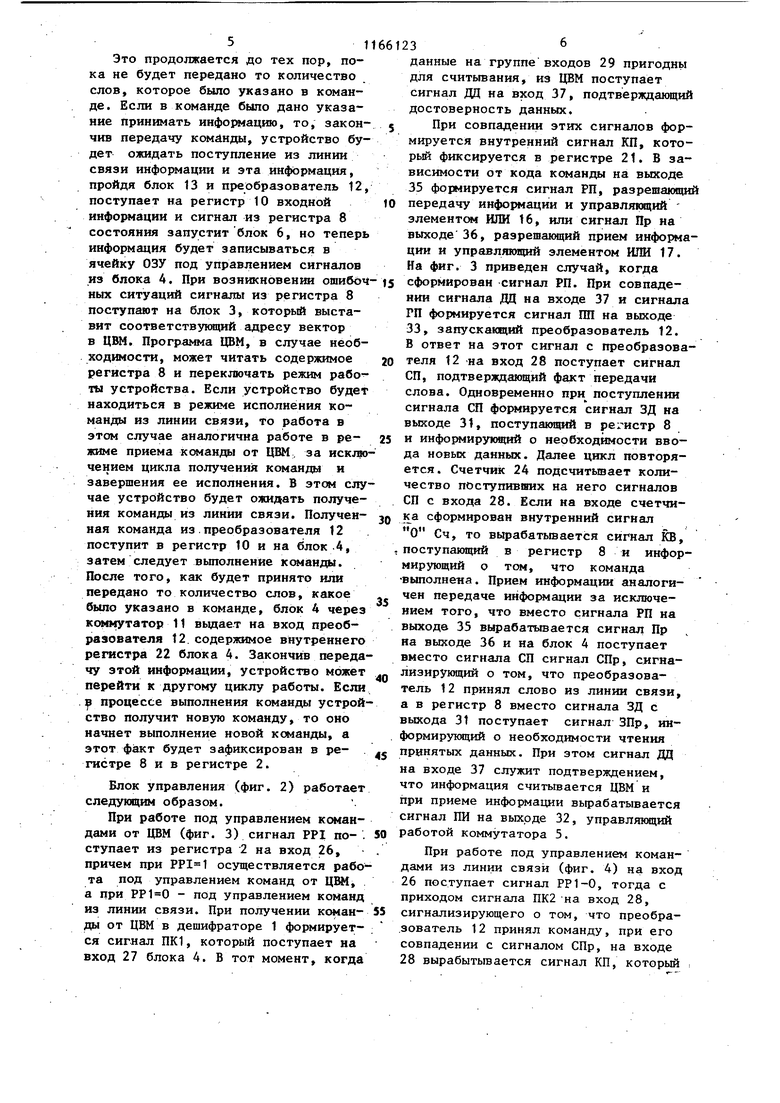

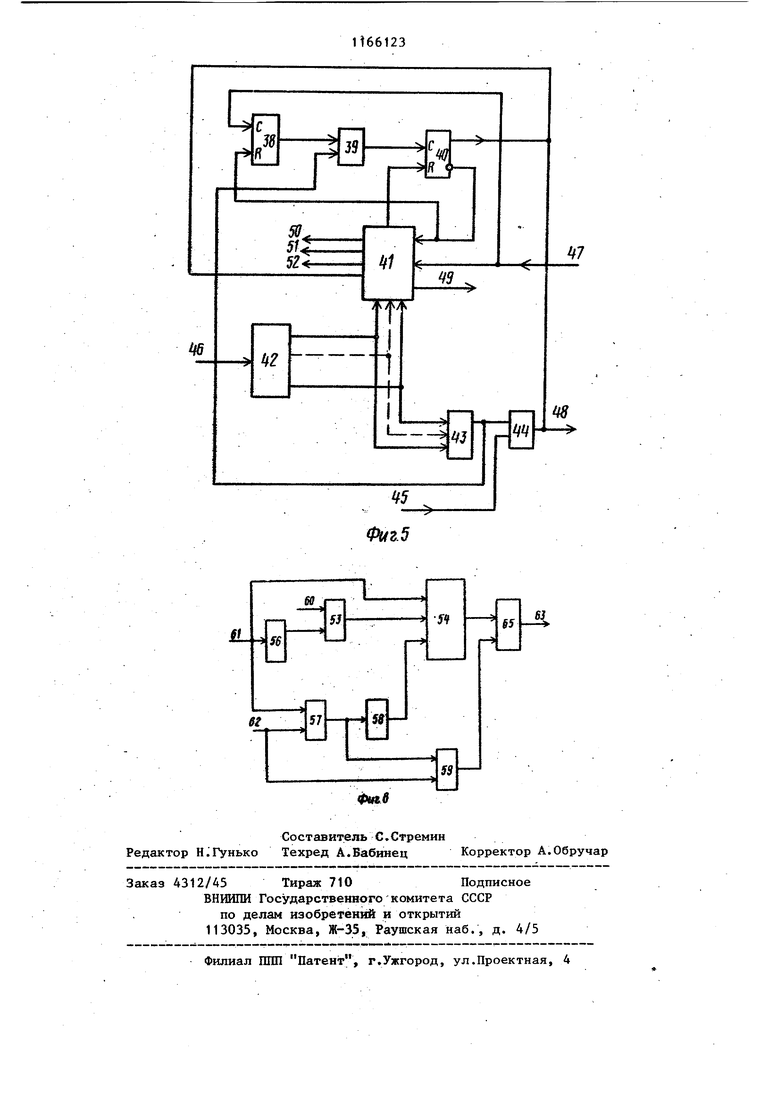

Блок 6 прямого доступа в память (фиг. 5) содержит триггер 38, элемент И 39, триггер 40, дешифратор 41 регистр 42 запросов, элемент ШШ 43, элемент И 44, входы 45 - 47, выходы 48-52.

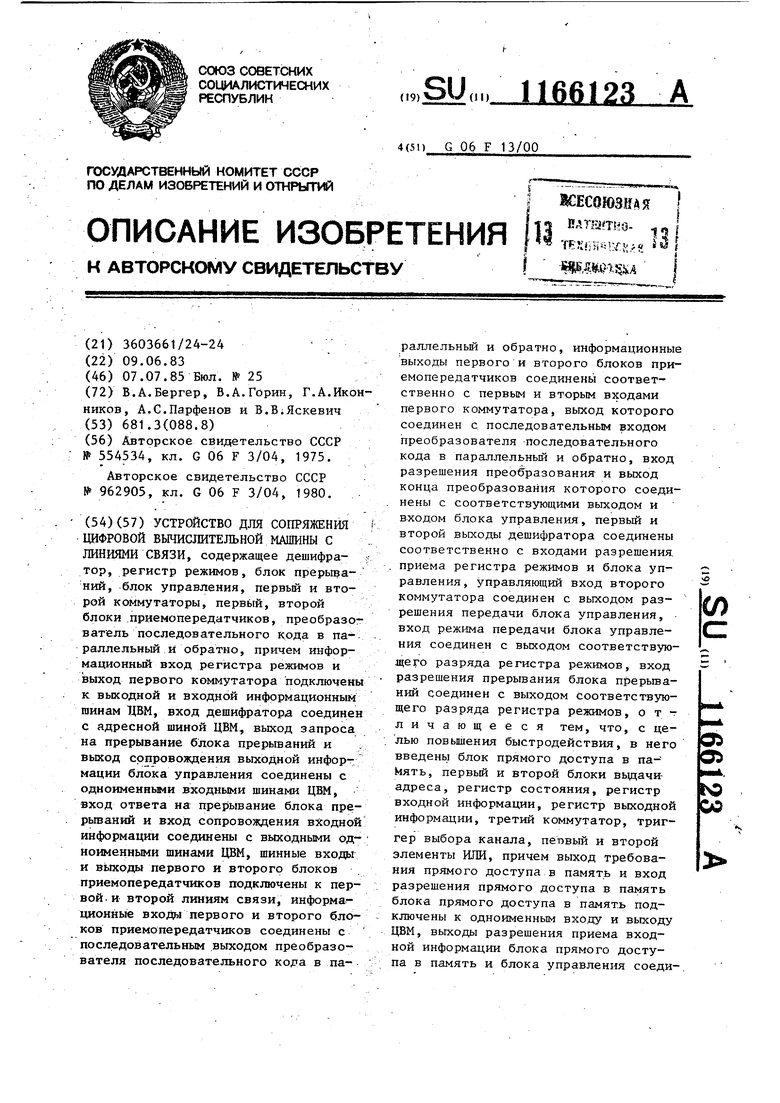

Блоки 7 и 7j. выдачи адреса (фиг. идентичны и содержат элемент И 53, счетчик 54, регистр 55, элемент НЕ 56, элемент И 57, элемент 58 задержки, элемент ИЛИ 59, входы 60 62, выход 63.

Предлагаемое устройство осуществляет,обмен информацией между внешни устройством и Оперативной памятью ЦВМ под управлением команд, поступивших или от ЦВМ, или из линии связи в зависимости от сигналов из регистра режимов. Работа происходит как в режиме прерывания программы ЦВМ, так и в режиме прямого доступа к памяти (ПДП) ЦВМ, с выдачей сигналов прерывания при обнаружении не замаскированной причины прерьюания. Кроме тог устройство производит преобразование параллельного кода в последовательный при передаче информации в линию связи и преобразование последовательного кода в параллельный при приеме информации из линии связи.

Устройство работает следующим образом.

Программа УВМ записывает управляющую информацию в регистр 2 режимов и адреса массивов принимаемой и передаваемой информации в блоки 7 и 7 выдачи адреса. В зависимости от содежимого регистра 2 устройство работает или под управлением команд, принимаемых от ЦВМ, или под управлением команд, принимаемых из линии связи. Содержимое регистра 2 определяет также возможность работы в режиме ПДП и в режиме прерьшания программы путе подачи соответствующих сигналов на блок 3 прерьгоаний и блок 6 прямого доступа в память. ЦВМ адресует регистр 9 входной информации путем подачи на вход блока 4 управления соответствующего сигнала с выхода дешифратора 1. В этом случае блок 4 воспринимает информацию с выхода регистра 9 как команду и, дешифровав ее, вйщает сигналы, разреш;:с1щие работу преобразователю 12, который преобразует в последовательный код информацию, поступившую в него через коммутатор 11 из регистра 9, и через блок 13 приемопередатчика передает эту информацию как к.оманду в линию связи. Номер работающего передатчика определяется сигналом, поступившим на вход триггера 14 выбора канала из регистра 2. Одновременно с этим процессом сигнал о том, что началась передача в линию связи, поступает в регистр 8 состояния. Из регистра 8 этот сигнал как требование ДЦП поступает на блок 6 прямого доступа в память управления, которьй выставляет сигнал Требование ДЦП в ЦВМ,а ЦВ отвечает сигналом,Предоставление ДЦП 47, и на блоки 7 или 1 поступает соответственно сигнал 50 или

26

Z7

57

J8

гэ

JL

20

21

l

22

J6

и,

L

Ztt

Ф(1.2

26 РР1

Фыъ.З

Ф1лгМ

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1983-06-09—Подача