(5) МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1274148A1 |

| Многофункциональный модуль | 1980 |

|

SU890557A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064471A1 |

| Универсальный логический модуль | 1984 |

|

SU1213537A1 |

| Многофункциональный логический элемент | 1980 |

|

SU898618A1 |

| Многофункциональный логический элемент на МДП-транзисторах | 1982 |

|

SU1064470A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| Многофункциональный элемент для логической матрицы | 1982 |

|

SU1037344A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

| Многовходовый логический модуль | 1990 |

|

SU1793547A1 |

I

Изобретение )тносится к вычислит тельной технике и предназначено для выполнения различных логических функ-, ций двух переменных, а также для выполнения операции арифметического сложения комбинаций прямых и инверсных значений двух переменных.

Известно устройство, выполненное на элементах И-ИЛИ-Н€, осуществляющее операцию арифметического сложения . ,

Недостатком известного устройства является то, что в нем осуществляется операция арифметического сложения только прямых значений двух переменных.

По основному авт.св. К 686lt6 известен многофункциональный логический элемент на МОП-транзисторах, содержащий три элемента равнозначности, в каждом из которых между шинами питания включен последовательно нагрузочный транзистор и

параллельные ветви из последователь

но. включенных переключателя и второго нагрузочного транзистора, в каждой ветви затвор переключающего транзистора подключен к истоку переключающего транзистора другой ветви, и один элемент И, образованный последовательно включенными между шинами питания нагрузочным транзистором и двумя переключающими транзисторами, причем в первом и во втором элементе равнозначности один вход подключен к соответствующей информационной шине, а второй - к соответствующей управляющей шине, выходы этих элементов через элемент И подключены к входу третьего элемента равнозначности,другой вход которого подключен к третьей управляющей шине 2.1.

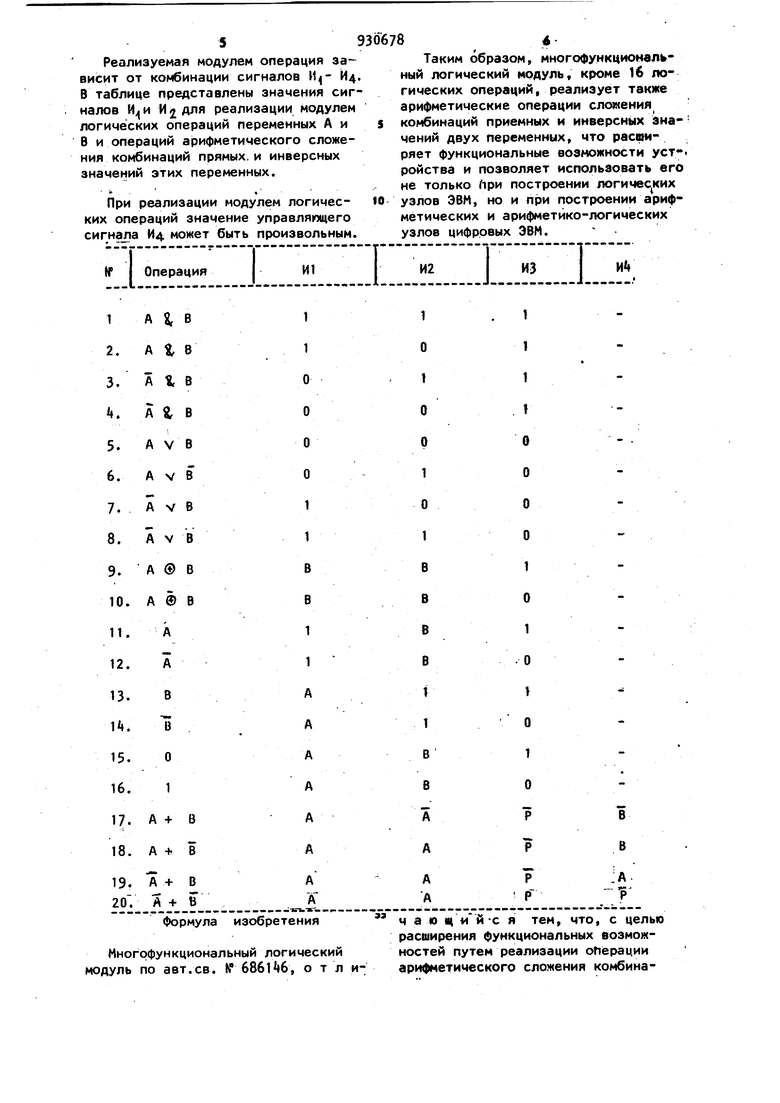

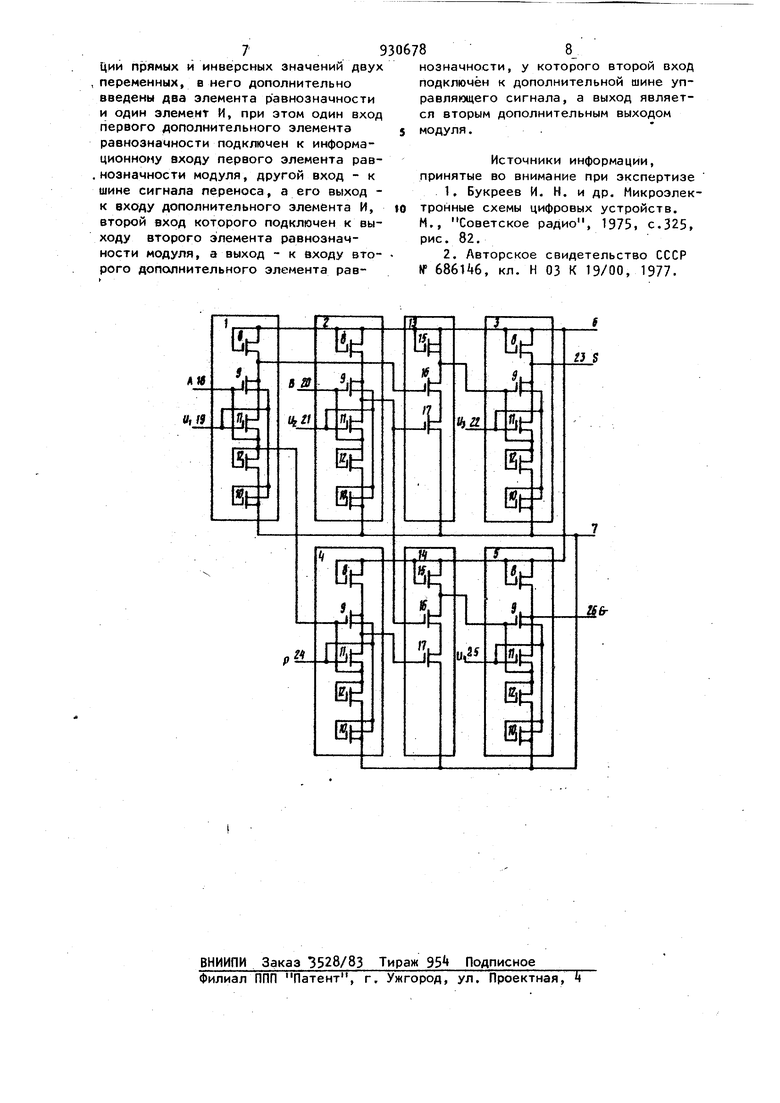

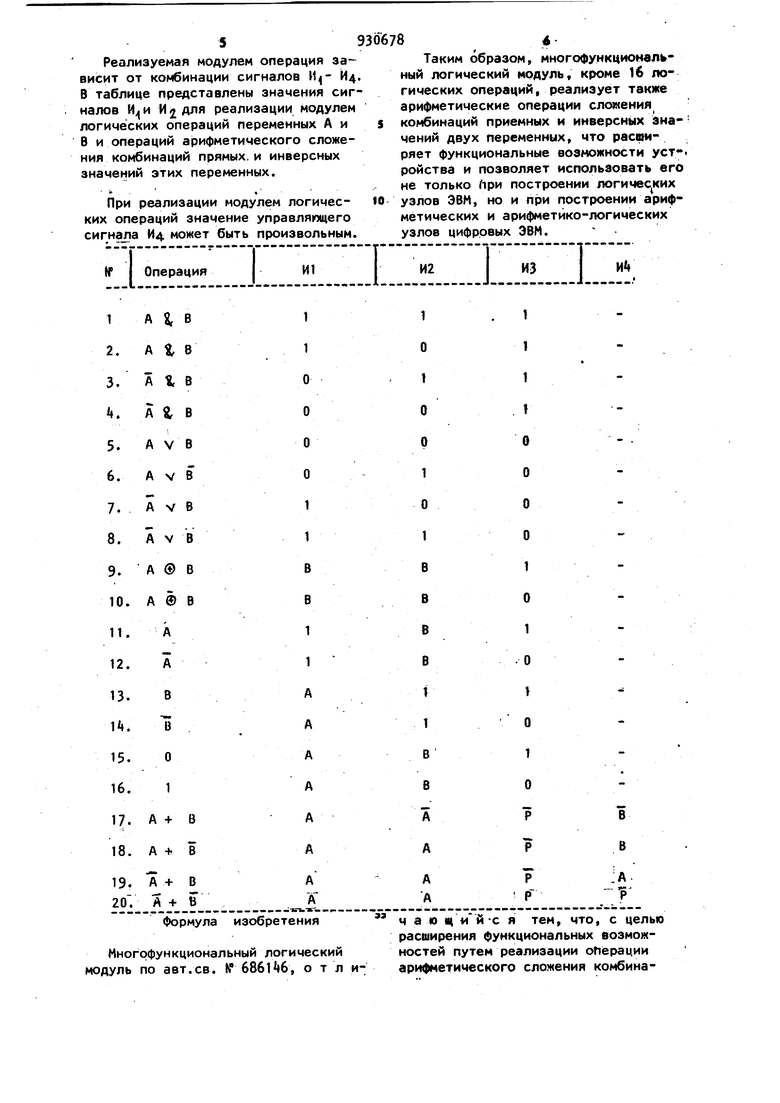

Недостатком этого устройства является то, что оно реализует только .логические функции двух переменных и не реализует операцию арифметичес3 9 кого сложения комбинаций прямых и инверсных значений двух переменных. Цель изобретения - расширение функциональных возможностей устройства путем реализации операции ариф метического сложения комбинаций пря мых и инверсных значений двух переменных. Для достижения поставленной цели в многофункциональный логический эл мент на МОП-транзисторах, содержащий три элемента равнозначности, в каждом из которых между шинами питания включен последовательно нагрузочный транзистор и две параллельные ветви из последовательно включе ных переключающего и второго нагрузочного транзисторов, в каждой ветви затвор переключающего транзистора подключен к истоку переключающего транзистора другой ветви, и один элемент И, образованный последовательно включенными между шинами питания нагрузочным транзистором и двумя переключающими транзисторами, причем в первом и во бтором элементе равнозначности один вход подключен к соответствующей информационной шине, а второй - к соответствующей управляющей шине, выходы эти элементов через элемент И подключен к входу третьего элемента равнознач ности, другой вход которого подключен к третьей управляющей шине, дополнительно введены два элемента ра нозначности и один элемент И, при этом один вход первого дополнительного элемента равнозначности подключен к информационному входу первого элемента равнозначности модуля другой вход - к шине сигнала переноса , а его выход - к входу дополнительного элемента, второй вход ко торого подключен к выходу второго элемента равнозначности модуля, а выход - к входу второго дополнитель ного элемента равнозначности, у которого второй вход подключен к дополнительной шмне управляющего си|- нала, а выход является вторым дополнительным выходом модуля. На чертеже представлена принципиальная электрическая схема устройства . Многофункциональный логический м дуль содержит пять элементов 1-5 ра нозначности между шинами 6 и 7 пита ния которых последовательно включены нагрузочный транзистор 8 и две параллельные ветви из последовательно включенных переключающего и второго нагрузочного транзисторов (соответстве нно 9-10 для одной ветви и 11-12 для другой). Затвор переключающего транзистора 9 подключен к истоку переключающего транзистора 11, а затвор транзистора 11 - к истоку транзистора 9. Каждый из двух элементов 13 и 1, образован последовательно включенными между шинами питания нагрузочным транзистором 15 и двумя переключающими транзисторами 16 и 17. При этом один вход элемента 1 подключен к информационной шине 18, а второй - к управляющей шине 19, соответственно, один из входов элемента 2 подключен к второй информационной шине 20, а второй - к второй управляющей шине 21, выходы элементов 1 и 2 подключены к соответствующим входам элемента 13, выход которого подключен к одному из входов элемента 3. Второй вход элемента 3 подключен к третьей управляющей шине 22, а выход элемента 3 является первым выходом модуля 23. ,0дин из входов дополнительного элемен та равнозначности подключен к шине 18,а второй - к шине 24 сигнала переноса. Выходы элементов 2 и Ц подключены к соответствующим входам дополнительного элемента И 14, выход которого подключен к одному из входов дополнительного элемента 5 равнозначности, второй вход которого подключен к четвертой управляющей шине 25, а выход является вторым дополнительным выходом модуля 26. Устройство работает следую1чим образом. На управляющие шины 19, 21, 22 и 25 поступают, соответственно,управляющие сигналы H;j- Н, одновременно на шины 18 и 20, поступают информационные сигналы в виде двоичных кодов переменных А и D. При реализации операции арифметического сложения комбинаций прямых и инверсных значений Переменных А и В на шину 2Ц поступает сигнал переноса Р из предыдущего разряда. На выходе 23 формируется сигнал , S - результат выполнения логической или арифметической операции, а на выходе 2б формируется сигнал переноса в старший разряд G. Реализуемая модулем операция зависит от комбинации сигналов Ид В таблице представлены значения сиг налов И 2 для реализации модулем логических операций переменных А и В и операций арифметического сложения комбинаций прямых, и инверсных значений этих переменных. « При реализации модулем логических операций значение управляющего сигнала И4 может быть произвольным. Формула изобретения Многрфункциональный логический модуль по авт.св. К 6861(б, о т л и84Таким образом, многофункциональный логический модуль, кроме 16 логических операций, реализует также арифметические операции сложения комбинаций приемных и инверсных значений двух переменных, что расширяет функциональные возможности ycT-i ройства и позволяет использовать его не только Лри построении логических узлов ЭВМ, но и при построении арифметических и арифметико-логических узлов цифровых ЭВМ. ч а ю щи и-с я тем, что, с целью расширения функциональных возможностей путем реализации операции арифметического сложения комбинаЦии прямых и инверсных значений двух , переменных, в него дополнительно введены два элемента равнозначности и один элемент И, при этом один вход первого дополнительного элемента равнозначности подключен к информационному входу первого элемента рав.нозначности модуля, другой вход - к шине сигнала переноса, а его выход к входу дополнительного элемента И, второй вход которого подключен к выходу второго з лемента равнозначности модуля, а выход - к входу второго дополнительного элемента равнозначности, у которого второй вход подключён к дополнительной шине управляющего сигнала, а выход являетсл вторым дополнительным выходом модуля.

Источники информации, принятые во внимание при экспертизе

1,Букреев И. Н. и др. Микроэлектронные схемы цифровых устройств. М., Советское радио, 1975, с.325, рис. 82.

Авторы

Даты

1982-05-23—Публикация

1980-08-13—Подача