f

Изобретение относится к импульсной технике и предназначено для реализации всех логических функций двух переменных.

Цель изобретения - повышение надежности и расширение области применения.

Поставленная цель достигается тем, что модуль имеет минимальное число настроечных входов, что определяет простоту его настройки и реа лкзацАи блоков управления при построении на его основе автоматов с памятью.

Кроме того, модуль обладает боле широкими схемотехническими возможностями, так как имеет четыре выхода, на каждом из которых реализуются различные логические функции. Это значительно упрощает реализац ию на его основе шoгoвыxoдныx адаптивных вычислительных и управляющих структур.

На чертеже представлена электрическая принципиальная схема универсального логического модуля.

Универсальный логический модуль содержит первую I и вторую 2 информационные шины, первую 3 и вторую 4 шины настройки, первую 5 и вторую 6 выходные шины, первый трехвходовый элемент И-НЕ 7, два двухвходовых элемента 8 и 9 РАВНОЗНАЧНОСТЬ, второй двухвходовый элемент И-НЕ 10, первая информационная шина 1 подключена к первым входам первого и второго элементов И-НЕ 7 и 10, вторая информационная шина 2 подключен к вторым входам первого элемента И-НЕ 7 и второго элемента 9 РАВНОЗНАЧНОСТЬ, первая шина 3 настройки подключена к второму входу второго элемента И-НЕ 10, вторая шина 4 настройки подключена к третьему

Значения сигналов на входах настройки

I

о

I

IоХ2Х2

XI/X2XI«ХаХ2- Х1Х2 ЛXI

ia XIXI ©х2Х1 Х2

Х1- Х2Х1ЛХ2XIV Х2XI I-Х2

213537

входу первого элемента И-НЕ 7, выходы элементов И-НЕ 7 и 10 подключены к входам первого элемента РАВНОЗНАЧНОСТЬ 8, инверсный выход которого подключен к первому входу второго элемента РАВНОЗНАЧНОСТЬ 9, прямые и инверсные выходы элементов РАВНОЗНАЧНОСТЬ 8 и 9 соединены с выходными шинами 5,6,11 и 12.

Между шинами 13 и 14 питания включены цепочки МОП-транзисторов, образующие первый 7 и второй 10 элементы И-НЕ (транзисторы 15-18, 19-21 соответственно) и первый 8 и второй 9 элементы РАВНОЗНАЧНОСТЬ 8 и 9 (транзисторы 22 - 26, 27 - 31 соответственно).

Первый элемент И-НЕ выполнен из трех переключательных 15-17 и одном нагрузочном 18 транзисторах, второй элемент И-НЕ 10 вьшолнен из двух переключательных 19 и 20 и нагрузочном 21 транзисторах. Первый 8 (второй 9) элемент РАВНОЗНАЧНОСТЬ состоит из последовательно включенного нагрузочного транзистора 28 и двух параллельно включенных ветвей, каждая состоит из последовательно включенных переключательного и второго нагрузочного транзисторов (соответственно 23,26,28 и 31 для одной ветви и 24,25,29 и 30 для другой ветви).

Устройство работает следующим образом.

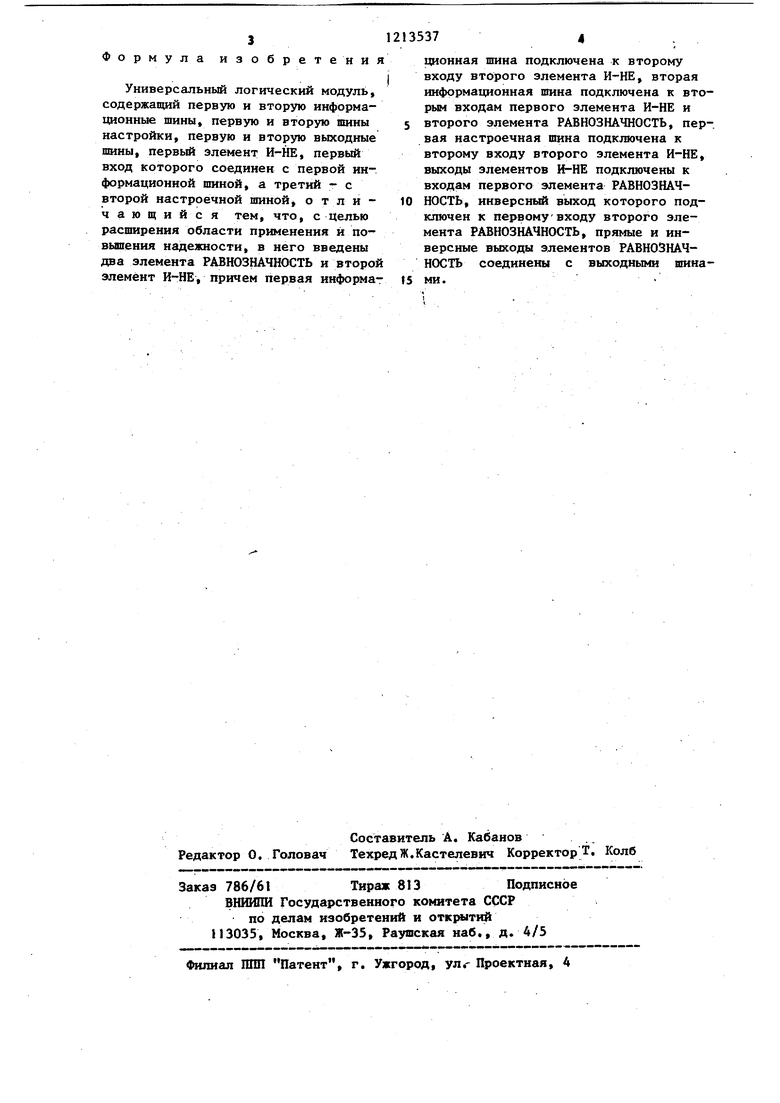

На информационные шины 1 и 2 поступают входные переменные XI и Х2 соответственно. Одновременно на шины 3 и 4 настройки подаются сигналы настройки И1 и И2 соответственно. При этом на выходных шинах 5,6, 11 и 12 устройства реализуются логические фукции в соответствии с приведенной таблицей.

Функции, реализуемые на выходах

1

11

i:i

Формула изобретения

Универсальный логический модуль, содержащий первую и вторую информа- 1Д1Онные шины, первую и вторую шины настройки, первую и вторую выходные шины, первый элемент И-НЕ, первый вход которого соедииен с первой информационной шиной, а третий - с второй настроечной шиной отличающийся тем, что, с Целью расширения области применения и повышения надежности, в иего введены два элемента РАВНОЗНАЧНОСТЬ и второй элемент И-НЕ, причем первая информаСоставитель А. Кабанов .. Редактор О. Головач Техред Ж.Кастелевич Корректор Т,

Заказ 786/61 Тираж 813 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул.- Проектная, А

ционная шина подключена к второму входу второго элемента И-НЕ, вторая информациоиная шина подключена к вторым входам первого элемента И-НЕ и второго элемента РАВНОЗНАЧНОСТЬ, первая настроечная шина подключена к второму входу второго элемента И-НЕ, выходы элементов И-НЕ подключены к входам первого элемента РАВНОЗНАЧНОСТЬ, инверсный выход которого подключен к первому входу второго элемента РАВНОЗНАЧНОСТЬ, прямые и инверсные выходы элементов РАВНОЗНАЧНОСТЬ соединены с выходными шинами,

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1985 |

|

SU1274148A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1676093A1 |

| Многофункциональный логический модуль | 1991 |

|

SU1793542A1 |

| Многофункциональный логический элемент | 1980 |

|

SU898618A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Многофункциональный логический модуль | 1980 |

|

SU930678A2 |

| Многофункциональный логический модуль | 1989 |

|

SU1637020A1 |

| Мультиплексор | 1988 |

|

SU1538248A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1732462A1 |

| Многофункциональный модуль | 1980 |

|

SU890557A1 |

Изобретение относится к импульсной, технике и предназначено для реализации всех логических функций двух переменных. Цель изобретения - повышение надежности модуля и расширение области его применения. Это достигается тем, что модуль имеет минимальное количество настроечных входов. Это определяет простоту настройки и реализации блоков управления. Модуль содержит информационные шины 1 и 2, шины настройки 3 и 4, выходные шины 5 и 6, трехвхо- довый логический элемент (ЛЭ) И-НЕ 7. В него дополнительно введены два двухвходовых элемента РАВНОЗНАЧНОСТЬ 8 и 9 и двухвходовой ЛЭ И-НЕ 10. Первый и второй ЛЭ И-НЕ образованы транзисторами 15 - 18 и 19 - 21 соответственно, элементы 8 и 9 - транзисторами 22-26 и 27-31 соответственно. Выходными шинами являются шины 11 и 12. 1 ил. 00 ел со

| Патрон для ламп накаливания | 1923 |

|

SU898A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-23—Публикация

1984-07-23—Подача