(5) УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ СКОРОСТИ ДВИЖЕНИЯ МАГНИТНОГО НОСИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный вентильный электропривод с комбинированным управлением | 1987 |

|

SU1610588A1 |

| Цифровое устройство для управления многофазным импульсным преобразователем | 1989 |

|

SU1735990A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для стабилизации вакуума | 1983 |

|

SU1149060A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Счетчик эектроэнергии | 1983 |

|

SU1190280A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

1

Изобретение относится к приборостроению и может быть использовано в аппаратуре точной магнитной записи. Известны устройства для регулирования скорости движения маг,нитного носителя, содержащие частотный либо фазовый дискриминатор, с помощью которых оценивается отклонение частоты или фазы контрольных сигналов, поступаю-,, щих с носителя и вырабатывается

i управляющий сигнал, компенсирующий дане)ое отклонение СО и jf2j.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее формирователь входных импульсов, соединенный с входами частотного и фазового дискриминаторов, генератор опорной частоты, подключенный через управляемый делитель частоты к ДРУГИМ входам частотного и фазового дискриминаторов, а также последовательно соединенные.

усилитель мощности и электродвигатель.

В известном устройстве изменение скорости движения магнитного носителя приводит к изменению частоты и фазы контрольной последовательности импульсов, которая после деления поступает на вход частотного и фазового дискриминаторов. Сигналы частотного и фазового дискриминаторов суммируются и через усилитель мощности воздействуют на элекУродвигатель, изменяя необходимым образом его обороты З.

Однако при изменении частоты контрольных импульсов от нуля до номинальности и вообщев случаях больших рассогласований, фаза сигнала изменится на 2Хи радиан, где число in зависит от величины рассогласования, что вызовет значительное снижение точности регулирования скорости.

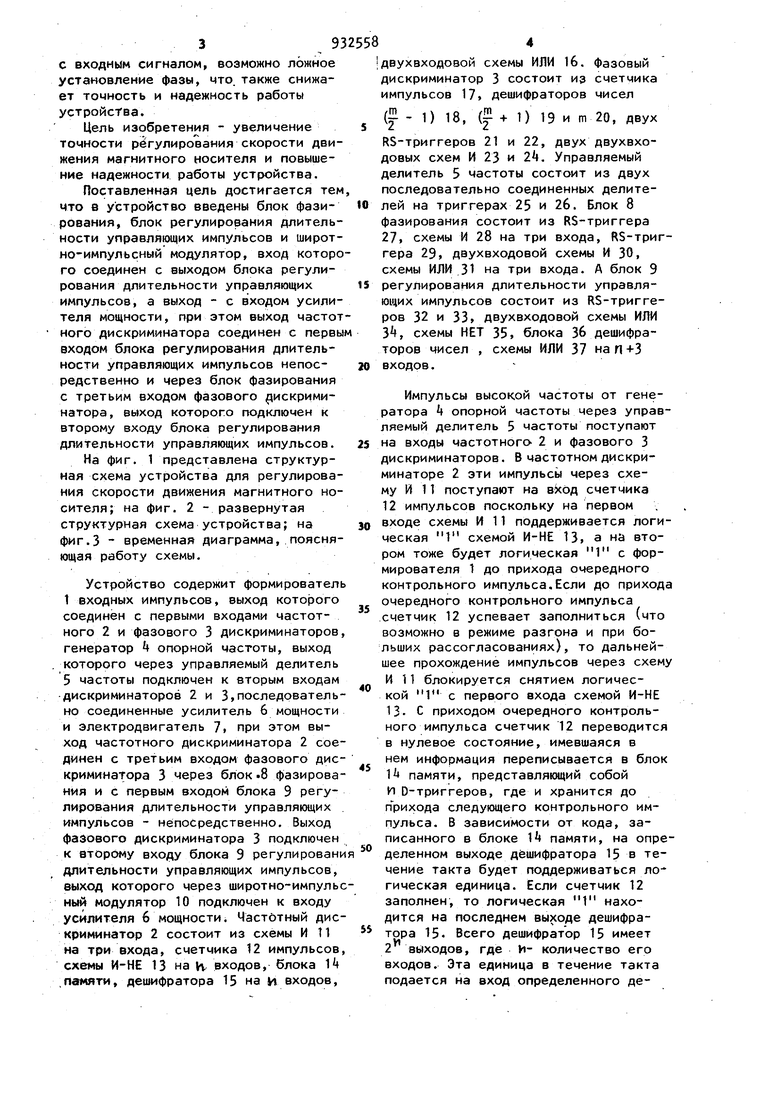

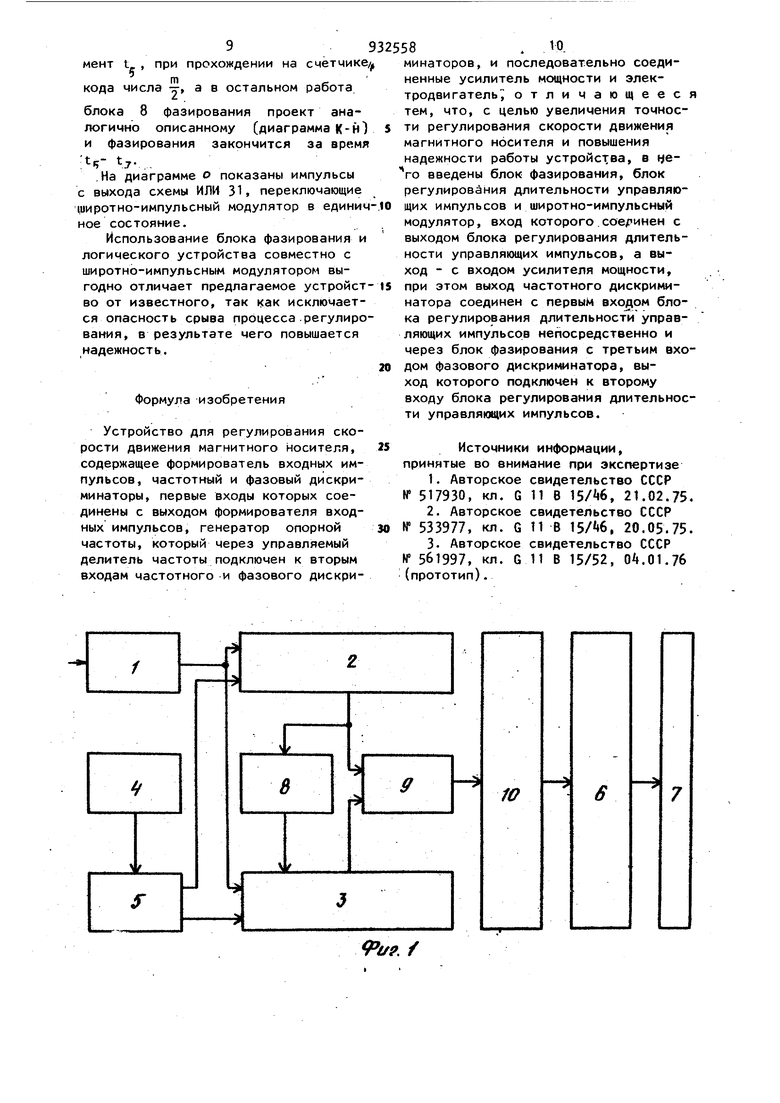

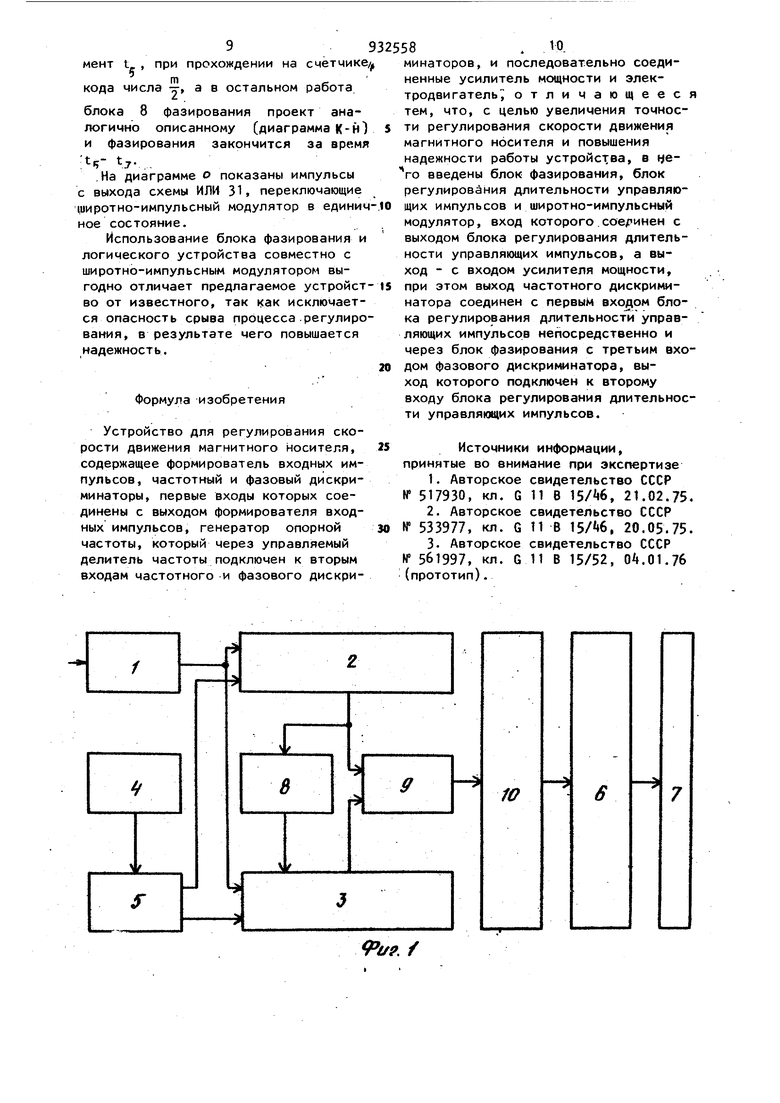

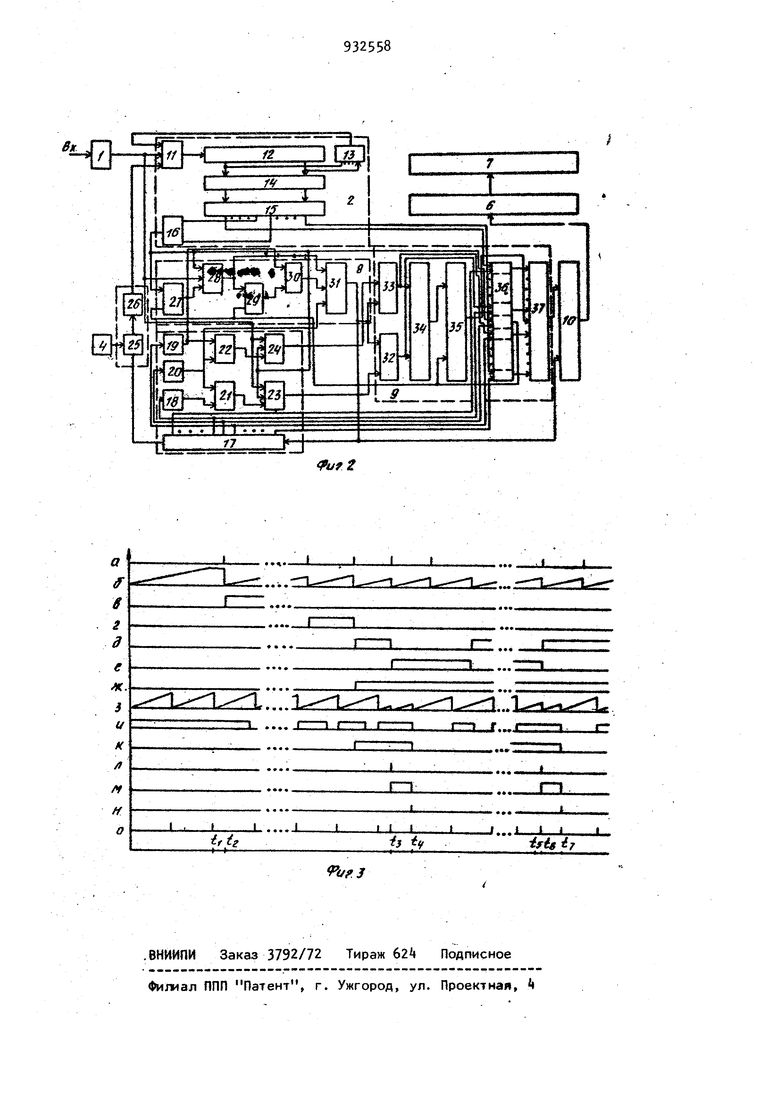

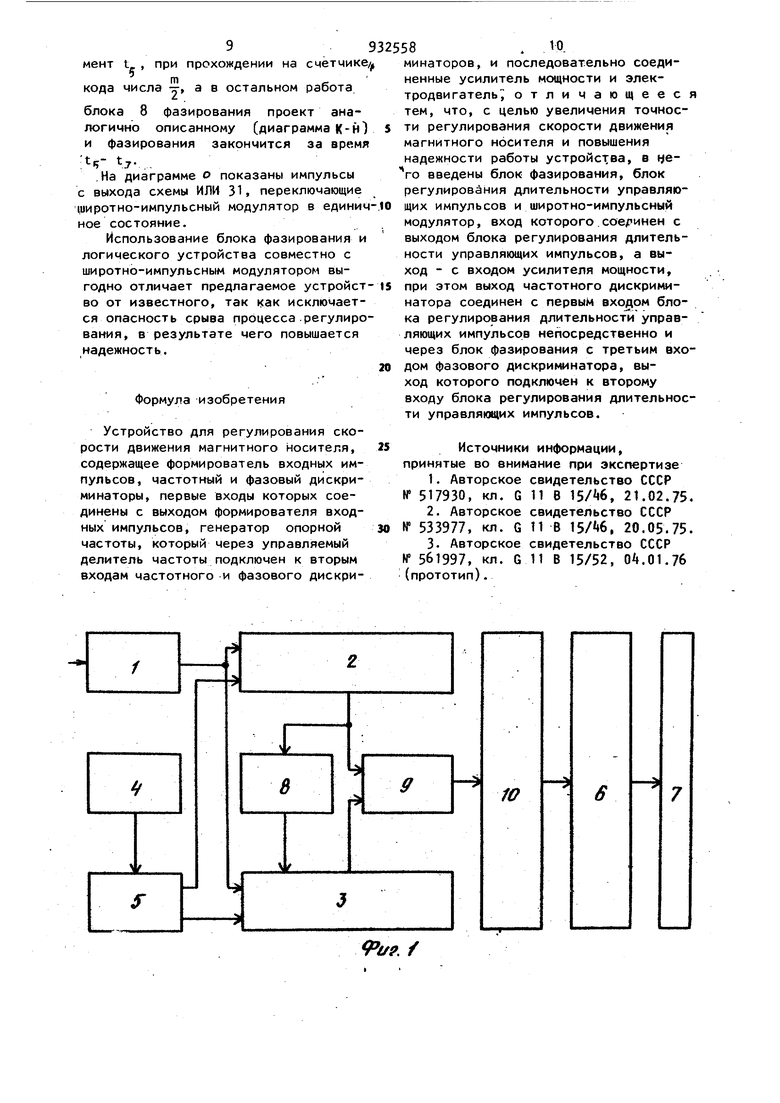

того, поскольку генератор опорной частоты не синхронизирован 393 с входным сигналом, возможно ложное установление фазы, что. также снижает точность и надежность работы устройства. Цель изобретения - увеличение точности регулирования скорости движения магнитного носителя и повышение надежности работы устройства. Поставленная цель достигается тем что в устройство введены блок фазирования, блок регулирования длительности управляющих импульсов и широтно-импульсный модулятор, вход которо го соединен с выходом блока регулирования длительности управляющих импульсов, а выход - с входом усилителя мощности, при этом выход частот ного дискриминатора соединен с первы входом блока регулирования длительности управляющих импульсов непосредственно и через блок фазирования с третьим входом фазового дискриминатора, выход которого подключен к второму входу блока регулирования длительности управляющих импульсов. На фиг. 1 представлена структурная схема устройства для регулирования скорости движения магнитного носителя; на фиг. 2 - развернутая структурная схема устройства; на фиг.З - временная диаграмма, поясняющая работу схемы. Устройство содержит формирователь t входных импульсов, выход которого соединен с первыми входами частотного 2 и фазового 3 дискриминаторов, генератор опорной частоты, выход которого через управляемый делитель 5 частоты подключен к вторым входам дискриминаторов 2 и 3,последовательно соединенные усилитель 6 мощности и электродвигатель 7, при этом выход частотного дискриминатора 2 соединен с третьим входом фазового дискриминатора 3 через блок .8 фазирования и с первым входом блока 9 регулирования длительности управляющих импульсов - непосредственно. Выход фазового дискриминатора 3 подключен к вторсжу входу блока 9 регулировани длительности управляющих импульсов, выход которого через широтно-импульс ный модулятор 10 подключен к входу усилителя 6 мощности. Частотный дискриминатор 2 состоит из схемы И 11 на три входа, счетчика 12 импульсов, схемы И-НЕ 13 на К входов, блока k .памяти, дешифратора 15 на И входов. двухвходовой схемы ИЛИ 16. Фазовый дискриминатор 3 состоит из счетчика импульсов 17, дешифраторов чисел (f - 1) 18, ( + 1) 19 и m 20, двух RS-триггеров 21 и 22, двух двухвходовых схем И 23 и 24. Управляемый делитель 5 частоты состоит из двух последовательно соединенных делителей на триггерах 25 и 26. Блок 8 фазирования состоит из RS-триггера 27, схемы И 28 на три входа, К5-три1- гера 29, двухвходовой схемы И 30, схемы ИЛИ 31 на три входа. А блок 9 регулирования длительности управляющих импульсов состоит из RS-триггеров 32 и 33, двухвходовой схемы ИЛИ 3, схемы НЕТ 35, блока 36 дешифраторов чисел , схемы ИЛИ 37 на п+3 входов. Импульсы высокой частоты от генератора опорной частоты через управляемый делитель 5 частоты поступают на входы частотного- 2 и фазового 3 дискриминаторов. В частотном дискриминаторе 2 эти импульсь через схему И 11 поступают на вхйд счетчика 12 импульсов поскольку на первом входе схемы И 11 поддерживается логическая 1 схемой И-НЕ 13, а на втором тоже будет логическая 1 с формирователя 1 до прихода очередного контрольного импульса.Если до прихода очередного контрольного импульса счетчик 12 успевает заполниться (что возможно в режиме разгона и при больших рассогласованиях), то дальнейшее прохождение импульсов через схему И 11 блокируется снятием логической 1 с первого входа схемой И-НЕ 13- С приходом очередного контрольного импульса счетчик 12 переводится в нулевое состояние, имевшаяся в нем информация переписывается в блок 1 памяти, представляющий собой И D-триггеров, где и хранится до прихода следующего контрольного импульса. В зависимости от кода, записанного в блоке И памяти, на определенном выходе дешифратора 15 в течение такта будет поддерживаться ло- гическая единица. Если счетчик 12 заполнен, то логическая 1 находится на последнем выходе дешифратора 15. Всего дешифратор 15 имеет 2 выходов, где И- количество его входов. Эта единица в течение такта подается на вход определенного дешифратора числа блока 36 дешифраторов чисел, блок 9 регулирования длитедьности управлйющих импульсов. Дешифраторы чисел представляют собой многовходовые схемы И, каждая из которых связана с определенными выходами счетчика 17 фазового дискриминатора 3.Таким образом, при определенном коде на счетчике 17, только на выходе одного определенного дешифратора числа блока 36 дешифраторов чисел, возможно появление единичного импульса при условии, что на дополнительный его вход подан единичный логический уровень от дешифратора 15 частотного дискриминатора 2, Поскольку в течение такта логическая 1 с частотного дискриминатора 2 подается только на один определенный дешифратор числа блока 9 регулирования длительности управлякицих импульсов, то на его выходе и появится единичный импульс, который пройдя через схему ИЛИ 37, переведет в нулевое состояние широтно-импульсный модулятор 10, который в начале такта устанавливается в единичное состояние сигналом с выхода схемы ИЛИ 31. Следовательно, ширина управляющего импульса с выхода широтноимпульсного модулятора 10 зависит от кода числа зафиксированного на счетчике 12 частотного дискриминатора 2.

Сигнал с фазового дискриминатора 3 до определенного момента блокируется нулевым потенциалом, подаваемым с выхода схемы ИДИ 16 на .входы схем И 23 и 2 фазового дискрисминатора 3. Таким образом, исключается нежелательное влияние сигнала фазового дискриминатора на процесс регулирования при больших рассогласованиях. Как только разность между текущим и номинальным значениями скорости вращения электродвигателя уменьшится до установленной величины, единичный потенциал начнет поо2чередно появляться на выходах - 1

2

и у + 1 дешифратора 15, подключенных к входам схемы ИЛИ 16. На выхьде последней установится логическая единица, которая разблокирует фазовый дискриминатор 3 и разрешит

работу дешифратору числа у блока 36 дешифраторов чисел.

Характеристика фазового дискриминатора 3 формируется в RS-триггерах 21 и 22 по сигналам от дешифраторов чисел (у - l)l8, (у Ol9

и m 20. В начале такта счетчик 1/ и триггер 22 переводятся в нулевое состояние, а триггер 21 - в единичное сигналом с дешифратора 20 числа п. Триггер 21 переводится в нулевое состояние сигналом с дешиф-.

ратора числа (у - 1)18, а триггер 22 в единичное состояние сигналом с

дешифратора числа (у + 1)19. Таким образом, на выходе триггера 21 поддерживается логическая 1 от начала такта и до дешифрации числа

(у - 1), а на триггере 22 - от дешифрации числа у -f 1 и до конца таК

та. Эти единичные уровни поступают на входы схем И 23 и 2 соответст-.

венно.

Контрольный импульс с формирователя 1 может поступать на входы схем И 23 и 24 фазового дискриминатора 3 с опережением, отставанием либо

без фазового рассогласования.

Если контрольный импульс поступает с опережением по фазе (текущая скорость выше номинальной), т.е., в момент между началом такта и прохождением на счетчике 17 кода, соm

ответствующего числу у - 1, то он

пройдет через схему И 23 поскольку в этом интервале времени на другом

ее входе поддерживается логическая 1 триггером 21, и переведет RSтриггер 32 блока 9 регулирования длительности управляющих импульсов в единичное состояние. Единичный уровень с триггера 32 до конца такта разрешает работы дешифрато ру числа

у - 1 блока 36 дешифраторов чисел.

В случае отставания по фазе контрольного импульса (текущая скорость . ниже номинальной), он пройдет через схему И 2 и переведет триггер 33 в единичное состояние, который разрешит работу дешифратору числа у.+

блока 36 дешифраторов чисел.

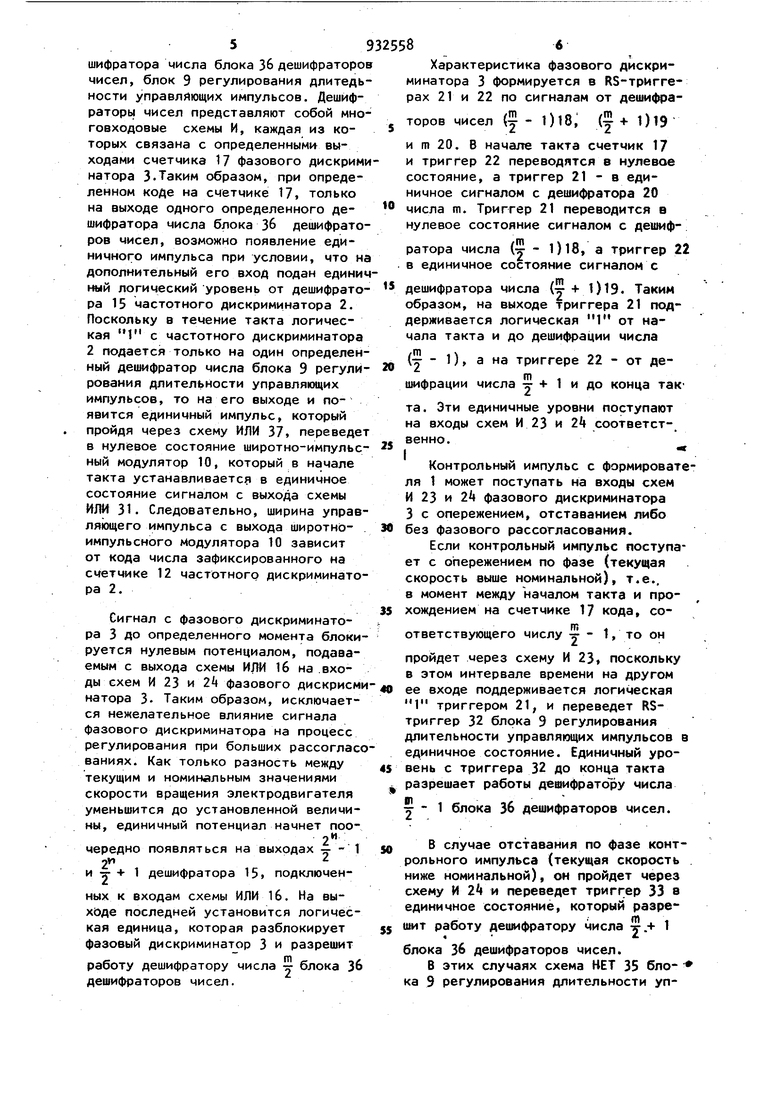

В этих случаях схема НЕТ 35 бло- ка 9 регулирования длительности управляющих импульсов задерживает сиг нал от дешифратора числа блока Зб дешифраторов чис.ел благодаря тому, что на запрещающем входе схемы НЕТ 35 поддерживается логическая 1, поступающая через схему ИЛИ З от триггера 32 либо 33. И наконец, если контрольный импульс поступает без рассогласования то он поступает на фазовый дискрими натор 3 в интервале между протеканием на счетчике 17 кодов чисел у - 1 и у + 1. Поскольку в этом интервале триггеры 21 и 22 находятся в нулевом состоянии, то контрольный импульс не пройдет ни через схе му И 2-3, ни через схему И 24. Следовательно триггеры 32 и 33 блока 9 регулирования длительности управляю щих импульсов остаются в нулевом состоянии, чем разрешаетсяпрохождение сигналов от дешифратора числа у блока Зб дешифраторов чисел чере схему НЕТ 35. Этот сигйал через схему ИЛИ 37 переводит в «улевое со тояние широтно-импульсный модулятор 10 точно посредине такта. Для фазового согласования цикла работы фазового дискриминатора 3 с произвольно поступающими контрольными импульсами служит блок В фазирования. Перед рассмотрением его работы необходимо отметить, что сче чик 12 заполняется за два, а счетчик 17 за один такт. Частота поступления импульсов на счетчик 17 (емкостью т) в несколько раз выше, чем на счетчик .12, что связано с тр буемой точностью. Процесс заполнения счетчико в 12 и 17 показан на диаграммах д соответстаенно (фиг. 3). 8 режиме разгона счетчик 12 успевает заполниться (.диаграмма 6 момент t) и сохраняет свое состояние до поступления контрольного импульса (момент t). Контрольные импульсы изображе ны на диаграмме 3. Начало их поступлейия взято произвольно. С поступлением на вход устройства первог контрольного импульса счетчик 12 сбрасывается, а на последнем выходе Р дешифратора 15 устанавливаетс единичный уровень (диаграмма ). До момента t,j с дешифратора 15 не поступает разрешающий сигнал в блок 36 дешифраторов чисел, поэтому широтноимпульсный модулятор 10 не сбрасывается fдиаграмма li) и на электродвигатель 7 подается постоянное напряжение, что способствует быстрейшему его разгону. По истечении некоторого времени (зависящего от характеристик электродвигателя, параметров схемы и выхода дешифратора) сигнал появится на RJ выходе дешифратора 15 (диаграмма г). Соответственно уменьшается длительность управляющих импульсов на выходе широтно-импульсного модулятора 10 (диаграмма и). Наконец, при приближении скорости электродвигателя к номинальной, единичный уровень будет появляться на выходах р р -Х--1 и - + 1 дешифратора 15, диаг раммы д и е , а на выходе схемы ИЛИ 16 устанавливается единичный потенциал (диаграмма й-), который переводит триггер 27 блока 8 фазирования в единичное состояние (диаграмма К), чем разрешает его работу. С поступлением на вход схемы И 28 очередного контрольного импульса. (назовем его переключающим, момент времени t-), он проходит через схему И 28 (диаграмма л), переключает триггер 29 в единичное состояние (диаграмма м), а через схему ИЛИ 31 сбрасывает счетчик 17 в исходное состояние (диаграмма-, точка t). Как только на счетчике появится код, соответствующий половине цикла его работы, импульс дешифратора 19 числа пройдет через схему И 30 (диаграмма н), так как на другом ее входе логическая 1 от триггера 29 схема ИЛИ 31 снова сбросит счетсик 17 в исходное состояние (диаграмма «у, точка t). Этим же импульсом переводятся в исходное состояние триггеры 27 и 29 (диаграммы k и v), Работа блока фазирования прекращается. Следующие контрольные импульсы оказываются привязанными к средине цикла работы счетчика 17 (диаграммы «, . В рассмотренном случае переключающий импульс поступает в момент t J с опережением по фазе . Если пе 1Ъключающий импульс, поступает с отставанием по фазе, момент tg, то сбрасывание счетчика 17 происходит в мо

мент t- , при прохождении на счетчике/

m

а в остальном работа кода числа -j.

блока 8 фазирования проект аналогично описанному (диаграмма К-н) и фазирования закончится за время

;ч-17- ,На диаграмме о показаны импульсы с выхода схемы ИЛИ 31, переключающие чииротно-импульсный модулятор в единич ное состояние.

Использование блока фазирования и логического устройства совместно с широтно-импульсным модулятором выгодно отличает предлагаемое устройство от известного, так как исключается опасность срыва процесса.регулирования, в результате чего повышается надежность.

Формула изобретения

Устройство для регулирования скорости движения магнитного носителя, содержащее формирователь входных импульсов, частотный и фазовый дискриминаторы, первые входы которых соединены с выходом формирователя входных импульсов, генератор опорной частоты, который через управляемый делитель частоты подключен к вторым входам частотного и фазового дискриминаторов, и последовательно соединенные усилитель мощности и электродвигатель, отличающееся тем, что, с целью увеличения точности регулирования скорости движения магнитного носителя и повышения надежности работы устройства, в введены блок фазирования, блок регулирования длительности управляющих импульсов и широтно-импульсный модулятор, вход которого.сое/инен с выходом блока регулирования длительности управляющих импульсов, а выход - с входом усилителя мощности, при этом выход частотного дискриминатора соединен с первым входом блока регулирования длительност | управляющих импульсов непосредственно и через блок фазирования с третьим входом фазового дискриминатора, выход которого подключен к второму входу блока регулирования длительности управляющих импульсов.

Источники информации, принятые во внимание при экспертизе

№ 517930, кл. G 11 В 15А6, 21.02.75.

№ 533977, кл. G 116 15А6, 20.05.75.

№ 561997, кл. G 11 В 15/52, 04.01.76 (прототип).

/

II

, I

.

n

I I I

Ь tf

iftgi,

Авторы

Даты

1982-05-30—Публикация

1979-12-12—Подача