(S) ЛОГАРИФМИЧЕСКИЙ УСИЛИТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь | 1970 |

|

SU868785A2 |

| Множительно-делительное устройство | 1981 |

|

SU995098A1 |

| Устройство для деления аналоговыхСигНАлОВ | 1979 |

|

SU822203A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Логарифмический преобразователь | 1982 |

|

SU1064283A1 |

| Устройство для измерения сопротивления и емкости электрических и сигнальных сетей относительно земли | 1986 |

|

SU1370611A1 |

| Множительное устройств | 1979 |

|

SU824223A1 |

| Логарифмический преобразователь | 1979 |

|

SU877570A2 |

| Вычислительное устройство | 1981 |

|

SU978159A1 |

| Логарифмический усилитель | 1982 |

|

SU1080156A1 |

1

Изобретение относится к усилительным устройствам с логарифмической амплитудной характеристикой и может быть использовано в аналоговых вычислительных машинах.

Известен логарифмический усилитель, содержащий операционный усилитель, логарифмирующий диод и масштабный резистор 1 }

Однако, этот логарифмический усилитель характеризуется низкой точностью работы.

Наиболее близким к предлагаемому является логарифмический усилитель, содержащий первый и второй масштабные резисторы, ключ генератор коммутирующих импульсов, источник опорного напряжения, избирательный усилитель, фазочувствит.ельный выпрямитель, первый коммутатор .

Недостатком известного логарифмического усилителя является сравнительно малая точность работы.

Цель изобретеня - повышение точности работы.

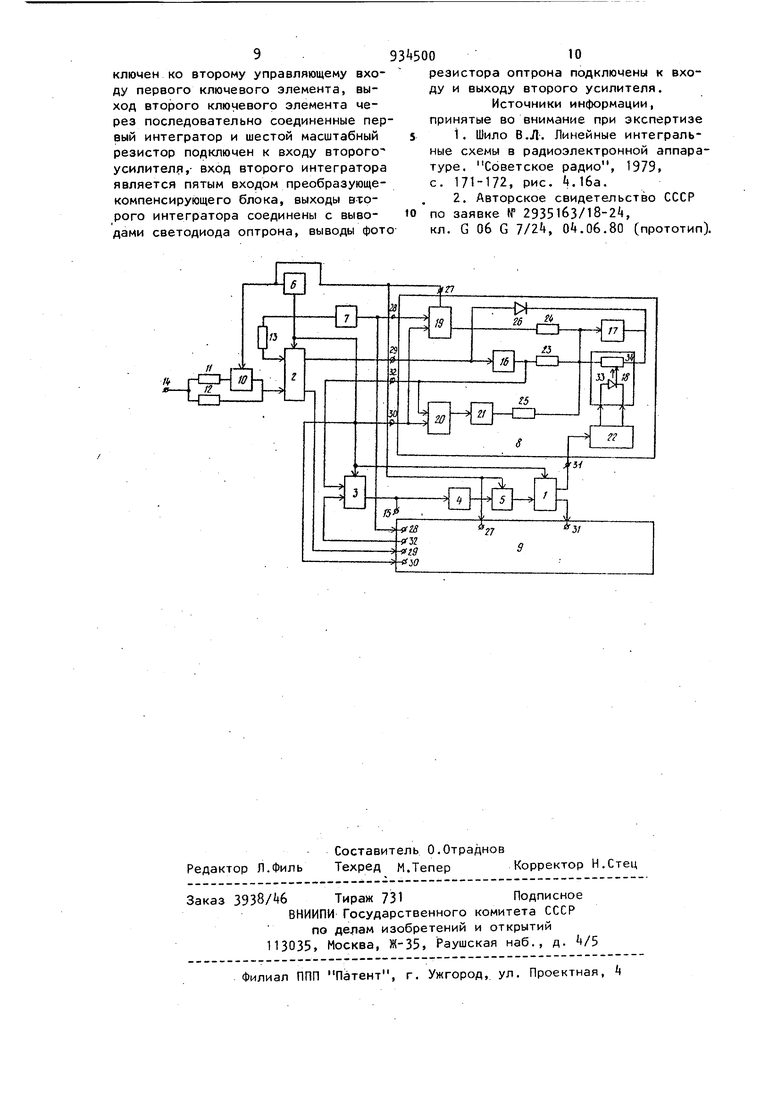

Для достижения указанной цели в известный логарифмический усилитель, содержащий первый и второй масштабные резисторы, ключ, генератор коммутирующих импульсов, источник опорного напряжения, соединенные последовательно избир-тельный усилитель, фазочувствительный выпрямитель и первый коммутатор, первый вывод первого масштабного резистора соединен с входом ключа, выход которого подключен к первому выводу второго масштабного резистора, второй вывод последнего соединен со вторым выводом первого масштабного резистора и является входом логарифмического усилителя, вход избирательного усилителя является выходом логарифмического усилителя, управляющий вход ключа соединен с первым выходом генератора коммутирующих импульсов, введены первый и второй преобразующе-компенсирующие блоки, второй итретий коммутаторы и третий масштабный резистор, примем первый выход источника опорного напряжения через третий масштабный резистор подключен к первому входу второго коммута тора, второй вход которого соединен с выходом ключа, выход третьего коммутатора подключен к входу избирйтельного усилителя, второй выход генератора коммутирующих импульсов соединен с управляющими входами пер вого, второго и третьего коммутаторов, первый выход генератора коммутирующих импульсов подключен к коммутирующему входу фазочувствител ного выпрямителя и к первым входам первого и второго преобразующе-компенсирующих блоков, второй выход ис точника опорного напряжения соедине со вторыми входами первого и второг преобразующе-компенсирукмдих блоков, первый и второй выходы второго коммутатора подключены к третьим входам соответственно первого и второго преобразующе-компенсирующих блоков, четвертые входы которых соединены со вторым выходом генератора коммутирующих импульсов, пятые входы первого и второго преобра ующекомпенсирующих блоков подключены соответственно к первому и второму выходам первого коммутатора, выходы первого и второго преобразующекомпенсирующих блоков соединены соответственно с Первым и вторым входами третьего коммутатора. Каждый преобразующе-компенсирующий блок содержит первый и второй усилители, первый и второй ключевые элементы, оптрон, первый и второй интеграторы, логарифмирующий ДИОД; четвертый, пятый и шестой масштабные резисторы, причем первый управляющий вход первого ключевого элемента является первым входом преобразующе-компенсирующего блока, вторым входом которого является вход первого ключевого элемента, вход первого усилителя является тре тьим входом преобразующе-компенсиру щего блока, выходом которого является выход первого усилителя, который через четвертый масштабный резистор соединен со входом второго усилителя и первым выводом пятого масштабного резистора, второй вывод которого подключен к выходу пер вого ключевого элемента, вход первого усилителя через логарифмирующий диод соединен с выходом второго усилителя, управляющий вход второго ключевого элемента является четвертым входом преобразующе-компенсирующего блока , выход первого усилителя соединен с информационным входом второго ключевого элемента, управляющий вход которого подключен к второму управляющему входу первого ключевого элемента, выход второго ключевого элемента через последовательно соединенные первый интегратор и шестой масштабный резистор подключен к входу второго усилителя, вход второго интегратора является пятым входом преобразующе-компенсирующего блока, выходы второго ин- . тегратора соединены с выводами светодиода оптрона, выводы фоторезистора оптрона подключены к входу и выходу второго усилителя. На чертеже изображена функциональнал схема предлагаемого логарифмического усилителя. Логарифмический усилитель содержит первый, второй и третий коммутаторы 1, 2 и 3, избирательный усилитель k, фазочувствительный выпрямитель 5, генератор 6 коммутирующих импульсов, источник 7 опорного напряжения, первый и второй преобразующе- компенсирующие блоки 8 и 9, ключ 10, первый, второй и третий масштабные резисторы 11, 12 и 13, вход 1 и выход 15 логарифмического усилителя, первый и второй усилители 16 и 17 оптрон 18, первый и второй ключевые элементы 19 и 20, первый и второй интеграторы 21 и 22, четвертый, пятый и шестой масштабные резисторы 23, 2k и 25, логарифмирующий диод 2б, первый, второй, третий, четвертый и пятый входы 27, 28, 29, 30 и 3 и выход 32 измерительного блока; оптрон 18 выполнен на светодиоде 33 и фоторезисторе 3. Логарифмический усилитель работает следующим образом. На первом и втором выходах гене,ратора 6 коммутирующих импульсов формируются сигналы в виде меандра, причем частота повторения сигнала на первом выходе значительно выше частоты повторения сигнала на втором выходе. Со второго выхода сигналм поступают на упоавляющие входы первого, второго и третьего коммутаторов 1, 2 и 3 и переключают их. В случае, когда сигнал на втором выходе генератора 6 коммутирующих импульсов равен единице, третий вход 29 первого преобразующе-компенсирующего блока 8 подключается с помощью второго коммутатора 2 к третьему масштабному резистору 13, а третий вход 29 второго преобразу ще-компенсирующего блока 9 подключен к выходу ключа 10. Вход избирательного усилителя k соединен с выходом 32 второго измерительного блока 9, выход фазочувствительного выпрямителя 5 подключен к пятому входу 31 второго преобразующе-компенсирующего блока 9, причем в пер вом преобразующе-компенсирующем блоке 8 первый ключевой элемент 19 разомкнут, а второй ключевой элемент 20 замкнут. Первый усилитель 1 неинвертирующий, а второй усилитель 17 инвертирующий, поэтому мож но считать, что логарифмирующий диод 26 включен в цепь отрицательной обратной связи и через него протекает весь ток, задаваемый чере третий масштабный резистор 13 источником 7 опорного напряже(ия. Эт ток вызывает падение напряжения на логарифмирующем диоде 2б и появление на выходе первого усилителя 16 напряжения,, равного отношению паде ния напряжения на логарифмирующем диоде 2б к коэффициенту усиления второго усилителя 17. Считаем, что в первом цикле напряжение на выходе второго интегратора 22 равно нулю. Выходное напряжение первого усилителя 1б интегрируется неинвертирующим первым интегратором 21 и напряжение с его поступает через шестой масш табный резистор 25 на вход второго усилителя 17. Это вызывает уменьше ние выходного напряжения первого усилителя 16. Процесс идет до тех пор, пока напряжение на выходе пер вого усилителя 1б не станет равным нулю. В этом случае напряжение на выходе второго интегратора -22 равно падению напряжения на логарифмирующем диоде 2б ( если сопротивление ре зистора 3 оптрона равно сопротивле нию шестого масштабного резистора 25). 0 , 6 В случае, когда сигнал на втором выходе генератора 6 коммутирующих импульсов равен нулю, третий вход 29 первого преобразующе-компенсирующего блока 8 подключается к выходу ключа 10, а третий вход 29 второго измерительного блока 9 соединяется с третьим масштабным резистором 13Вход избирательного усилителя соединяется с выходом первого усилителя 16 первого преобразующе-компенсирующего блока В, а выход фазочувствительного выпрямителя 5 соединяется со входом второго интегратора 22 первого преобразующе-компенсирующего блока 8. Второй ключевой элемент 20 преобразующе -koмпeнcиpyющeгo блока 8 закрывается, и первый интегратор 21 в нем переходит в режим хранения, а пер.вый ключевой элемент 19 начинает переключаться с частотой сигнала с первого выхода генератора 6 коммутирующих импульсов синхронно с ключом 1 о. Напряжение со входа k преобразуется в пульсирующий входной ток, который протекает через логарифмирующий диод 2б и. вызывает на нем соответствующее падение напря5кения. Постоянная составляющая этого напряжения зависит от напряжения на входе I, температурного потенциала и обратного тока логарифмирующего диода 26. Переменная составляющая зависит от температурного потенциала и соотношения сопротивлений первого и второго масштабных резисторов 11 и 12 и не зависит от напряжения на входе Ц и обратного тока логарифмирующего диода 2б. Синхронно с переменной составляющей на лога1эифмирующем диоде 26, но в противофазе через пятый масштабный резистор 2Ц на вход второго усилителя 17 поступает компенсирующее напряжение, в результате чего переменная составляющая на выходе первого усилителя 16 уменьшается. Переменная составляющая с выхода первого усилителя 16 поступает на вход избирательного усилителя , усиливается и выпрянпяется фазомувствительным выпрямителем 5, с выхода которого выпрямленное напряжение поступает на вход второго интегратора 22 первого преобразующе-компенсирующего блока 8. При изменении выходного напряжения второго ратора 22 меняется ток, протекающий 79 через светодиод оптрона 18, в результате изменяется сопротивление резкстора 3j оптрона. При этом пере меиная составляющая на выходе первого усилителя 16 уменьшается. Процесс идет до тех пор. пока переменная составляющая на выходе перво го усилителя 16 не станет равной ну лю и его постоянное напряжение является выходным напряжением логариф мического усилителя. Циклы настройки и работы первого и второго преобразующе-компенсирующих блоков 8 и 9 чередуются. Напряжение на выходе 15 пропорционально логарифму от напряжения на входе 1 Предлагаемый логарифмический уси литель по сравнению с известным обладает более высокой точностью ра боты благодаря стабилизации его фун циональной зависимости путем самонастройки. Формула изобретения 1. Логарифми.ческий усилитель, содержащий первый и второй масштабные резисторы, ключ, генератор коммутирующих импульсов, источник опорного напряжения, соединенные поО ледова тельно избирательный усилитель, фазо чуаствительный выпрямитель и первый коммутатор, первый вывод первого масштабного резистора соединен с вхо дом ключа, выход которого подключен к первому выводу второго масштабного резистора, второй вывод последнего соединен со вторым выводом первого масштабного резистора и является входом логарифмического усилителя, вход избирательного усилителя является выходом логарифмического усилителя, управляющий вход ключа соедине с первым выходом генератора коммутирующих импульсов, отличающийся тем, что, с целью повышения точности его в работе, в него введены первый и второй преобразующе компенсирующие блоки, второй и третий коммутаторы и третий масштабный резистор, причем первый выход источника опорного напряжения через третий масштабный резистор подключен к первому входу второго коммутатора, второй вход которого соединен с выходом ключа, выход третьего, коммутатора подключен к входу избирательного усилителя, второй выход генератора коммутирующих импульсов соединен с управляющими входами первого, второго и третьего коммутаторов, первый выход генератора коммутирующих импульсов подключен к коммутирующему входу фазочувствительнаго выпрямителя и к первым входам первого и второго преобразующе-компенсирующих блоков, второй выход источника опорного напрян- ения соединен со вторыми входами первого и второго преобразующе-компенсирующих блоков, первый и второй выходы второго коммутатора подключены к третьим входам соответственно первого и второго преобразующе-компенсирующих блоков, четвертые входы которых сеодинены со вторым выходом генератора коммутирующих импульсов, пятые входы первого .и второго преобразующе-компенсирующих блоков подключены соответственно к первому и второму выходам первого коммутатора, выходы первого и второго .преобразующе-компенсирующих блоков соединены соответственно с первым и вторым входами третьего коммутатора. 2. Усилитель по п. 1, отличающийся тем, ЧТО-каждый преобразующе-компенсирующйй блок содержит первый и второй усилители,первый и второй ключевые элементы, оптрон, первый и второй интеграторы, логарифмирующий диод, четвертый, пятый и шестой масштабные резисторы, причем первый управляющий вход первого ключевого элемента является первым входом преобразующе-компенсирующего блока,вторым входом которого является вход первого ключевого элемента, вход первого усилителя является третьим входом преобразующе- компенсирующего блока, выходом которого является выход первого усилителя, который через четвертый масштабный резистор соединен с входом второго усилителя и первым выводом пятого масштабного резистора, второй вывод которого подключен к выходу первого ключевого элемента, вход первого усилителя через логарифмирующий диод соединен с выходом второго усилителя, управляющий вход второго ключевого элемента является четвертым входом преобразующе-компенсирующего блока, выход первого усилителя соединен с информационным входом второго ключевого элемента, управляющий вход которого подключей ко второму управляющему входу первого ключевого элемента, выход второго ключевого элемента через последовательно соединенные первый интегратор и шестой масштабный резистор подключен к входу второго усилителя,- вход второго интегратора является пятым входом преобразующекомпенсирующего блока, выходы второго интегратора соединены с выводами светодиода оптрона, выводы фоторезистора оптрона подключены к входу и выходу второго усилителя.

Источники информации, принятые во внимание при экспертизе

с. 171-172, рис. it.lSa.

кл. G Об G 7/2, 0.0б.80 (прототип).

Авторы

Даты

1982-06-07—Публикация

1980-11-12—Подача