1

Изобретение относится к цифровой вычислительной технике,в частности к устройствам управления ЦВМ.

Известно микропрограммное устройство управления, содержащее два блока памяти, три реги.стра, коммутаг , тор tn .

Недостатком этого устройства является низкая надежность, обусловленная отсутствием возможности перестройки д структуры при отказе блоков памяти.

Из известных перестраиваемых микропрограммных устройств управления наиболее близким к изобретению по ,- 15 технической сущности является перестраиваемое микропрограммное устройство управления, содержащее два запоминающих блока, два регистра адреса, два элемента И, элемент ИЛИ, 30 два коммутатора и два триггера управления t21.

.Недостатком устройства является низкая экономичность, обусловленная большим объемом не используемых массивов блоков памяти.

Цель изобретения - сокращение оборудования.

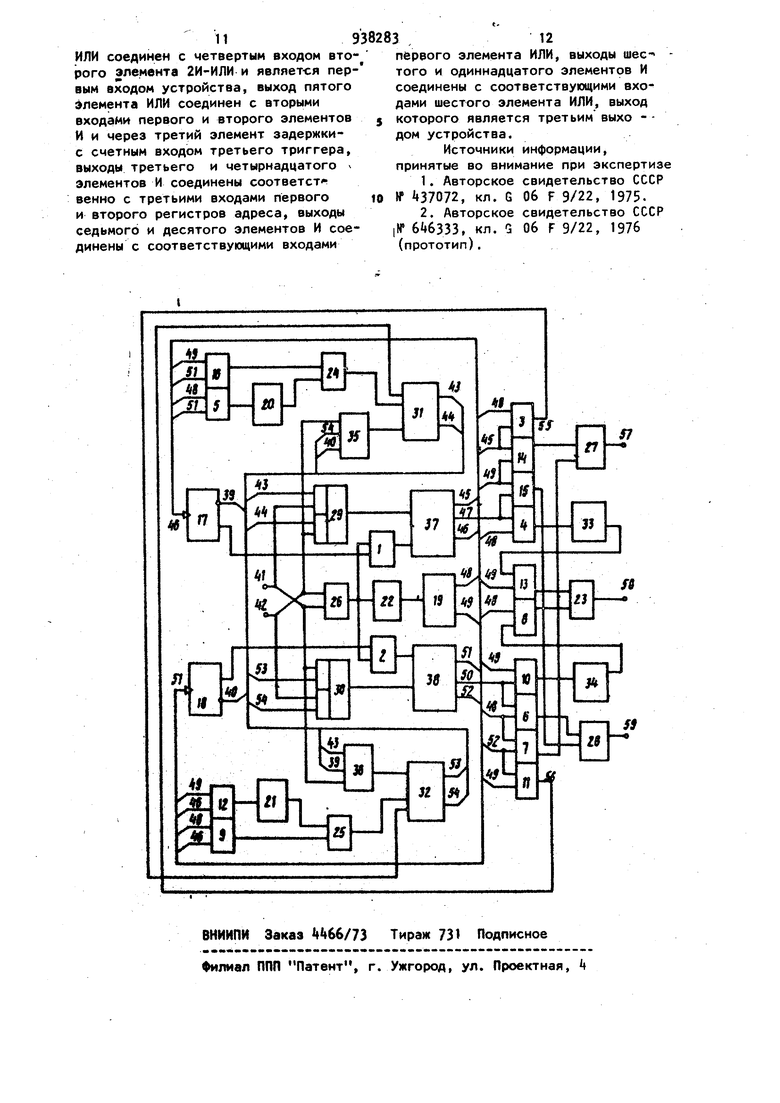

Поставленная цель достигается тем, что в устройство, содержащее два коммутатора, два регистра-адреса, два триггера, два элемента И, элемент ИЛИ и два блока памяти, первые выходы которых соединены с счетными входами соответственно первого и второго триггеров, единичные выходы которых соединены с первыми входами соответственно первого и второго элементов И, выходы которых соединены с первыми входами соответственно первого и второго блоков памяти, нулевые выходы первого и второго триггеров соединены с первыми входами соответственно первого и второго коммутаторов, выходы которых соединены с первыми входами соответственно первого и второго регистров адреса, первые выходы которых соедийены с вторым входом соответственн первого и второго коммутаторов, третьи входы которых соединены соответственно с первым и вторым входами устройства, выход первого элемента ИЛИ соединен с первым выходом ycjpoftcTsa, дополнительно содержит два регистра, пять элементов ИЛИ, четырнадцати элементов И, два элемента 2И-ИЛИ-, три элемента задержки и третий триггер; единичный выход которого соединен с первыми входам 1 с третьего по девятый элемент И, нулевой выход третьего триг гера соединен с первыми входами с десятого по шестнадцатый элемент И, выходы пятнадцатого и девятого элементов И соединены соответственно с первыми входами второго и трет его элементов ИЛИ, выходы которых ,соединены соответственно с вторыми входами второго и первого регистров адреса, вторые выходы которых соеди нены соответственно с первыми входа ми первого и второго элементов 2ИИЛИ, вторые входы которых соединены соответственно с первым и вторым входами устройства, третьи входы первого и второго элементов 2И-ИЛИ соединены соответственно с первыми выходами второго и первого регистров адреса, четвертые входы первого и второго элементов 2И-ИЛИ соединены соответственно с вторым и первым вх дами устройства, а выходы этих элементов соединены соответственно вторыми входами первого и второго блоков памяти, второй выход первого блока памяти соединен с вторыми вхо дами четвертого и одиннадцатого эле ментов И, второй выход второго блок памяти соединен с вторыми входами ш стого и тринадцатого элементов И, третий выход первого блока памяти соединен с вторыми входами третьего и десятого элементов И, третий выход второго блока памяти соединен с вторыми входами седьмого и четырнадцатого элементов И, выходы четвертого и тринадцатого элементо И с единены соответственно с входами первого и второго дополнительных ре гистров, выходы которых соединены соответственно с вторыми входами двенадцатого и пятого элементов И, выходы которых соединены с срответс вукхцими входами четвертого элемента ИЛИ, выход которого является . вторым выходом устройства, первый ВЫХОД первого блока памяти соединен с вторыми входами девятого и шестнадцатого элементов И, первый выход второго блока памяти соединен с вторыми входами восьмого и пятнадцатого элементов И, выход восьмого элемента И через первый элемент задержки соединен с вторым входом второго элемента ИЛИ, выход шестнадцатого элемента И через второй элемент задержки соединен с вторым входом третьего элемента ИЛИ, первый вход пятого элемента ИЛИ соединен с четвертым входом первого элемента 2И-ИЛИ . и является вторым входом устройства, второй вход пятого элемента ИЛИ соединен с четвертым входом второго элемента 2И-ИЛИ и является первым входом устройства, выход пятого элемента ИЛИ соединен с вторыми входами первого и второго элементов И и через третий элемент задержки соединен со счетным входом третьего триггера, ,выходы третьего и четырнадцатого элементов И соединены соответственно с третьими входами первого и второго регистров адреса, выходы седьмого и десятого элементов И соединены с соответствующими входами первого элемента ИЛИ, выходы шестого и одиннадцатого элементов И соединены с соответствующими входами шестого элемента ИЛИ, выход которого является третьим выходом устройства. Сущность изобретения состоит в сокращении объема блока памяти за счет разбиения микрокоманд на два сегмента, каждый из которых записывается в отдельной ячейке блока памяти, и осуществления считывания микрокоманды по частям за два такта. Первый сегмент каждой микрокоманды содержит поле адреса и операционное поле, в котором записана часть ее поля микроопераций. Остальная часть поля микроопераций микрокоманды содержится в адресном и операционном полях второго ее сегмента. Адрес Л первого сегмента i-и микрокоманды задается в поле адреса первого сегмента предыдущей (+1)-й микрокоманды, записанной в противоположном блоке памяти. Адрес А. второго сегмента i-й микрокоманды задается путем инвертирования первого сегмента в каждом такте считывание информации производится из обоих . блоков памяти; в одном блоке производится, считывание первого сегмента очередной -й микрокоманды, а в противоположном блоке - считывание второго сегмента предыдущей (i-1)-й микрокоманды. В следующем такте из первого блока считывается второй сегмент I-и микрокоманды, а из противоположного блока - первый сегмент следующей за ней (i+1)-и микрокоманды и т.д. Та часть поля микроопераций, кото рая содержится в операционном поле первого сегмента микрокоманды, запоминается и подается на выход устройства одновременно с считыванием остальной части поля микроопераций, т.е. второго сегмента микрокоманды. Благодаря этому быстродействие устройства сохраняется таким же, как и у известного устройства. При отказе одного из блоков памяти устройство переходит в режим рабо ты с одним блоко 1 памяти, наминая с той микрокоманды, адрес которой устанавливается в регистре адреса исправного блока по сигналу отказа другого блока памяти. На чертеже представлена функциональная схема устройства. Устройство содержит два элемента И 1 и 2, четырнадцать-дополнительных элементов И 3-16, два триггера 1 и 18, третий дополнительный триггер 19 три элемента 20-22 задержки, построенных, например, на О-триггерах, элeмeнt ИЛИ 23,пять дополнительных элементов ИЛИ , два элемента 2 И-ИЛИ 29 и 30, два регистра 31 И 32 адреса, два дополнительных регист ра 33 и первый 35 и второй Зб ко мутаторы, первый 37 и второй 38 блоки памяти. Кроме того, на чертеже обозначены нулевые выходы 39 и kQ соответственно первого 17 ивторого 18 триггеров первый 41 и второй 42 входы устройст ва, ВЫХОДЫ 43 и 44 соответственно пр мого и инверсного адреса второго рег стра 31 адреса, второй выход 45 (выход поля адреса) первого блока 37 памяти, первый выход 46 (выход не исправности) первого блока 37 памяти третий выход 47 (выход поля микроопераций) первого блока 37 памяти, единичный 48 и нулевой 49 выходы третьего триггера 19, третий выход 3 50 (выход поля микроопераций) второго блока ЗВ памяти, первый выход 5 (выход неисправности) второго блока 38 пaмятиJ второй выход 52 (выход поля адреса) второго блока 38 памяти, выходы 53 и S соответственно инверсного и прямого адреса первого регистра 32 адреса, выходы 55 и 56 адреса микрокоманд, записанных соответственно в первом 37 и в втором 38 блоках памя:ти, соответственно первого 57, второго 58 и третьего 59 выходов устройства. Устройство работает следующим образом. В исходном состоянии при отсутствии неисправностей в блоках памяти триггеры 17 и 18 установлены в единицу, триггер 19 - в нуль, в регистре 31 адреса записан адрес первой микрокоманды, в регистре 32 адреса и дополнительных регистрах 33 и З - нулевой код. При поступлении первого тактового импульса на вход 41 устройства с выхода 43 регистра 31 через элемент 2 И-ИЛИ 29 на блок 37 памяти подается прямое значение адреса первой микрокоманды,а с выхода 53 регистра 32 на блок 38 памяти подается инверсное значение нулевого кода, т.е. единичный код, которому в этом блоке соответствует пустая ячейка. Кроме того, импульс с входа 41 через элемент ИЛИ 26 поступает на элемент задержки 22 , а также через открытые триггерами 17 и 18 элементы И t и 2 поступает на считывающие входы блоков 37 и 38 памяти. К моменту выдачи информации из блоков памяти триггер 19 сигналом с элемента 22 задержки устанавливается в единичное состоя-, ниеи отпирает элементы И8, 6и 7,а также элементы И 3 и 4. Так как в регистре 34 установлен нулевой код, а в блоке 38 памяти будет опрошена пустая ячейка, через элементы И 8, 6 и.7 на выходы 58, 59 и 57 поступает нулевой код. Из блока 37 памяти будет считан первый сегмент первой микрокоманды. При этом адрес следующей, т.е. второй микрокоманды, с выхода 45 блока 37 памяти через открытый элемент И 3 поступает на регистр 32 адреса, а операционная часть первого сегмента первой микрокоманды через открытый элемент И 4 поступает на дополнительный регистр 33. 9 в следующем такте на вход 2 устройства поступает тактовый импульс, по которому на блок 37 памяти с выхода Al регистра 31 подается инверсный адрес первого сегмента первой микрокоманды, т.е. адрес ее второго сегмента,а на блок 38 памяти с выхода S регистра 32 подается прямой адрес первого сегмента второй микро команды. Далее аналогично первому такту происходит считывание информации из блоков памяти. К моменту ее выдачи из блоков триггер 19 устанавливается в нуль, запирая элементы ИЗ, , 8, 6и7и отпирая элементы И 1, 15, 13, 10 и 11. Благодаря этому содержимое адресного поля второго сегмента первой микрокоманды с выхода kS блока 37 памяти подается через элементы И 1 и ИЛИ 27 на выход 57 устройства, содержимое операционного поля этого сегмента подается через элементы И 15 и ИЛИ 28 на выход 59 устройства а содержимое дополнительного регистра 33 через элементы И 13 и ИЛИ 23на выход 58 устройства, т.е. на выходы устройства подаются полностью микрооперации первой микрокоманды Одновременно из блока 38 памяти буде считан первый сегмент второй микрокоманды. При этом адрес следующей за ней, т.е. третьей, микрокоманды с выхода 52 блока 38 памяти через открытый элемент И 11 поступит на регистр 31, а операционная масть первого сегмента второй микрокоманды через элемент И 10 поступит в дополнительный регистр З. Далее устройство функционирует аналогично описанному, осуществляя одновременно с считыванием первого {сегмента очередной микрокоманды из одного блока памяти считывание из второго сегмента предыдущей микрокоманды другого блока памяти и подавая микрооперации этой предыдущей микрокоманды на выходы устройства и т.д. При обнаружении искажений в считанном из блока 37 (38) памяти сегменте микрокоманды происходит перестройка на работу одним исправным блоком 38 (37) памяти.При этом на выходе (51) блока 37 (38) памяти формиру ется сигнал неисправности, который устанавливает в нуль триггеры 17 (18 запирая тем самым элемент И 1 (2), и разблокируя коммутатор 35 (36). Кроме того, этот сигнал поступает на 8 элементы И12и9 (16и5). Если искажение обранужено при считывании первого сегмента микрокоманды, сигналом с единичного (нулевого) выхода 8 (V9) триггера 19 будет открыт элемент И 9 (1б), через ко/орый сигнал неисправности поступит на элемент ИЛИ 25 (2) , а с него - на регистр 32 (31), в котором по этому сигналу установится фиксированный адрес, с которого начинается микропрогмамма функционирования устройства с одним неисправным блоком памяти. В следующем такте, согласно описанному, подается импульс на вход k2 (41) устройства, и из блока 38 (37) памяти происходит считывание первого сегмента микрокоманды, адрес которого был установлен в .регистре 32 (ЗО. Адрес следующей микрокоманды, содержащийся в считанном первом сегменте, через элемент И 11 (3) поступит на регистр 31 (32). В следующем такте подается импульс на вход t («2) устройства. При этом согласно описанному из памяти 38 (37) считывается второй сегмент микрокоманды по инверсному значению адреса, установленного на регистре 32 (31), а также происходит выдача микроопераций на выходы устройства. Одновременно адрес записанный в регистре 31 (32) через разблокированный коммутатор 36 (35) записывается в регистре 32 (ЗО. Далее из блока 38 (37) памяти происходит считывание первого сегмента очередной микрокоманды и содержимое его адресного поля устанавливается . на регистре 31 (32) и т.д. При этом считывание информации из блока 37 (38) памяти не происходит, так как элемент И 1 (2) заперт нулевым сигналом с единичного выхода триггера 1 (18). Если искажение обнаружено при считывании второго сегмента микрокоманды из блока 37 (38) памяти, сигнал неисправности с выхода 46 (50 блока 37 (38) памяти поступит на регистр 32 (31) через элемент И 12 (5), элемент 21 (20) задержки и элемент ИЛИ 25 (24) с задержкой на один такт. Задержка введена потому, что в следующем такте на блок 38 (37) памяти будет подаваться инверсное значение адреса, установленного в регистре 32 (31) и если перед этим в регистре установить фиксированный адрес,микро команда по этому адресу будет считана в обратном порядке : сначала будет считан ее второй сегмент, а потом первый, что приведет к нарушению работы устройства. Данное устрюйство по сравнению с известным, сохраняя способность к пе рестройке структуры, обеспечивает считывание микрокоманд из блоков памяти в виде двух сегментов, длина которых в два раза меньше длины микрокоманды. Это позволяет при постро ении блоков памяти устройства на БИС, количество ячеек в которых в два или более раз больше, чем количество микрокоманд, сократить в два раза количество БИС для блоков памяти устройства. Формула изобретения Микропрограммное устройство управ лeнияJ содержащее два коммутатора, два регистра адреса, два триггера, два элемента И, элемент ИЛИ и два блока памяти, первые выходы, которых соединены с счетными входами соответ ственно первого и Второго триггеров единичные выходы которых соединены с первыми входами соответственно пер вого и второго элементов И, выходы которых соединены с первыми входами соответственно первого и второго блоков памяти, нулевые выходы первого и второго триггеров соединены с первыми входами соответственно .первого и второго коммутаторов, выходы которых соединены с первыми вхо дами соответственно первого и второго регистров адреса, первые выходы которых соединены с вторым входом соответственно первого и второго коммутаторов, третьи входы которых соединены соответственно с первым и вторым входами устройства, выход пер вого элемента ИЛИ соединен с первым выходом устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит два регистра, пять элементов ИЛИ, четырнадцать элементов И, два элемента 2И-ИЛИ, три элемента задержки и третий триггерi единичный выход которого соединен с первыми входами с третьего по девятый элемент И нулевой выход третьего триггера соединен с первыми входами с десятого по шест надцатый элемент И, выходы пятнадцатого и девятого элементов И сое динены соответственно с первыми входами второго и третьего элементов ИЛИ, выходы которых соединены соответственно с вторыми входами второго и первого регистров адреса, вторые выходы которых соединены соответст: венно с первыми входами первого и второго элементов 2И-ИЛИ, вторые входы которых соединены соответственно с первым и вторым входами устройства, третьи входы первого и второго элементов 2И-ИЛИ соединены соответственно с первыми выходами второго и первого регистров адреса, четвертые входы первого и второго элементов 2И-ИЛИ соединены соответственно с вторым и первым входами устройства, а выходы этих элементов - соответственно с вторЫм и первым входами устройства, а выходы этих элементов соединены соответственно с вторыми входами первого и второго блоков памяти, второй выход первого блока памяти соединен с вторыми входами четвертого и одиннадцатого элементов И, второй выход второго, блока памяти соединен с вторыми входами шестого и тринадцатого элементов И, третий выход первого блока памяти соединен с вторыми входами третьего и десятого элементов И, третий выход второго блока памяти соединен с вторыми входами седьмого и четырнадцатого элементов И, выходы четвертого и тринадцатого элементов И соединены соответственно с входами первого и второго дополнительных регистров, выходы которых соединены соответственно с вторыми входами двенадцатого и пятого элементов И, .; выходы которых соединены с соответствующими входами четвертого элемента ИЛИ, выход которого является вторым выходом устройства, первый выход первого блока памяти соединен с вторыми входами девятого и шестнадцатого элементов И, первый выход второго блока памяти соединен с вторыми входами восьмого и пятнадцатого элементов И, выход восьмого элемента И через первый элемент задержки соединен с вторым входом . второго элемента ИЛИ, выход шестнадцатого элемента И через второй элемент задержки - с вторым входом третьего элемента ИЛИ, первый вхадпятого элемента ИЛИ соединен с четвертым входом первого элемента 2ИИЛИ и является вторым входом устройства, второй вход пятого элемента

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1980 |

|

SU888120A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

Авторы

Даты

1982-06-23—Публикация

1980-11-21—Подача