(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Микропрограммное устройство управления | 1981 |

|

SU993261A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

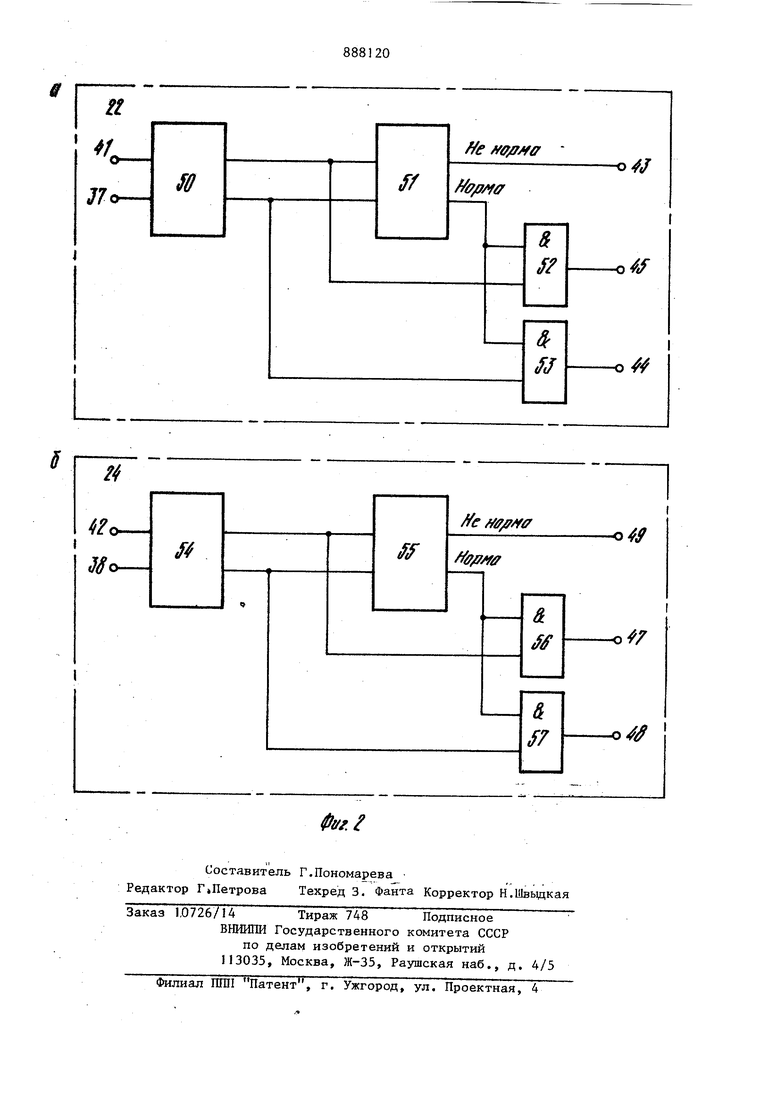

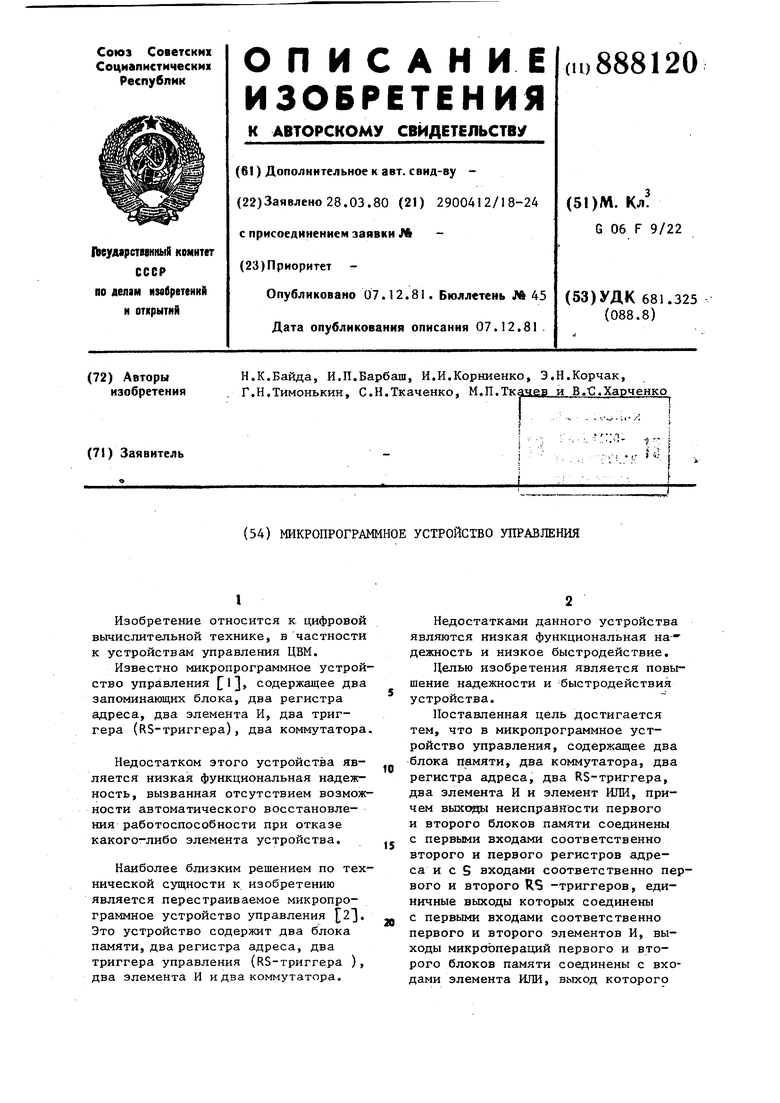

Изобретение относится к цифровой вычислительной технике, в частности к устройствам управления ЦВМ. Известно микропрограммное устройство управления flj, содержащее два запоминающих блока, два регистра адреса, два элемента И, два триггера (RS-триггера), два коммутатора Недостатком этого устройства является низкая функциональная надежность, вызванная отсутствием возможности автоматического восстановления работоспособности при отказе какого-либо элемента устройства. Наиболее близким решением по технической сущности к изобретению является перестраиваемое микропрограммное устройство управления . Это устройство содержит два блока памяти, два регистра адреса, два триггера управления (RS-триггера ), два элемента И и два коммутатора. Недостатками данного устройства являются низкая функциональная на-дежность и низкое быстродействие. Целью изобретения является повышение надежности и быстродействия устройства. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее два блока памяти, два коммутатора, два регистра адреса, два RS-триггера, два элемента И и элемент ИЛИ, причем выходы неисправности первого и второго блоков памяти соединены с первыми входами соответственно второго и первого регистров адреса и с S входами соответственно первого и второго RS -триггеров, единичные выходы которых соединены с первыми входами соответственно первого и второго элементов И, выходы микроопераций первого и второго блоков памяти соединены с входами элемента ИЛИ, выход которого является выходом устройства, первый выход первого коммутатора соединен с вторым входом первого регистра адреса, выход которого соединен с первым адресным входом второго коммутатора, первый и второй тактовые входы устройства соединены с вторыми входами соответственно первого и второго элементов И, нулевой выход первого RS -триггера соединен с первым управляющим входом первой группы входов второго коммутатора, нулевой выход второго R9-триггера соединен с первым входом первого коммутатора, введены дешифратор, два RS-триггера, шесть элементов И и четыре элемента ИЛИ,, причем единичные йыходы третьего и четвертого R5-триггеров соединены соответственно с первым управляющим входом первой группы и вторым управляющим входом второй группы первого коммутатора и соответственно с вторы управляющим входом первой группы и первым управляю0щм входом второй группы второго коммутатора, нулевые выходы третьего и четвертого К9-триг геров соединены соответственно с вторым управляющим входом первой гру пы и третьим управляющим входом второй группы первого коммутатора и соответственно с третьим управляющим входом первой группы и вторым управл ющим входом второй группы второго ко мутатора, единичные выходы первого и второго RS-триггеров соединены соот ветственно с третьим управляющим вхо дом первой группы и четвертым управл ющим входом второй группы первого ко мутатора и соответственно с четверты управляющим входом первой группы и третьим управляющим входом второй гр пы второго коммутатора, нулевой выхо первого R9 -триггера соединен с четвертым управляющим входом первой гру пы первого коммутатора и с первьм вх дом третьего элемента И, нулевой вых второго R9 -триггера соединен с пер вым входом четвертого элемента И и с четвертым управляющим входом второ группы второго коммутатора, первый и второй выходы которого соединены с адресными входами соответственно пер вого и второго блоков памяти, адресные выходы которых соединены соответ ственно с первым и вторым адресными входами первого коммутатора, второй выход которого соединен с вторым вхо дом второго регистра адреса, выход которого соединен с вторым адресным входом второго коммутатора, первый и второй тактовые входы устройства соединены с первыми входами соответственно пятого и шестого элементов И, с первыми входами соответственно седьмого и восьмого элементов И и с вторыми входами соответственно третьего и четвертого элементов И, выходы которых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, вторые входы которых соединены с выходами соответственно второго и первого элементов И, выход второго элемента ИЛИ соединен с входами считывания первого блока памяти и с первыми входами считывания первого и второго коммутаторов, выход третьего элемента ИЛИ соединен с входами считьшания второго блока памяти и вторыми входами считывания первого и второго коммутаторов, третьи входы первого и второго регистров адреса соединены с выходами неисправности соответственно первого и второго блоков памяти, выходы первого и второго регистров адреса соединены с вторыми входами соответственно восьмого и седьмого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, выход которого соединен с входом дешифратора, группа выходов которого соединена с группой входов пятого элемента ИЛИ, выход которого соединен с вторыми;входами пятого и шестого элементов И, выходы которых соединены с S входами соответственно четвертого и третьего R5-триггеров, первый и второй входы неисправности первого коммутатора соединены с выходами неисправности соответственно первого и второго блоков памяти. Сущностьизобретения состоит в повышении функциональной надежности устройства за счет обеспечения перестройки его структуры при отказе одного из регистров адреса и предотвращения включения в работу отказавшего ранее блока памяти, а также в повьш1ении быстродействия устройства при работе с отказавшим одним блоком памяти за счет сохранения рабочей частоты вьщачи микрокоманд на объект управления из другого блока памяти. Отказы регистров адресов обнаруживаются дешифратором и фиксиру11:)тся дополнительно введенными для этой цели третьим и четвертым RS-триггера5ми. Перестройка устройства при этом производится коммутаторами, которые обеспечивают запись адреса на исправ ный регистр адреса, а затем подачу этого адреса на нужный блок памяти. При этом за счет перестройки сохраня ется работоспособность устройства не только при одиночных отказах, т.е. при отказе или одного из блоков памяти, или одного из регистров адреса, но также и при двукратных отказах, т.е. при отказе одновременно одного из блоков памяти и одного из регистров. Это способствует повышению функциональной надежности устройства. Кроме того, при отказе обоих блоков памяти или обоих регистров второй коммутатор прекращает подачу адресов на блоки памяти, чем предотвращается работа неисправного блока памяти и вьщача им искаженньос микрокоманд на объект управления. Это также повьшает функциональную надежность устройства. Кроме того, при отказе одного из памяти прекращается подача на него импульсов считьшания. Импуль сы считывания, предназначенные для этого блока, подаются на исдравный блок памяти, за счет чего обеспечива ется надежное отключение отказавшего блока памяти и сохранение рабочей ча стоты подачи микрокоманд на объект управления. На фиг. 1 представлена функционал ная схема предлагаемого устройства, на фиг. 2 - функциональная схема пер вого и второго блоков памяти. Устройство содержит первый коммутатор 1, первый RS -триггер 2, первы 3 и второй 4 регистры адреса, второй RS-триггер 5, восьмой 6 и седьмой 7 элементы И, пятый элемент И 8, чет вертый элемент ИЛИ 9, шестой элемент И 10, четвертый tl5 -триггер 11, дешифратор 12, третий R9-триггер 13, пятый элемент ИЛИ 14, второй коммутатор 15, третий 16, первый 17, второй 18 и четвертый 19 элементы И, второй 20 и третий 21 элементы ИЛИ, первый блок 22 памяти, первый элемент ИЛИ 23, второй блок 24 памяти, первый и второй выходы 25, 26 пер- вого коммутатора единичный и нулевой выходы 27, 28 первого -триггера, выходы 29, 30 первого и второго регистров адреса, единичный и нулевой выходы 31 и 32 второго R5 04триггера, единичный и нулевой выходы 33 и 34 четвертого RS-триггера, единичные и нулевой выходы 35 и 36 третьего Я9 -триггера, первый и второй выходы 37 и 38 второго коммутатора, первый и второй тактовые входы 39 и 40 устройства, выходы 41 и 42 считывания соответственно с первого и с второго блоков памяти, первый выход 43 неисправности первого блока памяти, выход 44 адреса блока 22, выход 45 микрооперации блока 22 выход 46 устройства, выход 47 , микрооперации блока 24, третий выход 48 адреса блока 24, выход 49 неисправности блока 24, Блок памяти содержит запоминающий узел 50 (54), узел контроля на четность 51 (55), блоки элементов И 52, 53, запоминающий узел 54, узел контроля на четность 55, блоки элементов И 56 и 57. Устройство управления работает следующим образом./ В исходном состоянии при отсутствии неисправностей в блоках памяти и в регистрах адреса триггеры 2, 5, 11, 13 находятся в нулевом состоянии, на выходах 43 и 49 блоков 22 и 24 и на выходе дешифратора 12 значение сигнала соответствует логическому нулю, в регистре 4 (3) записан адрес микрокоманды, подлежащей считыванию, на входы 39 и 40 устройства поочередно подаются тактовые импульсы. Так как триггер 2 (. 5 ) находится в нулевом состоянии, то он разрешает прохождение тактового импульса с входа 39 (40) через элемент И 16 (19) и далее через элемент ИЛИ 20 (21) на считывающий вход блока 22 (24) и входы коммутаторов 1 и 15. По этому сигналу коммутатор 15 подает адрес микрокоманды,: подлежащей считыванию, с регистра 4 (З) на выход 37 (38) и далее - на адресный вход блока 22 (24),. где происходит считывание микрокоманды по этому адресу. На выходе 45 (47) блока 22 (24) появляются сигналы микроопераций считанной микрокоманды, которые через элемент ИЛИ 23 подаются на выход 46, а адрес следующей микрокоманды подается с выхода 44 (48) через коммутатор 1 на регистр 3 (4). Далее поступает тактовый импульс на вход 40 (39)/ и устройство продолжает работу, аналогично описанному выше. 7 При отказе одного из блоков памя ти или одного из регистров, или же одновременно одного из блоков памяти и одного из регистров происходит перестройка структуры устройства е целью восстановления его работоспособности , При отказе одного из блоков памяти, например 22 (24), считьюание микрокоманд происходит только с : блока 24 (22). Происходит это следующим образом На первый выход 43 (49) отказавшего блока 22 (24) подается сигнал, по -которому в регистрах 3 и 4 устанавливается фиксированный адрес, а триггер 2 (5) устанавливается в единичное состояние, запирая элемент И 16 (19) и отпирая элемент И 17 (18) для прохождения тактовых импульсов с входа 39 (40) устройства на блок 24 (22), а также перестраивая работу коммутаторов 1 и 15. Очередной тактовый импульс, поступая на вход 40 (39) устройства, через элемент ИЛИ 21 (20) поступает на считывающий вход блока 24 (22 и на входы коммутаторов 1 и 15. По этому сигналу коммутатор 15 подает фиксированный адрес, записанный в регистре 4 (З), на выход 38 (37) и с него - на адресный вход блока 24 (22), где происходит .считывание микрокоманды по этому адресу. Адрес следзпощей микрокоманды, содержащийся в поле адреса считанной микрокоманды, подается с выхода 48 (44) бл ка 24 (22) через коммутатор 1 на ре гистр 4 (з). Тактовый импульс с вхо да 39 (40) поступает через элемент И 17 (18) на элемент ИЛИ 21 (20), в результате чего происходит считывание микрокоманды из блока 24 (22 по адресу, установленному в регистр 4 ( 3, а также происходит запись в него адреса очередной микрокоманды с выхода 48 (44) блока 24 (22). Таким образом, обеспечивается сохранение прежней частоты следования микрокоманд на выходе 46 устройства. При отказе одного из регистров адреса и исправных блоках памяти пе рестройка происходит следующим образом. При подаче тактового импульса на вход 39 (40) устройства откры вается элемент И 7 (6), который подает сигнал с выхода регистра 4 (3 на дешифратор 12. Дешифратор, обна . 8 ружив запрещенное состояние регистра 4 (з), подает на один из .своих выходов сигнал, который через элемент ИЛИ 14 и элемент И 8 (10), открытый тактовым импульсом с входа 39 (40) устройства, поступает на 5 вход триггера 11 (13) и устанавливает его в единичное состояние. Далее отличие работы устройства .от полностью неисправного заключается лишь в том, что адрес микрокоманды, считанный из блока памяти, записывается коммутатором 1 каждый раз в исправный регистр 3 (4), ас него подается коммутатором 15 на нужньш блок памяти: с регистра 3 (4) при подаче тактового импульса на вход 39 адрес подается на блок 24 (22), а при подаче тактового импульса на вход 40 адрес подается на блок 22 (24). При наличии отказа одновременно в регистре 3 (4) и в блоке 22 (24) триггеры 2 и 13 (5 и 11) устанавливаются вышеописанным способом в единичное состояние, а в регистре 3 (4) по сигналу с выхода 43 (49) блоблока 22 (24) устанавливается фиксированный адрес. Далее устройство работает так же, как и в вьшгеописанном случае, когда оба регистра исправны, а отказал лишь блок 22 (24), так как при этом не происходит подача адресов на регистр 3 (4). При наличии отказа одновременно в блоке 22 (24 ) и в регистре 4(3) триггеры 2 и II (5 и 13 описанным выше способом устанавливаются в единичное состояние, а триггеры 5 и 13 {2 и 11) остаются в нулевом состоянии. Кроме того, в регистрах 3 и 4 устанавливается фиксированный адрес, При поступлении тактового импульса на вход 40 ( 39 ) устройства этого импульса проходит через элемент И 19 ( 16 и элемент ИЛИ 21 (20) на коммутаторы 1 и 15 и на блок 24 (.22), в результате чего адрес из регистра 3 (4) подается коммутатором 15 на вькод 38, а с него - на блок 24 (22), в котором происходит считывание микрокоманды по этому адресу. Адрес следующей микрокоманды, содержащийся в поле адреса считанной микрокоманды, подается с выхода 48 ( 44 через коммутатор 1 на регистр 3 (4). При поступлении тактового импульса на вход 39 (40) устройства этот импульс поступает через элемент И 17 (18 и элемент ИЛИ 21 (.20) на коммутаторы 1 и 15 и блок 24 (22) в результа чего аналогично вышеописанному ад су с регистра 3 (4) поступает на 24 (22), происходит считывание мик команды и запись содержимого ее п адреса в регистр 3 (47. При наличии отказа одновременно регистрах 3 и 4 или одновременно в Длоках 22 и 24 коммутатор 15 блок руется, прекращая подачу адресов регистров 3 и 4 на блоки памяти, результате чего устройство прекращ ет работу. Данное устройство обеспечивает восстановление своей работоспособ ности не только при отказе одного из блоков памяти, но и при отказе одного из регистров адреса или одновременно одного из регистров адреса и одного из блоков памяти, а также предотвращает включение в работу неисправного блока памяти при наличии отказов одновременно в двух блоках памяти, за счет чего достигается повышение функциональной надежности устройства. Кроме того, при отказе одного из блоков памяти считывание микрокоманд с исправного блока памяти происходит в 2 раза чаще, чем в случае, когда оба блока исправны. Это позволяет при наличии отказа в одном из блоков памяти повысить в 2 раза быстродействие устройства по сравнению с прототипом. Формула изобретения Микропрограммное устройство управления, содержащее два коммутатора, два регистра, два RS-триггера, два злемента И, элемент ИЛИ и два блока памяти неисправности, выходы, которых соединены с первыми входами соответственно второго и первого регистров адреса и с S входами соответственно первого и второго R.5-триггеров, единичные выходы которьпс соединены с первыми входами соответственно первого и второго злементов И, выходы микроопераций первого и второго блоков памяти соединены с входами зле мента ИЛИ, выход которого является выходом устройства, первый выход первого коммутатора соединен с вторым входом первого регистра ад0реса, выход которого соединен с первым адресньм входом второго коммутатора, первый и второй тактовые входы устройства соединены с вторыми вхог дами соответственно первого и второго элементов И, нулевой выход первого и9 триггера соединен с первым управляющим входом первой группы входов второго коммутатора, а нулевой выход второго RS -триггера соединен с первым входом первого коммутатора, о т л и ч а ющ е е с я тем, что, с целью повышения надежности и быстродействия, в него введены дешифратор, шесть элементов И, четыре элемента ИЛИ и два RS-триггера, единичные выходы которых соединены соответственно с первым управляющим входом первой группы и вторьм управляющим входом второй группы первого коммутатора и соответственно с вторым управляющим входом первой группы и первым, управляющим входом второй группы второго коммутатора, а нулевые выходы указанных триггеров соединены соответственно с вторым управляющим входом первой группы и третьим управляющим входом второй группы первого коммутатора и соответственно с третьим управляющим входом первой группы и вторым управляющим входом второй группы второго коммутатора, единичные выходы первого и второго KS -триггеров соединены соответственно с третьим управляющим входом первой группы и четвертым управляющим входом второй группы первого коммутатора и соответственно с четвертым управляющим входом первой группы и третьим управляющим входом второй группывторого коммутатора, нулевой выход первого RS -триггера соединен с четвертым- управляющим входом первой группы первого коммутатора и с первым входом третьего элемента И, нулевой выход второго RS -триггера соединен с первым входом четвертого элемента И и с четвертым управляющим входом второй группы второго коммутатора, первый и второй выходы которого соединены с адресными входами соответственно первого и второго блоков памяти, адресные выходы которых соединены соответственно с первым и вторым адресньми входами первого коммутатора, второй выход которого соединен с вторым входом второго регистра адреса, выход которого соединен с вторым адресным входом второго коммутатора.

первый и второй тактовые входы устройства соединены с первыми входами соответственно пятого и шестого элементов И, с первыми входами соответственно седьмого и восьмого элементов Икс вторыми входами соответственно третьего и четвертого элементов И, выходы которых соединены с первыми входами соответственно второго и третьего элементов ИЛИ, -вторые входы которых соединены с выхода1ми соответственно второг и первого элементов И, выход второго элемента ИЛИ соединен с входами считывания первого блока памяти и с первыми входами считьгоания первого и второго коммутаторов, выход третьего элемента ИЛИ соединен с входами, считывания второго блока-памяти и вторыми входами считывания первого, и второго коммутаторов, третьи входы первого и второго регистров адреса соединены с выходами неисправности соответственно первого и второго блоков памяти, вы88120 . 12 .

ходы первого и второго регистров адреса соединены с вторыми выходами соответственно восьмого и седьмого элементов И, выходы которых соединены с входами четвертого элемента ИЛИ, выход которого соединен с . входом дешифратора, группа выходов которого соединена с группой входов питого элемента ИЛИ, выход кото 0 рого соединен с вторыми входами пятого и шестого элементов И, выходы которых соединены с 5 входамр соответственно четвертого и третьего Й&-триггеров, а первый и второй

15 входы неисправности первого коммутатора соединены с выходами неисправности соответственно первого и второго блоков памяти.

Источники информации,

20 принятые во внимание при экспертизе

//

/

№

J7of/e ffff/7 ff

/

//

//

//

8c //

Авторы

Даты

1981-12-07—Публикация

1980-03-28—Подача