элементов И второй группы, выходы которых соединены с второй группой информационных входов первого регистра адреса, выход ошибки второго блока памяти соединен с единичным входом четвертого триггера управления, первым входом пятого и инверсным входом шестого элементов И и с инверсными входами элементов И второй группы, единичный выход первого триггера управления соединен с первым входом седьмого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен, с входом считывания второго блока памяти и через первый элемент задержки с прямым входом шестого элемента И, выход которого соединен с первым входом второго элемента. ИЛИ, выход второго элемента ИЛИ соединен с единичным входом второго и нулевым входом третьего триггеров управления, единичный выход третьего триггера управления через второй элемент задержки соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом второго триггера управления, нулевой выход которого соединен с вторы входом седьмого элемента И, третий вход которого соединен с вторым управляющим входом устройства, единичный выход второго триггера управления соединен с первым входом восьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход KOTopioro соединен с входом считывания первого блока памяти и через третий элемент задержки с прямым входом четвертого элемента И, выход четвертого элемента И соединен с вторым входом второго элемента ИЛИ, выход которого соединен с единичным входом; первого и нулевым входом четвертого

триггеров управления, единичный выход четвертого дриггера управления через четвертый элемент задержки соединен с вторым входом пятого элемента И, выход которого соединен со счетным входом первого триггера управления, нулевой выход которого соединен с вторым входом восьмого элемента И, третий вход которого соединен с первым управляющим входом устройства, нулевые выходы третьего и четвертого триггеров управления соединены соответственно с третьими входами первого и второго элементов И, выходы которых

, соединены соответственно с вторыми входами первого и третьего элементов ИЛИ.

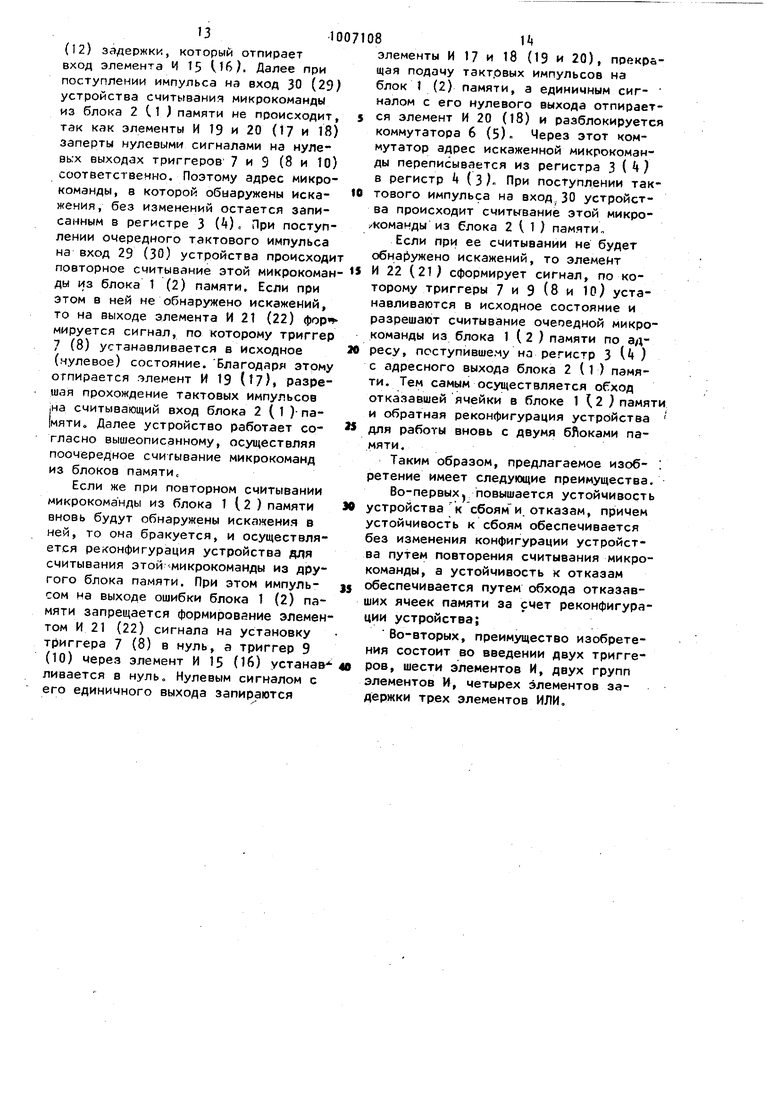

2. Устройство по П.1, отличающееся тем, что блок памя ти содержит запоминающую матрицу,

первый, второй и тре.тий элементы задержки, сумматор по модулю два, элемент И и группу элементов И, причем

; адресный и управляющий входы блока

памяти соединены соответственно с

адресным и управляющими входами запоминающей матрицы, управляющий вход блока памяти через первый элемент задержки соединен с первым входом элемента И, выход которого соединен с инверсными входами всех элементов И

группы и является выходом ошибки блока памяти, адресные и числовые выходы запоминающей матрицы соединены с входами сумматора по модулю два и через второй и третий элементы задержки соединены соответственно с адресным выходом блока памяти и с входами эяегментов И группы, выходы элементов И группы являются выходами операндаблока памяти, выход сумматора по нодулю два соединен с вторым входом

1 элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1016782A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310818A1 |

| Микропрограммное устройство управления | 1980 |

|

SU888120A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

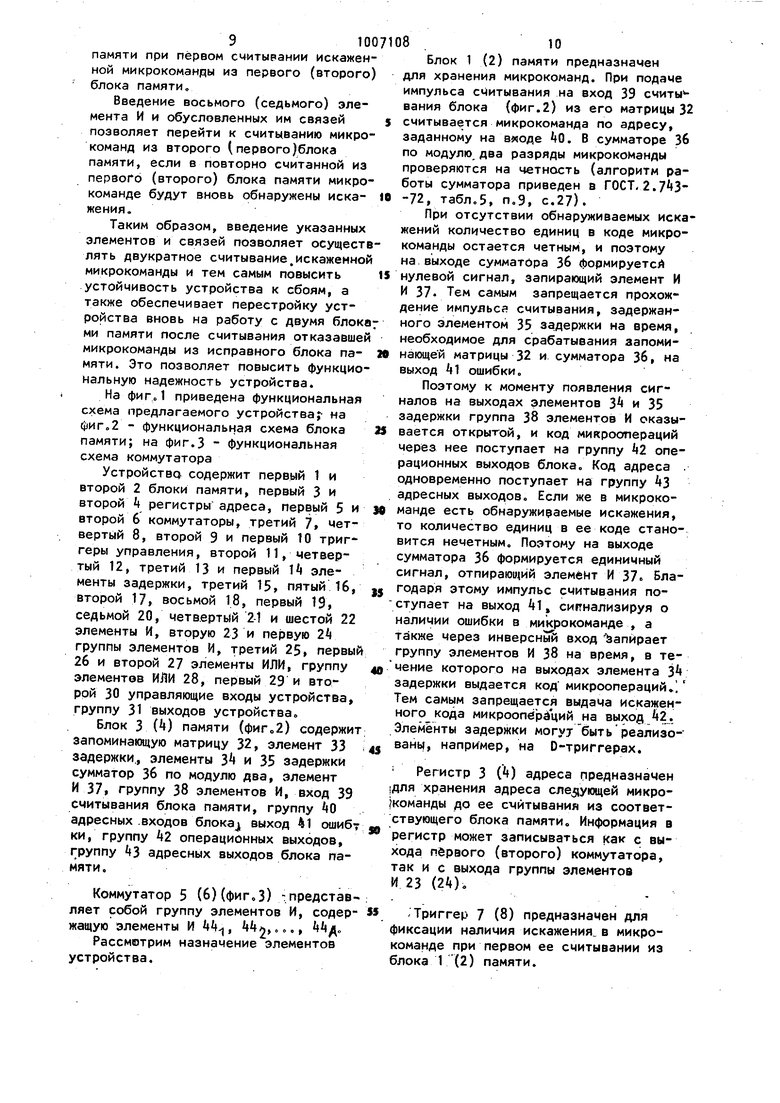

1. РЕКОНФИГУРИРУЕМрЕ УСТРОЙСТВО С ПРОГРАММНЫМ УПРАВЛЕНИЕМ, содержащее первый и второй блоки памяти, первый и второй регистры адреса, первый и второй коммутаторы, первый и второй элементы И, первый и второй триггеры управления, группу элементов ИЛИ, причем нулевой выход первого триггера управления соединен с первым управляющим входом первого коммутатора, группа выходов которого соединена с первой группой информационных входов первого регистра адреса, первый выход первого регистра адреса соединен с группой адресных входов первого блока памяти, нулевой выход второго триггера управления соединен с первым управляющим входом второго коммутатора, группа выходов которого соединена с первой группой информационных входов второго регистра адреса, первый выход второго регистра адреса соединен с группой адресных входов второго блока памяти, группы информационных выходов первого и второго блоков памяти соединены с соответствующим входом соответствующего элемента ИЛИ группы, выходы элементов ИЛИ группы являются группой выходов устройства, первый и второй управляющие входы устройства соединены с вторыми управляющими входами второго и первого коммутаторов соответственно, вторые выходы первого и второго регистров адреса соединены соответственно с информационными входами второго и первого коммутаторов, единичные выходы первого и второго триггеров управления соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены с вторым и первым управляющими входами устройства соответственно, отличающееся тем, что, с целью повышения надежности -S в устройство дополнительно введены тре тий и четвертый триггеры управления, третий, четвертый, пятый, шестой, седь мой и восьмой элементы И, первая и вторая группы элементов И, первый, второй, третий и четвертый элементы задержки, первый, второй и третий элео менты ИЛИ, причем группа адресных вы00 ходов первого блока памяти соединена с входами элементов И первой группы, выходы которых соединены с второй группой информационных входов второго регистра адреса, выход ошибки первого блока памяти соединен с единичным входом третьего триггера управления, первым входом третьего и инверсным входом четвертого элементом И и с инверсными входами элементов И первой группы, группа адресных вхсдоь второго блока памяти соединена с входами

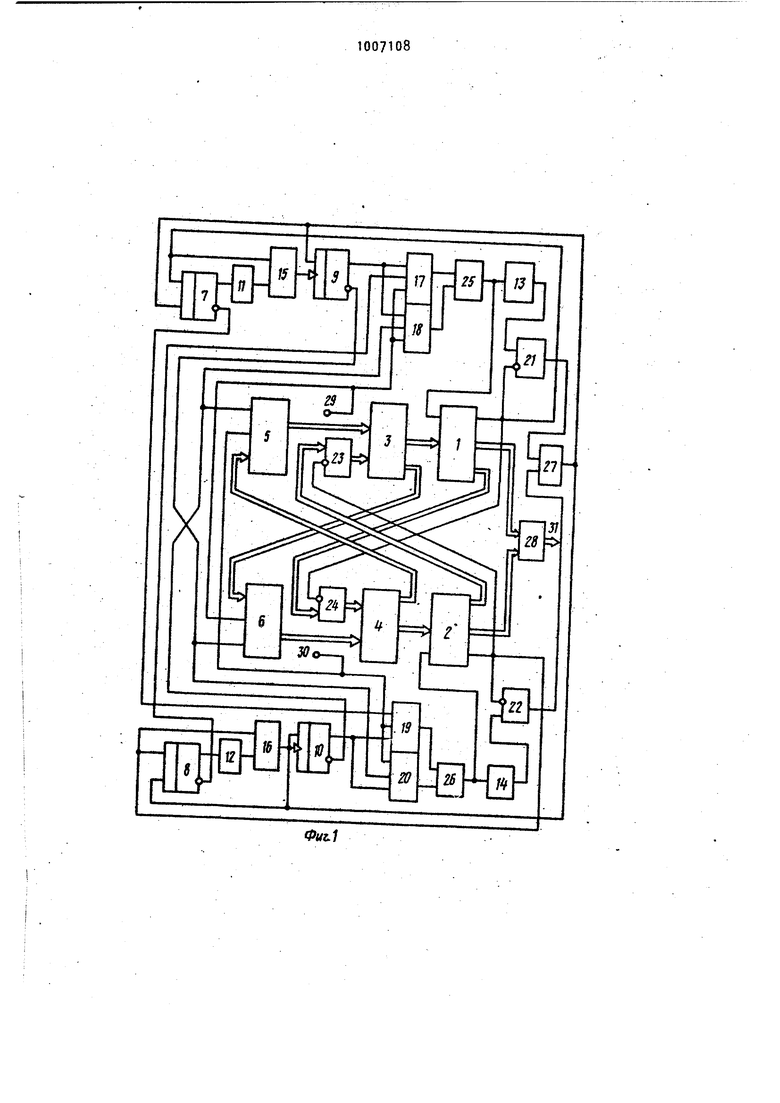

1 ,

Изобретение относится к цифровой вычислительной технике, в частности к устройствам управления ЭВМ.

Известно микропрограммное устройство управления, содержащее Два блока памяти, два коммутатора, два триг гера, два регистра адреса и два элемента И, причем первые входы блоков памяти соединены с первыми выходами

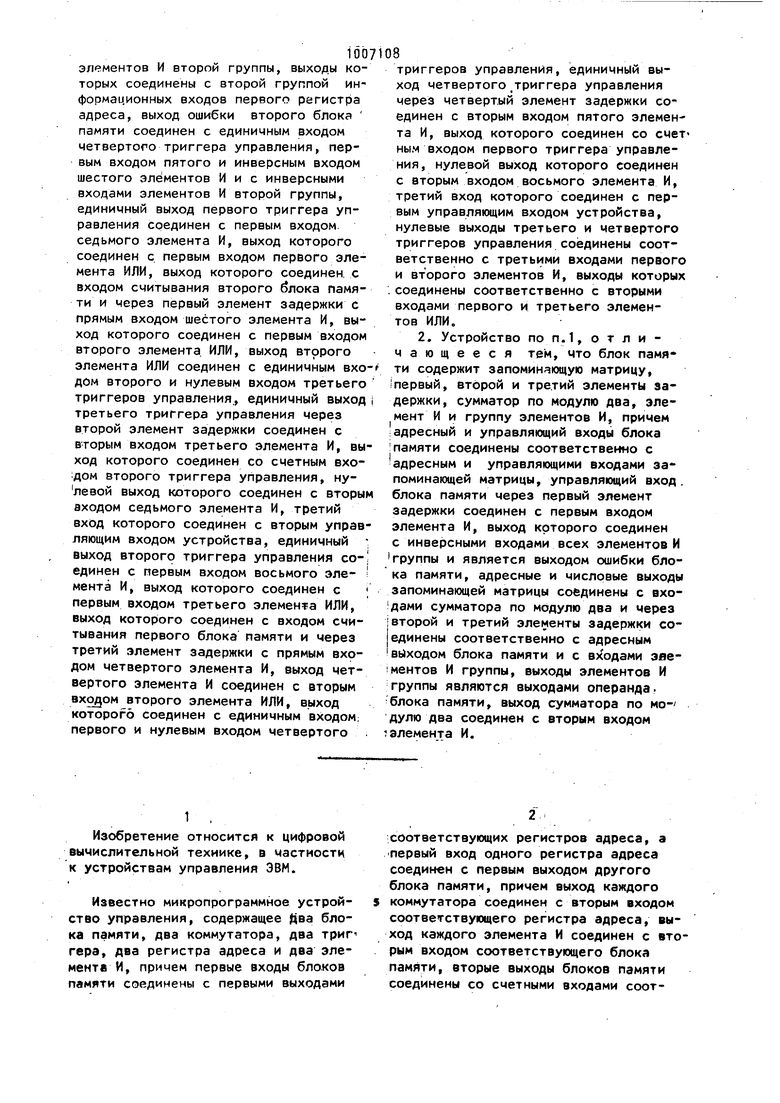

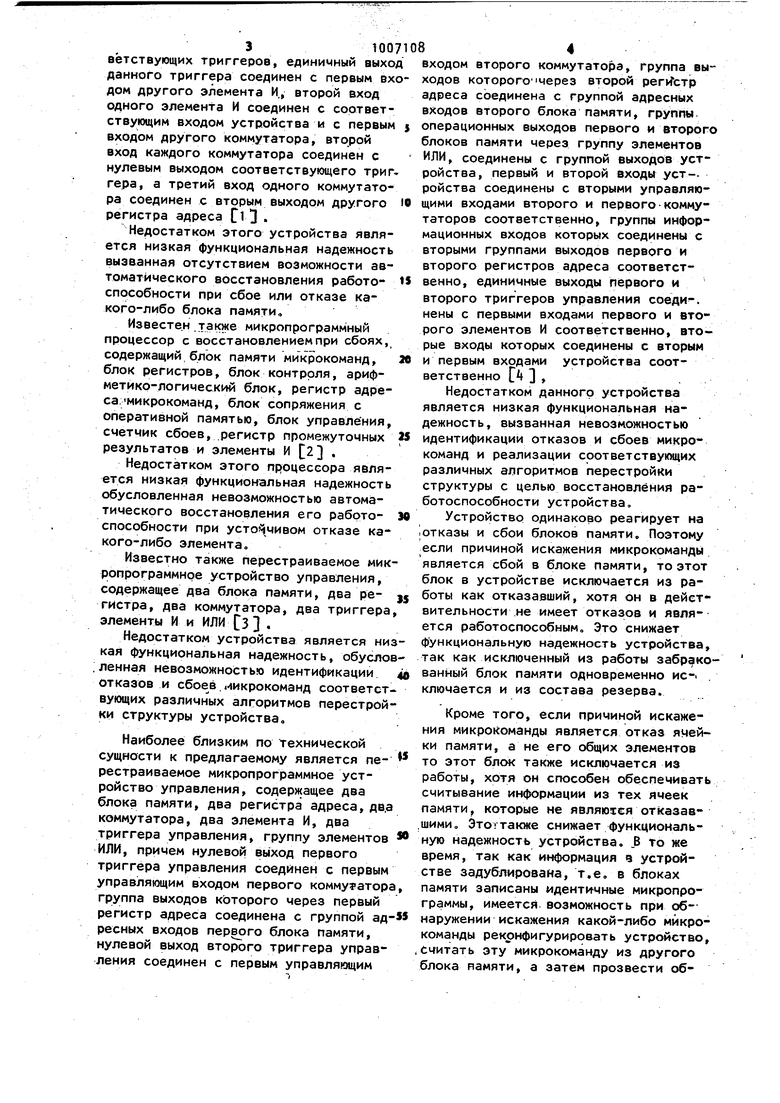

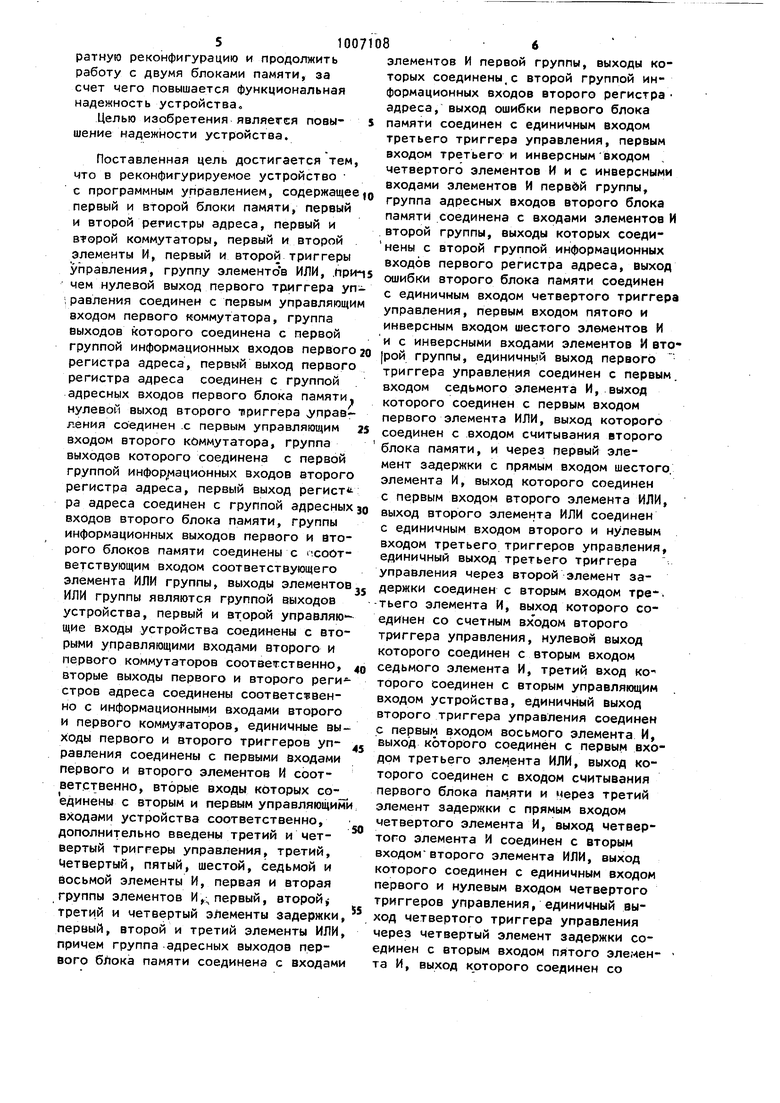

соответствующих регистров адреса, а Первый вход одного регистра адреса соедин«н с первым выходом другого блока памяти, причем выход каждого коммутатора соединен с вторым входом соответствующего регистра адреса, выход каждого элемента И соединен с вторым входом соответствующего блока памяти, вторые выходы блоков памяти соединены со счетными входами соответствующих триггеров, единичный выход данного триггера соединен с первым вхо дом другого элемента И, второй вход одного элемента И соединен с соответствующим входом устройства и с первым входом другого коммутатора, второй вход каждого коммутатора соединен с нулевым выходом соответствующего триггера, а третий вход одного коммутатора соединен с вторым выходом другого регистра адреса Cl3 Недостатком этого устройства является низкая функциональная надежность вызванная отсутствием возможности автоматического восстановления работоспособности при сбое или отказе какого-либо блока памяти. Известен.также микропрограммный процессор с восстановлением при сбоях, содержащий блок памяти микрокоманд, блок регистров, блок контроля, арифметико-логический блок, регистр адреса, микрокоманд, блок сопряжения с оперативной памятью, блок управления, счетчик сбоев, регистр промежуточных результатов и элементы И 2 . Недостатком этого процессора является низкая функциональная надежность обусловленная невозможностью автоматического восстановления его работоспособности при усто чивом отказе какого-либо элемента. Известно также перестраиваемое мик ропрограммное устройство управления, содержащее два блока памяти, два регистра, два коммутатора, два триггера элементы И и ИЛИ СЗ . Недостатком устройства является ни кая функциональная надежность, обусло ленная невозможностью идентификации отказов и сбоев.микрокоманд соответст вукицих различных алгоритмов перестрой ки структуры устройства. Наиболее близким по технической сущности к предлагаемому является перестраиваемое микропрограммное устройство управления, содержащее два блока памяти, два регистра адреса, дв.а коммутатора, два элемента И, два триггера управления, группу элементов ИЛИ, причем нулевой вЫход первого триггера управления соединен с первым управляющим входом первого коммутатор группа выходов которого через первый регистр адреса соединена с группой ад ресных входов первого блока памяти, нулевой выход второго триггера управления соединен с первым управлящим ходом второго коммутато|эа, группа вы одов которого-через второй pervfcTp дреса соединена с группой адресных ходов второго блока памяти, группы, перационных выходов первого и второго локов памяти через группу элементов ИЛИ, соединены с группой выходов устройства, первый и второй входы устройства соединены с вторыми управляюими входами второго и первогокоммутаторов соответственно, группы информационных входов которых соединены с вторыми группами выходов первого и второго регистров адреса соответственно, единичные выходы первого и второго триггеров управления соеди-. нены с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены с вторым и первым входами устройства соответственно СА 3,. Недостатком данного устройства является низкая функциональная надежность, вызванная невозможностью идентификации отказов и сбоев микрокоманд и реализации соответствующих различных алгоритмов перестройки структуры с целью восстановления работоспособности устройства. Устройство одинаково реагирует на iотказы и сбои блоков памяти. Поэтому если причиной искажения микрокоманды является сбой в блоке памяти, то этот блок в устройстве исключается из работы как отказавший, хотя он в действительности не имеет отка31оа и является работоспособным. Это снижает функциональную надежность устройства, так как исключенный из работы забракованный блок памяти одновременно ис-i . ключается и из состава резерва. Кроме того, если причиной искажения микрокоманды является отказ ячейки памяти, а не его общих элементов то этот блок также исключается из работы, хотя он способен обеспечивать считывание информации из тех ячеек памяти, которые не являются отказав,шими. Это;также снижает функциональную надежность устройства. .В то же время, так как информация в устройстве задублирована, т.е. в блоках памяти записаны иденти чные микропрограммы, имеется возможность при об-наружении искажения какой-либо микрокоманды рекрнфигурировать устройство, ,считать эту микрокоманду из другого блока памяти, а затем прозвести обратную реконфигурацию и продолжить работу с двумя блоками памяти, за счет чего повышается функциональная надежность устройства. Целью изобретения является повышение надежности устройства. Поставленная цель достигается тем, что в реконфигурируемое устройство с программным управлением, содержащее первый и второй блоки памяти, первый и второй регистры адреса, первый и второй коммутаторы, первый и второй элементы И, первый и второй триггеры уЬравления, группу элементов ИЛИ, ,при чем нулевой выход первого триггера уп ;равления соединен с первым управляющи входом первого коммутатора, группа выходов которого соединена с первой группой информационных входов первого регистра адреса, первый выход первого регистра адреса соединен с группой адресных входов первого блока памяти, нулевой выход второго триггера управления соединен .с первым управляющим входом второго кйммутатора, группа выходов которого соединена с первой группой инфор/ ационных входов второго регистра адреса, первый выход регист ра адреса соединен с группой адресных входов второго блока памяти, группы информационных выходов первого и второго блоков памяти соединены с псоответствующим входом соответствующего элемента ИЛИ группы, выходы элементов ИЛИ группы являются группой выходов устройства, первый и второй управляющие входы устройства соединены с вторыми управляющими входами второго и первого коммутаторов соответственно, вторые выходы первого и второго реги стров адреса соединены соответственно с информационными входами второго и первого коммуя аторов, единичные выходы первого и второго триггеров управления соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых со- единены с вторым и первым управляющими входами устройства соответственно, дополнительно введены третий и четвертый триггеры управления, третий, Цетвертый, пятый, шестой, седьмой и восьмой элементы И, первая и вторая группы элементов И,; первый, второй,третий и четвертый элементы задержки, первый, второй и третий элементы ИЛИ, причем группа адресных выходов первого бЛока памяти соединена с входами элементов И первой группы, выходы которых соединены.с второй группой информационных входов второго регистра адреса, выход ошибки первого блока памяти соединен с единичным входом третьего триггера управления, первым входом третьего и инверсным входом четвертого элементов И и с инверсными входами элементов И первдй группы, группа адресных входов второго блока памяти соединена с входами элементов И второй группы, выходы которых соединены с второй группой информационных входов первого регистра адреса, выход ошибки второго блока памяти соединен С единичным входом четвертого триггера управления, первым входом пятого и инверсным входом шестого элементов И и с инверсными входами элементов И группы, единичный выход первого триггера управления соединен с первым, входом седьмого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с входом считывания второго блока памяти, и через первый элемент задержки с прямым входом шестого, элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход второго элемента ИЛИ соединен с единичным входом второго и нулевым входом третьего триггеров управления, единичный выход третьего триггера управления через второй элемент задержки соединен с вторым входом тре-. тьего элемента И, выход которого соединен со счетным входом второго триггера управления, нулевой выход которого соединен с вторым входом седьмого элемента И, третий вход ко торого соединен с вторым управляющим входом устройства, единичный выход второго триггера управления соединен с первым входом восьмого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, выход которого соединен с входом считывания первого блока памяти и ерез третий элемент задержки с прямым входом четвертого элемента И, выход четвертого элемента И соединен с вторым входомвторого элемента ИЛИ, выход которого соединен с единичным входом первого и нулевым входом четвертого триггеров управления, единичный выход четвертого триггера управления через четвертый элемент задержки соединен с вторым входом пятого элемента И, выход которого соединен со 7100 счетным входом первого триггера управ ления, нулевой выход которого соединен с вторым входом восьмого элемента И, третий вход которого соединен . с первым управляющим входом устройства, нулевые выходы третьего и четвертого триггеров управления соединены соответственно с третьими входами пер вого ивторого элементов И, выходы которых соединены соответственно с вторыми входами первого и третьего элементов ИЛИ, Блок памяти содержит запоминающую матрицу, первый, второй и третий элементы задержки, сумматор по модулю два, элемент И и группу элементов И, причем адресный и управляющий входы блока памяти соединены соответственно с адресным и управляюи ими входами запоминающей матрицы, управляющий вход блока памяти через первый элемент задержки соединен с первым входом элемента И, выход которого соеди нен с инверсными входами всех элементов И группы и является выходом ошибки блока памяти, адресные и числовые выходы запоминающей матрицы соединены с входами сумматора по модулю два и через второй и ,третий элементы задержки соединены соответственно с ад ресныМ выходом блока памяти и с входами элементов И группы, выходы элементов И группы являются выходами операнда блока памяти, выход суммато по модулю, два соединен с вторым входом элемента И. Тущность изобретения состоит в по вышении функциональной надежности ус ройства путем обеспечения устойчивос ти к сбоям и обхода отказавших ячеек памяти путем реконфигурации , Устойчивость к сбоям обеспечивается за счет того, что считывание микрокоманды, в которой обнаружено искажение, осуществляется дважды, и лишь при повторении искажений микрокоманда бракуется и осуществляется реконфигурация устройства- для считывания этой микрокоманды из другого бпока памяти. Обход отказавшей ячейки памяти осуществляется путем реконфигурации устройства для работы с другим блоко памяти, осуществления считывания забракованной микрокоманды из этого блока, после чего осуществляется обратная реконфигурация для работы вновь с двумя блоками памяти. Введен .8 . ретьего (четвертого) триггера управения и соединение его единичного хода с третьим выходом первого (второго блока памяти предназначено для иксации наличия искажения б микрокоманде при первом ее считывании из лока памяти. Введение второго (четвертого элeмента задержки и обусловленных им связей предназначено для обеспечения отпирания третьего (шестого) элемента И лишь после того, как закончится импульс, установивший третий .(четвертый) триггер управления в единицу. Введение третьего (пятого) элеменta И и обусловленных им связей предназначено для подачи сигнала нассчетный вход второго (первого) триггера управления при наличии искажений в повторно ;считанной микрокоманде. Введение второй (первой) группы элементов И и обусловленных ею связей позволяет обеспечить подачу адресного поля микрокоманды, считанной из второго (первого) блока памяти, на первый (второй) регистр адре.са лишь при усдоВИИ, что в ней не обнаружено искажений. Введение четвертого (шестого) элемента И и обусловленных им связей поз воляет при отсутствии искажений в микрокоманде, считанной из первого (второго.) блока памяти, устанавливать триггеры управления в исходное состояние. Введение второго элемента ИЛИ позволяет устанавливать триггеры управления в исходное состояние при отсутствии искажений в микрокоманде, считанной из любого блока памяти. Введение третьего (первого элемента задержки и обусловленных им связей позволяет разрешить формирование сигнала на установку триггеров управления а исходное состояние лишь после того, как на выходе ошибки первого (второго) блока памяти будет сформирован результат контроля считанной из него микрокоманды. Введение третьего (первого) элемента ИЛИ и обусловленных им связей предназначено для формирования сигналов считывания микрокоманд из первого (второго) блока памяти. Соединение нулевого выхода третьего (четвертого) триггера управления с третьим одом первого (второго) элемента И позволяет прекратить считывание ИЗвторого (первого) блока памяти при первом СЧИТЫРЭНИИ искажен ной микрокоманды из первого (второго блока памяти. Введение восьмого (седьмого) элемента И и обусловленных им связей позволяет перейти к считыванию микро команд из второго (, первого )блока памяти, если в повторно считанной из первого (второго) блока памяти микро команде будут вновь обнаружены искажения. Таким образом, введение указанных элементов и связей позволяет осущест лять двукратное считывание,искаженно микрокоманды и тем самым повысить устойчивость устройства к сбоям, а также обеспечивает перестройку устройства вновь на работу с двумя блока ми памяти после считывания отказавшей микрокоманды из исправного блока памяти. Это позволяет повысить функциональную надежность устройства. На фиго1 приведена функциональная схема предлагаемого устройстваf на фиг.2 - функциональная схема блока памяти; на фиг.З - функциональная схема коммутатора Устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 регистры адреса, первый 5 и второй 6 коммутаторы, третий 7, четвертый 8, второй 9 и первый 10 триггеры управления, второй 11, четвертый 12, третий 13 и первый Ti элементы задержки, третий 15, пятый 16, второй 17, восьмой 18, первый 19, седьмой 20, четвертый 2-1 и шестой 22 элементы И, вторую 23 и первую 2 группь элементов И, третий 25, первый 26 и второй 27 элементы ИЛИ, группу элементов ИЛИ 28, первый 29 и вторрй 30 управляющие входы устройства, группу 31 выходов устройства. Блок 3 () памяти (фиГо2) содержит запоминающую матрицу 32, элемент 33 задержки., элементы З и 35 задержки сумматор 36 по модулю два, элемент И 37, группу 38 элементов И, вход 39 считывания блока памяти, группу АО адресных .входов блокад выход 41 ошибт ки, группу 42 операционных выходов, группу адресных выходов блока памяти. Коммутатор 5 (6) (фиг.З) .представляет собой группу элементов И, содержащую элементы И 4(, .. «Д Рассмотрим назначение элементов устройства. 10 8 Блок 1 (2) памяти предназначен для хранения микрокоманд. При подаче импульса считывания на вход 39 считы вания блока (фиг.2) из его матрицы 32 считывается микрокоманда по адресу, заданному на вжоде 40. В сумматоре Зб по модулю, два разряды микрокоманды проверяются на четность (алгоритм работы сумматора приведен в .743 -72, табл.5, п,9, с,27). При отсутствии обнаруживаемых искажений количество единиц в коде микрокоманды остается четным, и поэтому на выходе сумматора Зб формируете нулевой сигнал, запирающий элемент И И 37. Тем самым запрещается прохождение импуяься считывания, задержанного элементом 35 задержки на время, необходимое для срабатывания аапоминающей матрицы 32 и сумматора Зб, на выход 41 ошибки. Поэтому к моменту появления сигналов на выходах элементов 34 и 35 задержки группа 38 элементов И оказывается открыткой, и код микроопераций через нее поступает на группу 42 операционных выходов блока. Код адреса . одновременно поступает на группу 43 адресных выходов. Если же в микрокоманде есть обнаруживаемые искажения, то количество единиц в ее коде становится нечетным. Поэтому на выходе сумматора 36 формируется единичный сигнал, отпирающий элемент И 37. Благодаря этому импульс считывания поступает на выход 41, сигнализируя о наличии ошибки в микрокоманде , а также через инверснь вход Ъапйрает группу элементов И 38 на время, в течение которого на выходах элемента 34 задержки выдается код микроопераций. Тем самым запрещается выдача искаженного кода микроопбрёций на выход 4. Элементы задержки могут быть реализованц, например, на D-триггерах. Регистр 3 (4) адреса предназначен 1для хранения адреса следующей микрокоманды до ее считывания из соответствующего блока памяти. Информация в регистр может записываться ка с выхода первого (второго) коммутатора, так и с выхода группы элементов И 23 (24). Триггер 7 (В) предназначен для фиксации наличия искажения, в микрокоманде при первом ее считывании из блока 1 (2) памяти. и10 Триггер 9 (10) предназначен для фиксации наличия искажения а микрокоманде при ее повторном считываний из блока 1 (2) памяти. Элемент И 15 (t6) предназначен для управления триггером 9 (10). Элемент 11 (12) задержки предназ начен для отпирания элемента И после того, как закончится импульс, установивший триггер 7 (8) в единицу В качестве этих элементов могут быть использованы О-триггеры. Коммутатор 5 (6) предназначен для подачи адреса следующей микрокоманды из регистра (3) адреса в регистр 3 (А), когда при двукратном считывании из блока 1 (2) памяти микрокоманда вновь оказывается искаженной. Группа элементов И 23 (2) предназначена для подачи адреса следующей микрокоманды с адресного выхода блока 2 (1) памяти на регистр 3 С) лишь при отсутствии искажений в микрокоманде, считанной из этого блока памяти. Группа элементов ИЛИ 28 предназна чена для подачи сигналов микроопераций с блоков 1 и 2 памяти на выход устройства. Элемент И 21 (22) прее4назначен для формирования сигнала на устаноВ|к триггеров в исходное состояние, при отсутствии искажений а микрокоманде, считанной из блока 1 (2) памяти. Элемент ИЛИ 27 предназначен для формирования сигналов на установку триггеров в исходное состояние при отсутствии искажений в микрокоманде , считанной из блоков 1 и 2 памят, а Элементы И 17 (19) и 18 (20) пред назначены для управления подачей импульсов считывания на блок 1 (2) памяти. Элемент ИЛИ 25 (26) предназначен для формирования импульсов на входе считывания блока памяти 1 (2), Э Элемент задержки 13 (I) предназначен для разрешения формирования сигнала на установку триггеров 7-tO р исходное состояние лишь после того как на выходе ошибки блока 1 2 ) памяти будет сформирован результат контроля считанной из блока памяти микрокоманды. В качестве этого элемента может быть испольаован D-триггер. 8 Устройство работает следующим обазом. В исходном состоянии при отсутствии отказов в блоках 1 и 2 памяти риггеры 7 и 8 управления установлены а нуль, триггеры 9 и 10 - в единицу, на выходах ошибки блоков 1 и 2 памяти значение сигнала соответствует логическому нулю, на входы 29 и 30 устройства поочередно подаются тактовые импульсы, в регистре 3 W адреса, записан адрес микрокоманды, подлежащей считыванию. Очередной тактовый импульс с входа 29 (30) поступает через элемент И 17 (19), открытый сигналом с единичного выхода триггера 9 (10), и через элемент ИЛИ 25 (26) на считывающий вход блока 1 (2) памяти, осуществляя считывание из него микрокоманды по адресу, записанному, в регистре 3 W адреса. Сигналы микроопераций считанной микрокоманды с выхода блока 1 (2) памяти через группу элементов ИЛИ 28 подаются на группу 31 выходов устройства, а адрес следующей микрокоманды при отсутствии сигнала на выходе ошибки подается через элемент И 2k (25) на регистр k( ) адреса. Kpoмe того, при отсутствии сигнала ошибки элемент И 21 (22) остается отккрытым нулевым значением сигнала на его инверсном входе, в результате чего та,ктрвый импульс через элемент 13(Н) задержки поступает на вход элемента И 21 и через элемент ИЛИ 27 устанавливает триггеры 7-10 в исходное состояние. При поступлении тактового импульса на вход 30 (29) устройства происходит считывание очередной микрокод манды из блока 2 (1) памяти и т,д. При обнаружении искажения в микрокоманде, считанной из блока 1 (2) памяти на его выходе ошибки формируется импульс, который зйпирает группу элементов И 2k (23), запрещая запись адреса следующей микрокоманды в peгистр k (3) адреса, с выхода блока 1 (2) памяти, а также устанавливает триггер 7 (8) в единицу. Сигналом с нулевогр выхода триггера 7 (8) зарирается элемент И 19 (17), прекращая подачу тактовых импульсов на блок 2(1 ) памяти. По окончании импульса на выходе ошибки блока 1 (2) памяти появляется сигнал на выходе элемента 11 (12) задержки, который отпирает вход элемента И 15 (.f). Палее при поступлении импульса нэ вход 30 (29) устройства считывания микрокоманды из блока 2 Cl ) памяти не происходит, так как элементы И 19 и 20 (17 и 18) заперты нулевыми сигналами на нулевых выходах триггеров 7 и 9 (8 и 10) соответственно. Поэтому адрес микрокоманды, в которой обыаружены искажения, без изменений остается записанным в регистре 3 (). При поступлении очередного тактового импульса на вход 29 (30) устройства происходи повторное считывание этой микрокоман ды из блока 1 (2) памяти. Если при этом в ней не обнаружено искажений, то на выходе элемента И 21 (22) фор мируется сигнал, по которому триггер 7 (8) устанавливается в исходное (нулевое) состояние. Благодаря этому отпирается .элемент И 19 (7), разрешая прохождение тактовых импульсов на считывающий вход блока 2(1)- памяти. Далее устройство работает согласно вышеописанному, осуществляя поочередное считывание микрокоманд из блоков памяти. Если же при повторном считывании микрокоманды из блока 1(2) памяти вновь будут обнаружены искажения в ней, то она бракуется, и осуществляется реконфигурация устройства для считывания этой микрокоманды из другого блока памяти. При этом импульсом на выходе ошибки блока 1 (2) памяти запрещается формирование элементом И 21 (22) сигнала на установку триггера 7 (8) в нуль, а триггер 9 (10) через элемент И 15 (16) устанав ливается в нуль. Нулевым сигналом с его единичного выхода запираются элементы И 17 и 18 (19 и 20), прекращая подачу такт.овых импульсов на блок 1 (2) памяти, а единичным сигналом с его нулевого выхода отпирается элемент И 20 (18) и разблокируется коммутатора 6 (5). Через этот коммутатор адрес искаженной микрокоманды переписывается из регистра 3 ( } в регистр t ( 3). При поступлении тактового импульса на вход,30 устройства происходит считы вание этой микрооманды из блока 2 1 1 ) памяти, Если при ее считывании не будет обна| ужено искажений, то элемент 22 (2 сформирует сигнал, по которому триггеры 7 и 9 (8 и Ю) устанавливаются в исходное состояние и разрешают считывание очеоедной микрокоманды из блока 1(2) памяти по адресу, поступившему на регистр 3 ( ) с адресного выхода блока 2 ( Г) памяти. Тем самым осуществляется обход отказавшей ячейки в блоке ) памяти и обратная реконфигурация устройства для работы вновь с двумя бЛоками памяти. Таким образом, предлагаемое изоб- : ретение имеет следующие преимущества. Во-первыхJ повышается устойчивость устройства к сбоями отказам, причем устойчивость к сбоям обеспечивается без изменения конфигурации устройства путем повторения считывания микрокоманды, а устойчивость к отказам обеспечивается путем обхода отказавших ячеек памяти за счет реконфигурации устройства; Во-вторых, преимущество изобретения состоит во введении двух триггеРОВ, шести элементов И, двух групп элементов И, четырех элементов задержки трех элементов ИЛИ,

39 о-

40

/ l

O

J

34

4J

35 t

.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| i | |||

Авторы

Даты

1983-03-23—Публикация

1981-10-12—Подача