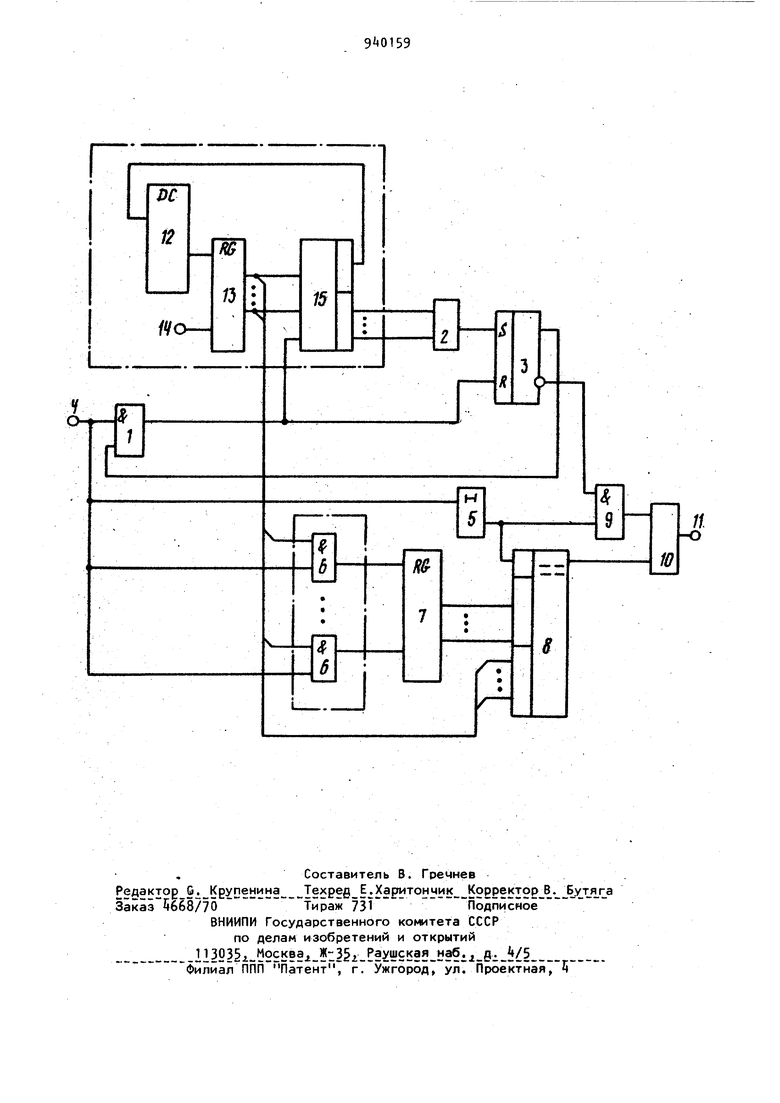

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации средств контроля управляющих автоматов, применяемых в цифровых вычислительных машинах и различных устройст вах цифровой автоматики. Известны устройства для контроля микропрограммного автомата, содержащие элементы И, ИЛИ, НЕ, задержки, триггер tl. Недостатками указанных устройств являются значительные затраты контрольного оборудования, что приводит к недостаточной надежности самих схе контроля, а также низкая оперативность обнаружения ошибки. Наиболее близким по технической сущности к предлагаемому является устройство для контроля микропрограм много автомата, содержащее триггер, элемент задержки и элементы И и ИЛИ, причем вход устройства подключен к первому входу первого элемента И, вы ход которого соединен с входом синхронизации контролируемого автомата и нулевым входом триггера, единичный выход которого соединен с вторым входом первого элемента И, а нулевой выход - с первым входом второго элемента И, входы элемента ИЛИ соединены с группой выходов контролируемого микропрограммного автомата {2. Недостатками известного устройства являются низкие функциональные возможности , обусловленные низкими полнотой и оперативностью контроля. Низкая полнота контроля вызвана ограниченным классом обнаружения ошибок. В известном устройстве обнаруживаются только ошибки, вызванные физичес.кими отказами элементов контролируемого автомата, и не обнаруживаются ошибки программирования. Низкая оперативность контроля обусловлена формированием сигнала ошибки в следующем такте после обнаружения неисправности. Цель.изобретения - расширение функциональных возможностей устройст ва за счет обнаружения ошибок програ мирования и, формирования сигнала эши ки в такте ее возникновения. Поставленная цель достигается тем что в устройство, содержащее дешифра тор, выходы которого соединены с г.ру пой входов регистра адреса, выходы к торого соединены с группой входов бл ка памяти №1крокоманд,первый элемент ИЛИ, два элемента И, триггер и элемент .задержки, причем выход первого элемента И соединен с нулевым входом Триггера и с входом блока памяти микрокоманд, синхронизирующий вход устройства соединен с первым вх дом первого элемента И, второй вход которого соединен с единичным выходом триггера, нулевой выход которого соединен с первым входом второго элемента И, входы первого элемента ИЛИ соединены соответственно с выходами микроопераций блока памяти микрокоманд, введены второй элеиент ИЛИ, группа элементов И, буфер:ный регистр и схема сравнения, приче первые входы элементов И группы соединены с первой группой входов схемы сравнения и с выходами регистра адреса, первый вход первого элемента И соединен с входом элемента задержки и вторыми входами элементов И группы, выходы которых соединены с соответствующими входами буферного регистра, выходы которого со единены с второй группой входов схемы сравнения, выход которой соединен с первым входом второго элемента ИЛИ, выход которого является выходом устройства, а второй вход соединен с входом схемы сравнения и выходом элемента задержки, выход первого элемента ИЛИ соединен с единичным входом триггера. На чертеже приведена функциональная схема устройства. В состав устройства входят первый элемент И 1, первый элемент ИЛИ 2, триггер 3 синхронизирующий вход , элемент 5 задержки, группа 6 элементов И, буферный регистр 7. схема 8 сравнения,второй элемент И 9, второй элемент ИЛИ 10, выход 11 устройства дешифратор 12, регистр 13 адреса, вход k установки начального адреса блок 15 памяти микрокоманд. Устройство позволяет контролировать ошибки программирования типа тупик, приводящие к зацикливанию программы на каком-либо адресе. Такие ошибки обнаруживаются при сравнении адресных частей предыдущей и последующей микрокоманд контролируемого автомата. В устройстве контролируется ход программы следукяцим образом. Очередной тактовый импульс поступает через Синхронизирующий вход k устройства на вторые входы элементов И 6 группы и разрешает запись адреса микрокоманды с выходов регистра 13 адреса на буферный регистр 7. Этот же им пульс, поступивший через первый элемент И 1 на блок 15 памяти микрокоманд, вызывает считывание очередной микрокоманды. По окончании считывания микрокоманды на регистре 13 адреса устанавливается адрес очередной микрокоманды, и тактовый импульс , .вызварший считывание микрокоманды, через элемент 5 задержки поступает .на схему сравнения. Происходит сравнение адреса предыдущей микрокоманды, записанного на буферном регистре 7, и адреса очередной микрокоманды. Поступающей на схему 8 сравнения с выходом регистра 13 адреса. При равенстве указанных адресов схема сравнения формирует сигнал ошибки, который через второй элемент ИЛИ 10 поступает на выход 11 устройства. Крнтроль ошибок, вызванных физическими отказами элементов устройства, заключается в проверке наличия хотя бы одного сигнала микрооперации в операционной части микрокоманды контролируемого устройства. При отсутствии сигналов на выходах микроопераций устройство формирует сигнал ошибки. . В устройстве микропрограммного управления обнаруживается отсутствие сигналов микроопераций на выходе блока 15 памяти следующим обрезом. Каждый тактовый импульс -через первый элемент И 1 устанавливает триггер 3 в нулевое состояние и поступает на блок 15 памяти микрокоманд, вызывая считывание очередной микрокоманды. Сигналы микроопераций операционной части микрокоманды через первый элемент ИЛИ 2 устанавливают триггер 3 в единичное состояние и запрещают прохождение тактового импульса, задержанного элементом 5 задержки , через второй элемент И 9 для формирования сигнала ошибки. Элемент 5 задерж5 gi

ки должен обеспечить задержку тактового импульса на время считывания микрокоманды и установки триггера 3, сигналами микроопераций в единичное состояние.

При отсутствии сигналов на выходах микроопераций блока 15 к моменту прихода на второй элемент И 9 задержанного тактового импульса триггер 3 находится в нулевом состоянии. На выходе второго элемента И 9 появляется си гнал ошибки, который через второй элемент ИЛИ 10 проходит на выход 11 устройства.

Таким образом, устройство позволяет расширить класс обнаруживаемых ошибок и повысить оперативность контроля, что позволяет строить более эффективные средства контроля микропрограммных автоматов.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее дешифратор, выходы которого соединены с группой входов регистра здреса, выходы которого соединены с группой входов блока памяти микрокоманд, первый: элемент ИЛИ, два элемента И, триггер и элемент задержки, причем выход первого элемента И соединен с нулевым входом триггера и с входом блока памяти микрокоманд, синхронизирующий вход устройства соединен с первым входом первого элемента И,второй вход которого соединен с единич96

ным выходом триггера, нулевой выход которого соединен с первым входом второго элемента И. входы первого элемента ИЛИ соединены соответственно с выходами микооопеоаций блока памяти микоокоманд, отли чающееся тем, что, с целью расширения фунч:циональных возможностей за счет обнаружения ошибок программирования и формирова1« я сигнала ошибки в такте ее возникновения, в него введены второй элемент ИЛИ, группа элементов И, буферный регистр и схема сравнения, причем первые входы элементов И группы соединены с первой группой входов схемы сравнения и с выходами регистра адреса,первый вход первого элемента И соединен с входом элемента задержки и вторыми входами элементов И группы, выходы которых соединены с соответствующими входами буферного регистра, выходы которого соединены с второй группой входов схемы сравнения, выход которой соединен с первым входом второго элемента ИЛИ, выход которого является выходом устройства, а вход соединен с входом схемы сравнения и выходом элемента задержки, выход первого элемента ИЛИ соединен с единичным входом триггера.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 35756, кл. G 06 F 11/10, 1969.

2,Авторское свидетельство СССР 391563, кл. G 06 F 11/02, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропрограммного блока управления | 1984 |

|

SU1203526A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1270772A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Устройство микропрограммного управления с контролем | 1990 |

|

SU1805466A1 |

| Микропрограммное устройство управления с контролем | 1980 |

|

SU920727A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

Авторы

Даты

1982-06-30—Публикация

1980-12-26—Подача