(5) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ

I

Изобретение относится к области .автоматики и вычислительной технике и может быть использовано при построении устройств программного и микропрограммного управления с высокой достоверностью функционирования.

Известно микропрограммное устройство с контролем переходов, содержащее регистры, блок памяти мик-. рокоманд, логические элементы D1.

Недостатком указанного устройства является большая вероятность пропуска сигнала ошибки.

Наиболее близким к предложенному по технической сущности и достигаемому эффекту является микропрограммное устройство с контролем, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, регистр сдвига, блок управления переходами, блок сравнения и элемент И, причем выход регистра адреса соединен со входами блока памяти, выход которого соединен со входами регистра микрокоманд, первый выход которого соединен с первым входом регистра адреса, второй выход соединен с первыми входами первого элемента И и блока сравнения, третий выход соединен с первым входом блока управления переходами, выЯод которого соединен со вторым входом регистра адреса и первым входом сдвигающего регистра, выход которого соединен со вторым входом блока сравнения, третий вход которого соединен с четвертым выходом регистра микрокоманд, пятый выход которого соединен с вторым входом блока управления переходами, а также инверсным входом первого элемента И, выход кс торого является выходом микроопераций устройства.

Недостатками данного устройства являются низкие оперативность и достоверность контроля.

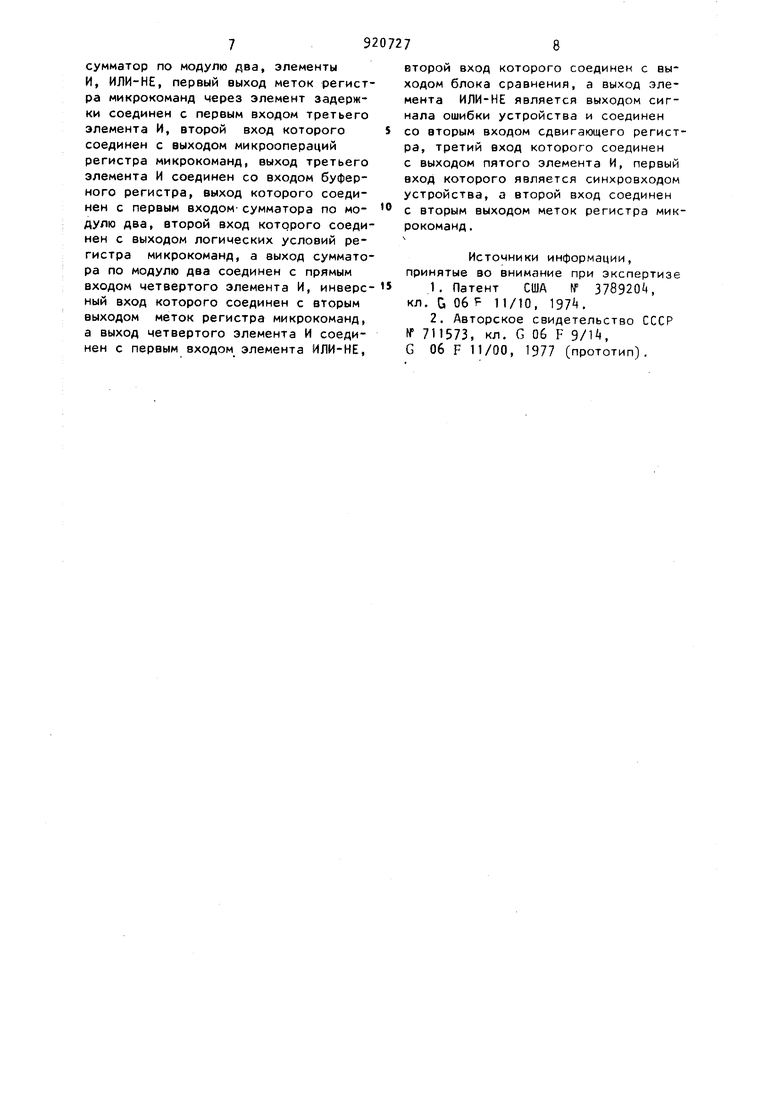

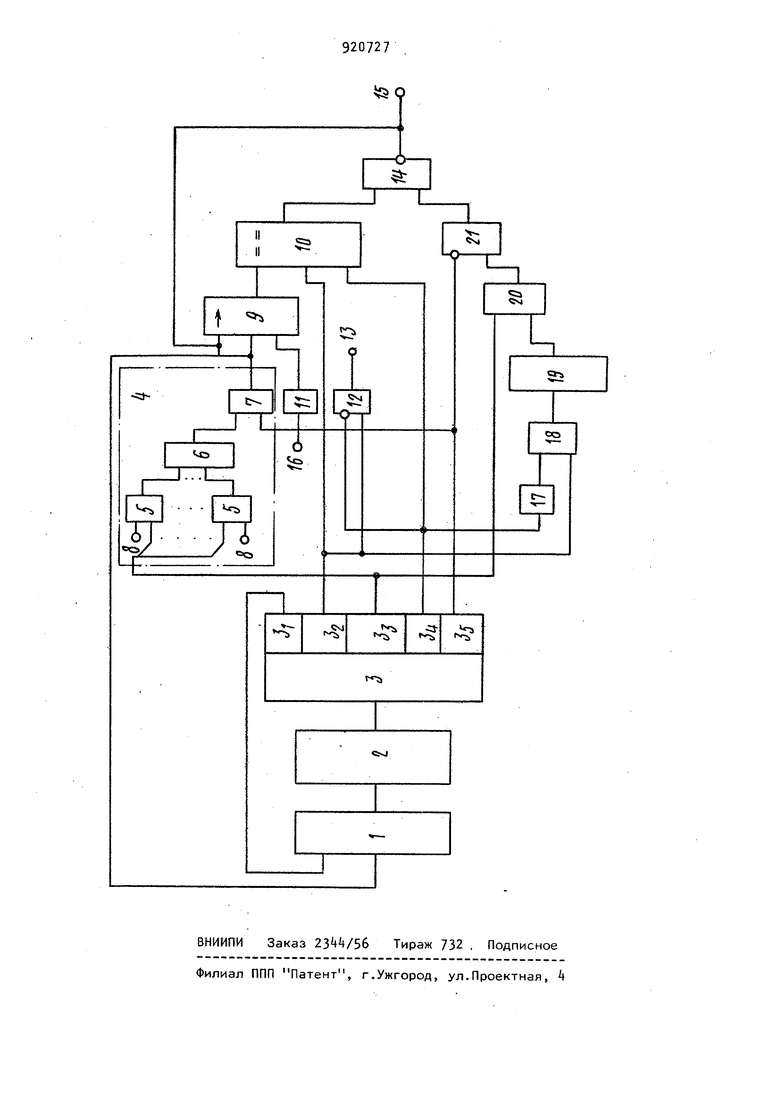

Цель изобретения - повышение оперативности и достоверности контроля Поставленная цель достигается теМ; что микропрограммное устройств управления с контролем, содержащее блок памяти микрокоманд, регистр ад реса, регистр микрокоманд, блок сра нения, сдвигающий регистр, первый элемент И, причем выход регистра адреса соединен с входом блока памя микрокоманд,выход которого соединен со входом регистра микрокоманд, адресный выход которого соединен с первым входом регистра адреса, выход микроопераций регистра микрокоманд соединен с прямым входом пер вого элемента И и с первым Е1Ходом блока сравнения, выход логических условий соединён с первыми входами элементов И группы, выход второго элемента И соединен со вторым входо регистра адреса и первым входом сдзигающего регистра, выход которог соединен со вторым входом блока сравнения, третий вход которого сое динен с инверсным входом первого элемента И и с первым выходом меток регистра микрокоманд, второй выход меток которого соединен с первым входом второго элемента И, выход первого элемента И является выходом микроопераций устройства вторые входы элементов И группы являются входами логических условий устройст ва, выходы элементов И группы соеди нены с входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, содержи т 31лемент задержки, буферный регистр, сумматор по модулю два, элементы И, ИЛИ-НЕ, первый выход меток регистра микрокоманд через элемент задержки соединен с -первым входом третьего элемента И, второй вход которого соединен с выходом микроопераций регистра микрокоманд, выход третьего элемента И соединен со входом буферного регистра, выход которого соединен с первым входом сумматора по модулю два, второй вход которого соединен с выходом логических условий регистра микрокоманд, а выход сумматора по модулю два соединен с прямым входом четверjoro элемента И, инверсный вход которого соединен с вторым выходом меток регистра микрокоман а выход четвертого элемента И соеди иен с первым входом элемента ИЛИ-НЕ второй вход которого соединен с выходом блока сравнения, а выход элемента ИЛИ-НЕ является выходом сигнала ошибки устройства и соединен со вторым входом сдвигающего регистра, третий вход которого соединен с выходом пятого элемента И, первый вход которого является синхровходом устройства, а второй вход соединен с вторым выходом меток регистра микрокоманд. На чертеже изображена функциональная схема микропрограммного устройства управления с контролем. Устройство содержит регистр 1 адреса, блок 2 памяти микрокоманд, регистр 3 микрокоманд с полями: адресным 3„.,, микроопераций 3 п.логических условий 3 3 меток ЗА ЗЕ блок k управления переходами,состоящий из группы элементов И 5, элемента ИЛИ6, второго элемента И 7 и входов 8 логических условий,сдвигающий регистр 9). блок 10 сравнения пятый элемент И -11, первый элемент И 12 с выходом 13 микроопераций, элемент ИЛИ-НЕ. 14, выход 15 сигнала ошибки устройства, синхровход 16 устройства, элемент 17 задержки, третий элемент И 18, буферный регистр 19, сумматор 20 по модулю два, четвертый элемент И 2. Устройство работает следующим образом. По сигналу синхроимпульса, поступающего на вход регистра 1 адреса, из блока 2 по адресу, записанному на регистре 1 адреса, выбирается очередная микрокоманда на регистр 3 микрокоманд. Адресная часть считанной микрокоманды передается из поля адреса 3-j регистра 3 микрокоманд в регистр. 1 адреса. Из поля микроопераций 3ij регистра 3 микрокоманд считываются коды микроопераций и при отсутствии в поле Зд метки контрольной микрокоманды проходят на выход 13 через элемент И 12. В следующем такте из блока 2 по адресу, записанному в регистре 1 адреса, выбирается очередная микрокоманда, и работа устройства происходит аналогичным образом. При ветвлениях в микропрограмме значение логических условий поступает на вход В блока k управления переходами. На другой вход группы элементов И 5 блока k управления переходами поступает код проверяемых логических условий, считанный

из поля За регистра микрокоманд 3. Значения логических условий проходят через элемент ИЛИ 6 на первый вход элемента И .7, на второй вход которого поступает единичное значение метки микрокоманды ветвления. Сигнал выхода элемента И 7 поступает на второй вход сдвигающего регистра 9, а также на второй вход регистра 1 адреса, где модифицирует адрес микрокоманды.

Контрольный признак, записанный в свободных ячейках поля логических условий 3i,одинаков во всех микрокомандах данного участка.Его значение в каждом такте поступает на первый вход сумматора 20 по модулю два и сравнивается с контрольным пригГНаком,хранимымбу.ферным регистром 19,в который он записывается с задержкой через элемент И 18 при считывании контрольной микрокоманды. При совпадении разрядов кода на выходе сумматора 20 по модулю -два сигнал отсутствует. Нулевой сигнал (сигнал совпадения кодов) поступает на второй вход элемента И 21 и далее на второй вход элемента ИЛИ-НЕ 1. Если и на первый вход этого элемента поступает нулевой сигнал, то это говорит об отсутствии ошибок при ветвлениях,на выходе элемента ИЛИ-НЕ 1 появляется единичный сигнал, свидетельствующий о правильном функционировании устройства в целом. Этот же сигнал обнуляет сдвигающий регист 9, подготавливая его к работе.

Проверка правильности ветвлений на участке микропрограммы осуществляется следующим образом.

Сигнал, поступающий с выхода блока 4 управления переходами, формирует в сдвигающем регистре 9 фактическое значение признака К- путем последовательной записи значений npo веряемых логических условий х.. .. При наличии ветвления (метка микрокоманды ветвления равна единице) на сдвигающий регистр 9 поступает через элемент И 11 разрешающий сигнал, по которому в сдвигающем регистре 9 формируется код контрольного признака К путем последовательной записи значений логических условий. Этот код затем сравнивается блоком 10 сравнения с его фактическим значением, поступающим из ячеек поля микроопераций 3 регистра микрокоманд 3.

При равенстве метки контрольной микрокоманды единице происходит сравнение и результат выдается на первый вход элемента ИЛИ-НЕ . В момент, когда происходит контроль ветвления, контроль перехода между рабочими микрокомандами не осуществляется, так как на выходе элемента 17 задержки сигнал отсутствует.

Таким образом, предложенное устройство существенно превосходит известное по достоверности и оперативности контроля. Использование этого устройства позволит разрабатывать высокоэффективные самоконтролируемые микропрограммные устройства.

Формула изобретения

Микропрограммное устройство управления с контролем, содержащее блок памяти микрокоманд, регистр адреса, регистр микрокоманд, первый элемент И, сдвигающий регистр, блок сравнения, причем выход регистра адреса соединен с входом блока памяти микрокоманд, выход которого соединен с входом регистра микрокоманд, адресный выход которого соединен с первым входом регистра адреса, выход микроопераций регистра микрокоманд соединен с прямым входом первого элемента И и с первым входом блока сравненияS выход логических условий соединен с первыми входами элементов И группы, выход второго элемента И соединен со вторым входом регистра адреса и первым входом сдвигающего регистра, выход которого соединен со вторым входом блока сравнения, третий вход которого соединен с инверсным входом первого элемента И и с первым выходом меток регистра микрокоманд, второй выход меток которого соединен с первым входом второго элемента И, выход первого элемента И является выходом микроопераций устройства, вторые входы элементов И группы являются входами логических условий устройства , выходы элементов И группы соединены с входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, отличающееся тем, что, с целью повышения оперативности и достоверности контроля, оно дополнительно содержит элемент задержки, буферный регистр,

сумматор по модулю два, элементы И, ИЛИ-НЕ, первый выход меток регистра микрокоманд через элемент задержки соединен с первым входом третьего элемента И, второй вход которого соединен с выходом микроопераций регистра микрокоманд, выход третьего элемента И соединен со входом буферного регистра, выход которого соединен с первым входом-сумматора по модулю два, второй вход которого соединен с выходом логических условий регистра микрокоманд, а выход сумматора по модулю два соединен с прямым входом четвертого элемента И, инверсный вход которого соединен с вторым выходом меток регистра микрокоманд, а выход четвертого элемента И соединен с первым входом элемента ИЛИ-НЕ,

второй вход которого соединен с выходом блока сравнения, а выход элемента ИЛИ-НЕ является выходом сигнала ошибки устройства и соединен

со вторым входом сдвигающего регистра, третий вход которого соединен с выходом пятого элемента И, первый вход которого является синхровходом устройства, а второй вход соединен

с вторым выходом меток регистра микрокоманд .

Источники информации, принятые во внимание при экспертизе 1. Патент США № 378920, кл, G Об 1 11/10, 197.

2. Авторское свидетельство СССР ff 711573, кл. С 06 F 9/Т, G Об F 11/00, 1977 (прототип).

920727 4йО

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1979 |

|

SU881749A1 |

| Микропрограммное устройство с контролем | 1984 |

|

SU1208556A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100625A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1024920A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления с контролем | 1982 |

|

SU1038944A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

t

ri

oH

rt

гтл

|15T . . T Z

1

«

Авторы

Даты

1982-04-15—Публикация

1980-07-23—Подача