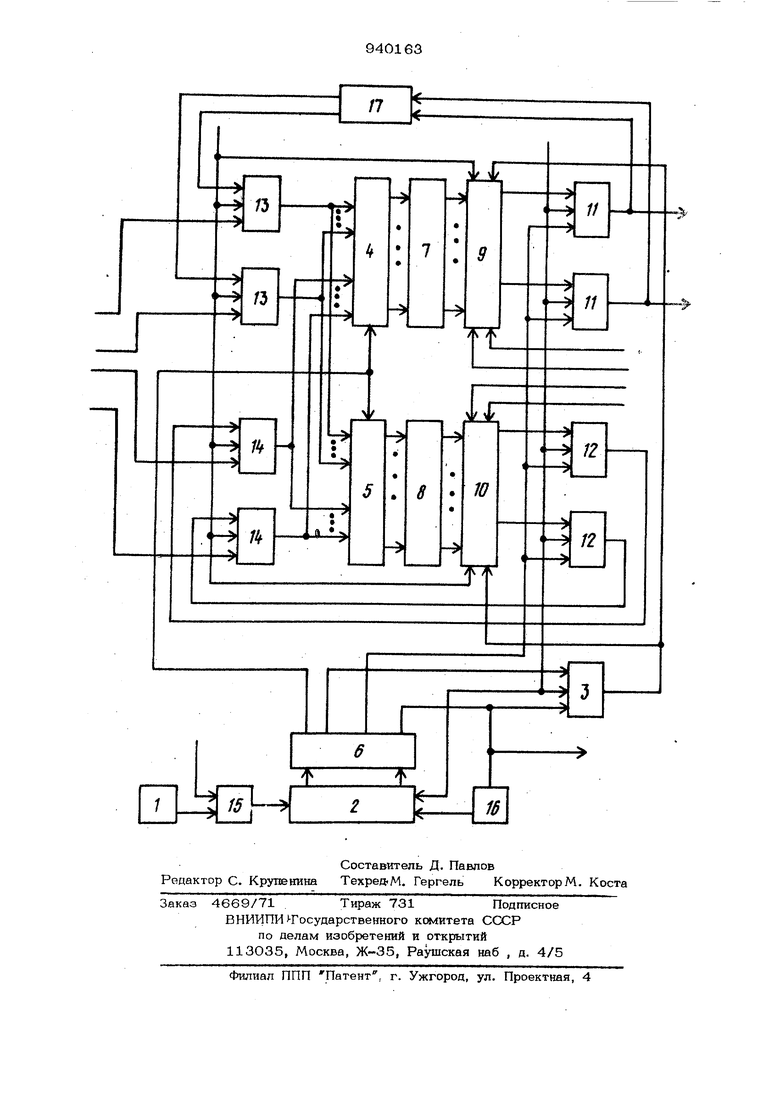

Изобретение относится к вычиспителМ ной технике и может бытьиспользовано для построения управляющих автоматов И автоматов обработки дискретной измер тельной информашга высокой производительности. Известно устройство, содержащее память, коммутаторы, регистр, счетчик, ге нератор, элемент И 1}. Недостатком указанного устройства является недостаточная производите-н ность и низкие функциональные возможно Наиболее близким к предлагаемому является устройство, содержащее две памяти, генератор, счетчик, два дешифра тора, триггер, группу KCTvu.:yTaTOpOB, эле мент И 2., Известное устройство недостаточно активно при усложнении или смене контролируемых объектов. Цель тЕэобретения - повышение коэф фиииента использования оборудования. Поставленная цель достигается тем, что в устройство для контроля логичеоких узлов, содержащее генератор, сче-рчик, выходы которого соединены с входами первого дешифратора, второй д&шифратор, две памяти, первую группу коммутаторов, триггер, элемент И, первый вход устройства соединен с первыми входами триггера и счетника, первая и вторая группа входов устройства со&аинены с первыми группами входов СОО-Рветственно первой и второй памяти, введены два регистра, третий дешифратор, вторая группа коммутаторов, две группы TpiirrepoB, элемент задержки, причем выход генератора и второй вход устрой,ства через элемент И соединеглы с вторым входом счетчика, третья группа входов i стройства соединена -с первыми входйми коммутаторов первой группы, выходы которых соединены с первыми группами входов первого и второго регистров, вторые группы входов которых соединены с выходами коммутаторов второй группы. первые входы которых соединены с четве той гругшой входов устройства, третий вход которого соеш1Нен с вторыми BXI дами коммутаторов первой к -второй групп и с первыми входами первой и второй памяти, вторые группы входов которых соответственно через второй и трети дешифраторы соединены с выходами соответственно первого и второго регистров, входь которых соединены с первым выходом первого дешифратора, второй выход которого соединен с вторым входом трих гера, выход которого соединен с вторыми входами первой и второй памяти, выходы которых соединены с первыми входами триггеров соответственно первой и второй групп, вторые входы которых соединены с третьим выходом первого дешифратора, четвертый выход которого соединен с третьим. входом триггера, выходом устройства и через элемент задержки с третьим входом счетчика, выходы триггеров первой группы соединены с группой выходов устройства, выходы триггеров второй группы соединены с третьими входами соответствующих коммутаторов второй группы, пятая группа входов устройства соединена с третьими входами коммутаторов первой группы первый вход устройства соединен с треть ми входами триггеров первой и орой На чертеже приведена блок-схема уст ройства. Устройство содержит генератор 1, счетчик 2, триггер 3, регистры 4 и 5, дешифраторы 6-8, памяти 9 и 10, триггеры 11 первой группы, триггеры 12 второй группы, коммутаторы 13 первой группы, коммутаторы 14 второй группы, элемент И 15, элемент 16 задержки, объект 17 контроля. Устройство работает следующим образом. Коммутаторы 13 и 14 в зависимости от значения сигнала на входе устройства коммутируют тот или иной вход , а памя ти 9 и 1О в зависимости от значения этого сигнала работают в режиме записи информации или считывания. Перед началом работы устройства в памяти 9 и 10 необходимо запислть информацию об алгоритме работы, т. е. настроить устройство для проверки конкретной аппаратуры. При этом сигнал ло тческого нуля ,с соответствующего входа устройства запрещает прохождение им пульсов от генератора 1 через элемент И 15 на счетчик 2 и приводит триггеры 11 и 12 и счетчик 2 в исходное состояние. Затем на входах устройства устанавливаются сигналы логической единицы. При этом импульсы с генератора 1 через элемент И 15 поступают на вход счетчика 2, откуда в параллельном коде на дешифратор 6 подается число отсчитант1Ь х импульсов, в результате на входы регис-г-ров 4 и 5 поступает импульс, по которому в них записываются адреса, которые дешифрируются дешифраторами 7 и 8 к в памяти 9 и 10 выбираются ячейки, в которые необходимо записать информа цию. Счетчик 2 продолжает считать и дешифратор 6 устанавливает триггер S в единичное значение и разрешается aa пись в памяти 9 и 1О. Затем дешифратор 6 устанавливает триггер 3 в исходное состояние, чем .снимается, сигнал .обрашения с памяти 9 и 10, и сигнализирует о необходимости выставить новую информацию для записи и новый адрес и через элемент 16 происходит сброс счетчика 2 в исходное состояние. Далее процесс мнол гократно повторяется. После записи информации подается сиг нал логической единицы, разрешаюший считывание информации, а коммутаторы 1 3 И 15 коммутируют соответствуюшие входы устройства и триггеров 12. Затем подается импульсный сигнал логического нуля, приводящий счетчик 2 и триггеры 3, 11 И 12 в исходное состояние. Процесс считывания информации из памяти 9 и 10 аналогичен процессу записи и управляется генератором 1, счетчиком 2, дешифратором 6, триггером 3. При этом адреса считывания определяются совокупностью сигналов на триггерах 12 и соответствующих входах устройства. Необходимо учесть, что до подачи первого воздействия на объект 17 значение сигналов на выходах заранее не предсказуемо. Поэтому памяти 9 и 10 запро1 раммированы так что на первом цикле работы в режиме считывания информация, считываемая из них, определяется лишь соотношением сигналов на входах регист ров 4 и 5 и не зависит от выходных сигналов объекта 17. С момента времени, когда значения сигналов на выходах объекта 17 заранее предсказуемы, каждое оч&редное воздействие, выдаваемое на наго, зависит от соотношения сигналов на первой я второй группах входов регистра 5. При этом, если реакция объекта соответ., ствует норме, ,то из памяти 9 считывает ся очередное воздействие на объект а из памяти 10 считывается воздействие для 5S перехода в другое состояние. Если же реакция объекта 17 соответствует не норме (имеется Неисправность ), то ра нее выданное воздействие на него сохраняется до устранения неисправности в нем, а из памяти Ю нет воздействия для перехода в другое состояние. Достигается это благодаря соответствующему программированию 9 и 1О. Анализируя прохождение вьвданного воэдействи5я, мо но определить место неисправности в объекте 17. Изобретение позволяет контролировать радиоаппаратуру по любому алгоритму, определяемому информацией, записанной в блоки ОЗУ, например, из ЭВМ. Устройство имеет не более внутренних СОСТОЯШ1Й и преобразует f входных скг налов -в К выходньтх сигналов причем для смены алгоритма работы не требует ся дополнительных аппаратурных затрат или механических перекоммутаций. Таким образом, технико-экономическа эффективность предлагаемого устройства состоит в повышешга коэффициента исполь зования оборудования на ЗО-60%. Экономическая эффективность ot внедрения изобретения составит 15- 20 тыс. руб. в год на одно изделие. Формула изобретения Устройство для контроля логических узлов, содержащее генератор, счетчик, выходы которого соединены с входами первого дешифратора, второй деши||ратор две памяти, первую группу коммутаторов триггер, элемент И, первый вход устройства соединен о первыми входами триггера и счетчика, первая и вторая группа входов устройства соединены с первыми группами входов соответственно первой и второй памяти, отличающеес я тем, что, с целью повышения коэффициента использования оборудования, в него введены два регистра, третий дешифратор, вторая группа коммутаторов, две группы триггеров, элемент задерж6S6ки, причем выход генератора и второй вход устройства через элемент И соеди-г некы-с вторым входом счетчика, третья rpyinia входов устройства соединена с первыми входами коммутаторов первой группы, выходы которых соединены с первыми группами входов первого и второго регистров, вторые группы входов которых соединены с выходами коммутаторов второй группы, первые входы которых соединены с четвертой группой устройства , третий вход которого соединен с вторыми входами кталмутаторов первой и второй групп и с первыми входами первой и второй пе1мяти, вторые rpyitnj)i входов которых соответственно через второй и третий деши(|раторы соединашл с выходами соответственно первого и второго регистров, входы которых соединены с первым выходом первого дешифратора, второй выход которого соединен с вторым входом триггера, выход которого соединен с вторыми входами первой и второй памяти, выходы которых соединены с первыми входами триггеров соответ ственно первой и второй групп, вторые Входы которых соединены с третьим выходом первого дешифратора, четвертый выход которого соединен с третьим входом триггера , выходом устройства и через элемент задержки с третьим входом счетчика, выходы триггеров первой пы соединены с грутшой выходов устройства, выходы триггеров второй группы со&дииэны с третьими входами соответствую тих коммутаторов второй группы, пятеья группа входов устройства соединена с третьими входами коммутаторов первой группы, первый вход устройства соединен с третьими входами триггеров первой и второй групп. i Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство № 561965, кл. Q06F 11/26, 1973. 2.Авторское свидетельство СССР № 595736, кл. Q06F li/26,l976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Программное устройство управления | 1986 |

|

SU1339558A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Программное устройство управления | 1983 |

|

SU1173414A1 |

| Программное устройство управления | 1985 |

|

SU1264171A2 |

| Устройство для контроля логических схем | 1981 |

|

SU1013956A2 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

Авторы

Даты

1982-06-30—Публикация

1981-04-30—Подача