1

Изобретение (относится к вычислительной технике и может быть исполь-зовано для контроля цифровых блоков, формирующих последовательность управляющих сигналов.

Известно устройство для контроля блока центрального управления, содержащее элемент ИЛИ, счетчик, дешифратор, группу элементов И и триггер С1.

Это устройство обнаруживает неисправности, приводящие к нарушению заданной последовательности управляющих сигналов, но не позволяет определить место неисправности в контролируемом блоке центрального управления.

Наиболее близким к предлагаемому по технической сущности является устройство для контроля блока центрального управления, содержащее элемент ИЛИ, элемент задержки, элемент И, счетчик, дешифратор, группу элементов И, триггер, информационные входы устройства, установочный вход и группу выходов устройства, в ко.тором информационные входы устройства соединены с входами элемента ИЛИ8 а также с первыми входами соответствующих элементов И группы элементов И, выход элемента И соединен с входом элемента И, второй вход которого соединен с суммирую10щим входом счетчика, выходы счетчика соединены с входами дешифратора и с группой устройства, выходы дешифратора соединены с вторыми вхо- дами соответствующих элементов И группы элементов И, выходы группы элементов И соединены с единичным входом триггера, шина установочного входа устройства соединена с

20 нулевым входом триггера и с входом установки счетчика в нулевое состояние.

Устройство работает следующим образом.;

Сигнал, поетупающий по установочному входу устройства устанавливает триггер и счетчик в нулевое состояние, на (т-1) выходах дешифратора устанавливается единичный потенциал, а на выбранном выходе нулевой потенциал, который поступает на вход первого элемента И группы элементов И. Тем самым осуществляется блокировка срабатывания первого элемента И по входу первого управляющего сигнала. Входной сигнал по входу первого управляющего сигнала qepea элемент задержки, элемент И поступает на вход счетчика. По окончанию действия этого сигнала на выходе элемента И срабатывает счетчик, и запрещающий сигнал с дешифратора поступает на вход второго элемента И группы элементов И. При поступлении управляющего сигнала по второму входу второй элемент И группы элементов И не пропускает его. При отсутствии неисправности в контролируемом блоке центрального управления ни один из входных сигналов не проходит через группу элементов И и триггер останется а состоянии О. Поэтому, когда поступит сигнал по последнему входу, дешифратор вырабатывает сигнал Правильно. О

Если в процессе работы нарушает.ся очередность поступления контролируемых сигналов, исчезнет или появится лишний сигнал в месте и во времени не предусмотренных временной диаграммой работы контролируемого цифрового блока, то на выход соответствующего элемента И группы элементов И проходит сигнал, который устанавливает триггер в состояние 1. Сигнал Ошибка с нулевого выхода триггера запрещает прохождение через элемент И сигналов на вход счетчика, вследствие чего состояние счетчика останется неизменным и двоичный код будет указывать номер сигнала по временной диаграммеj после которого произошло нарушение работы контролируемого блока центрального управления. Таким образом, устройство позволяет обнаруживать отказы блока центрального управления, приводящие к нарушению заданной последовательности управляющих сигналов, период следования которых не меньше суммы максимальной длительности входного сигнала,максимального времени задержки сигнала элементом задержки, максимального времени переключения элемента ИЛИ, элемента И, счетчика и дешифратора

2.

Недостаток известного устройстванизкие временные возможности по указанию места отказа в блоке центрального управления, формирующего

высокочастотную последовательность управляющих сигналов.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается

тем, что в устройство для контроля блока управления, содержащее элемент ИЛИ, счетчик, дешифратор, группу элементов И, триггер, причем выходы счетчика соединены соответственно с входами дешифратора и .являются выходами сигнала ошибка устройства , инверсные выходы дешифратора соединены соответственно с первыми входами элементов И группы

элементов И, выходы которых соединены соответственно с входами элемента И, выход которого соединен с единич-; ным входом триггера, нулевой вход которого соединен с нулевым входом

счетчика и является установочным входом устройства, выход сигнала ошибки соедмнен с последним прямым выходом дешифратора, группа информационных входов устройства соединена соответственно с вторыми входами элементов И группы элементов И, с входами элемента ИЛИ, введен элемент ИЛИ-НЕ, входы которого соединены соответственно с информационными входами .устройств,, выход элемента ИЛИ соединен с информационным входом первого каскада счетчика, вход синхронизации первого каскада ; которого соединен с инверсным выходом триггера, прямой выход которого соединен с дополнительным входом элемента ИЛИ-НЕ, выход которого соединен с входом синхронизации второго каскада счетчика.

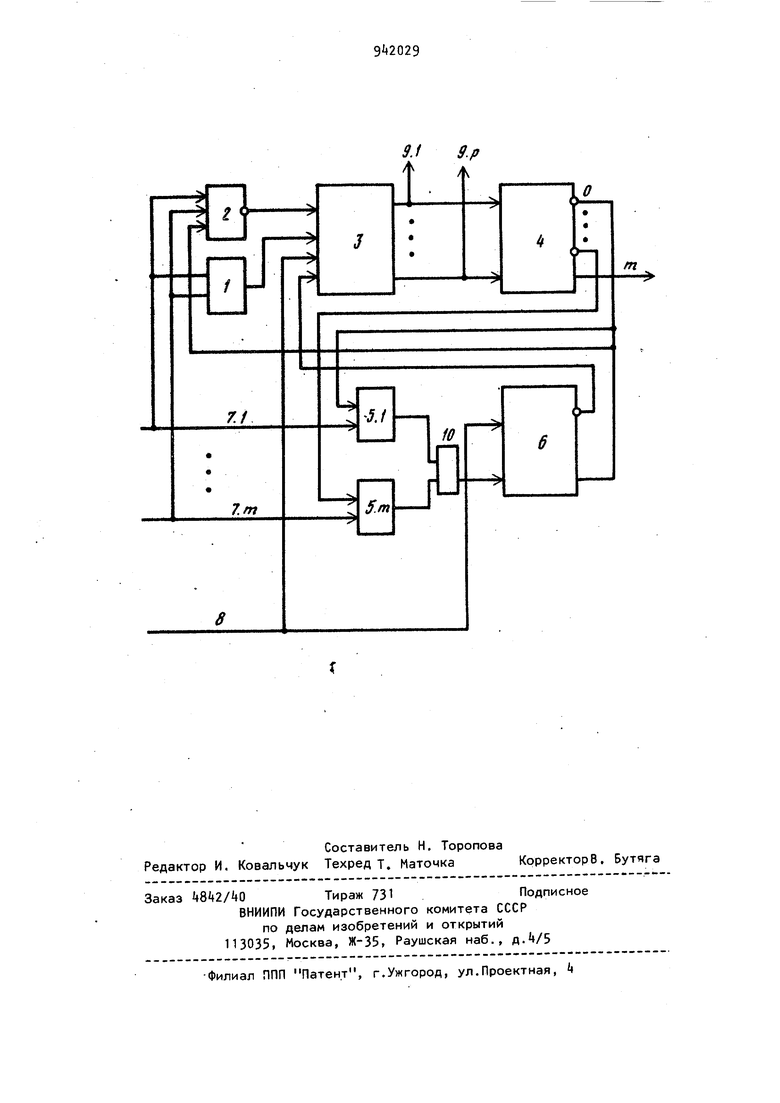

На чертеже приведена структурная схема устройства.

Устройство содержит элемент ИЛИ 1, элемент ИЛИ-НЕ 2, двухтактный счетчик 3, дешифратор k, группу элементов И 5.1 - И,5 т, триггер 6, шины 7.1 - 7.П1 входных управляющих сигналов, шину установочного

входа устройства 8, шины группы выходов 9.1 - 9.Р элемент И 10.

Устройство работает следующим образом.

Сигнал, поступающий по шине установочного входа устройства 8,устанавливает триггер 6 и счетчик 3 в нулевое состояние.

На т-1 выходе дешифратора устанавливается единичный потенциал, а на выбранном - нулевой, который поступает на вход элемента И 5.1. Управляющий сигнал со входа 7.1 не проходит на выход элемента И 5.1. После начала действия управляющего сигнала на выходе элемента ИЛИ 1 содержимое первой ступени счетчика увеличивается на единицу. По окончанию действия управляющего сигнала на выходе элемента ИЛИ-НЕ 2 устанавливается единичный потенциал, который поступает на вход синхронизации второй ступени счетчика 3 и разрешает перепись содержимого первой.ступени счетчика на вторую. С выхода дешифратора k запрещающий сигнал поступает на вход элемента И 5.2 группы элементов И. При поступлении (сигнала по входу 7.2 элемент И 5.2 не пропускает его. При отсутствии неисправностей в контролируемом блоке центрального управления ни один из входных сигналов не проходит через группу элементов И 5-1 И 5 и триггер 6 остается в состоянии О Поэтому, когда поступает сигнал по входу 7т, дешифратор выработает сигнал Правильно. Если в процессе работы нарушается последовательность сигналов, исчезнет или появится лишНИИ сигнал, то на выход соответствующего элемента И группы элементов И 5.1 511 проходит сигнал, который устанавливает триггер 6 в единичное состояние. Сигнал Ошибка с единицного выхода триггера 6 через элемент ИЛИ-НЕ 2 блокирует вторую ступень сч чика по входу синхронизации второй ступени после окончания действия ложного управляющего сигнала, а на вход синхронизации первой ступени счетчика поступает нулевой потенциал с нулевого выхода триггера.

Двоичный код содержимого счетчика сформированный на шинах группы выходов 9.1 Эр счетчика указывает номер сигнала, после которого сформировался сигнал Ошибка. Таким образом, изменение содержимого первой ступени счетчика совмещается по времени с контролем управляющих сигналов 7.1 - 7гп, что приводит к повышению быстродействия устройства. Это позволяет существенно повысить возможности устройства по локализации места отказа в блоке центрального управления.

Формула изобретения

Устройство для контроля блока управления, содержащее элемент ИЛИ, счетчик, дешифратор, группу элементов И, элемент И, триггер, причем выходы счетчика соединены соответственно с входами дешифратора и являются выходами места сбоя устройства, выходы дешифратора соединены соответственно с первыми входами элементов И-группы элементов И, выходы которых соединены соответственно с входами элемента И, выход которого соединен с единичным входом триггера, нулевой вход которого соединен с нулевым входом счетчика и является установочным входом устройства, выход сигнала ошибки устройства соеднен с последним прямым выходом дешифратора, группа информационных входов устройства соединена соответственно с вторыми входами элементов И группы элементов И и с входами элемента ИЛИ ,отли чающеесЯ тем, что, с целью увеличения быстродействия, в устройство введен элемент ИЛИ-НЕ, входы которого соединены соответственно с информационными входами устройства, выход элемента ИЛИ соединен с информационным входом первого каскада счетчика, вход синхронизации первого каскада которого соединен с инверсным выходом триггера, прямой выход которого соединен с дополнительным входом элемента ИЛИ-Н выход которого соединен с входом синхронизации второго каскада счетчика.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 399058, кл. И 03 К 5/18, 197.

2.Авторское свидетельство СССР № , кл. G Об F 11/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Устройство для управления и обмена данными | 1986 |

|

SU1319042A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1985 |

|

SU1337901A1 |

| Устройство для ввода информации | 1984 |

|

SU1145337A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

Авторы

Даты

1982-07-07—Публикация

1980-11-10—Подача