(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ ТАБЛИЧНЫХ ФУНКЦИЙ

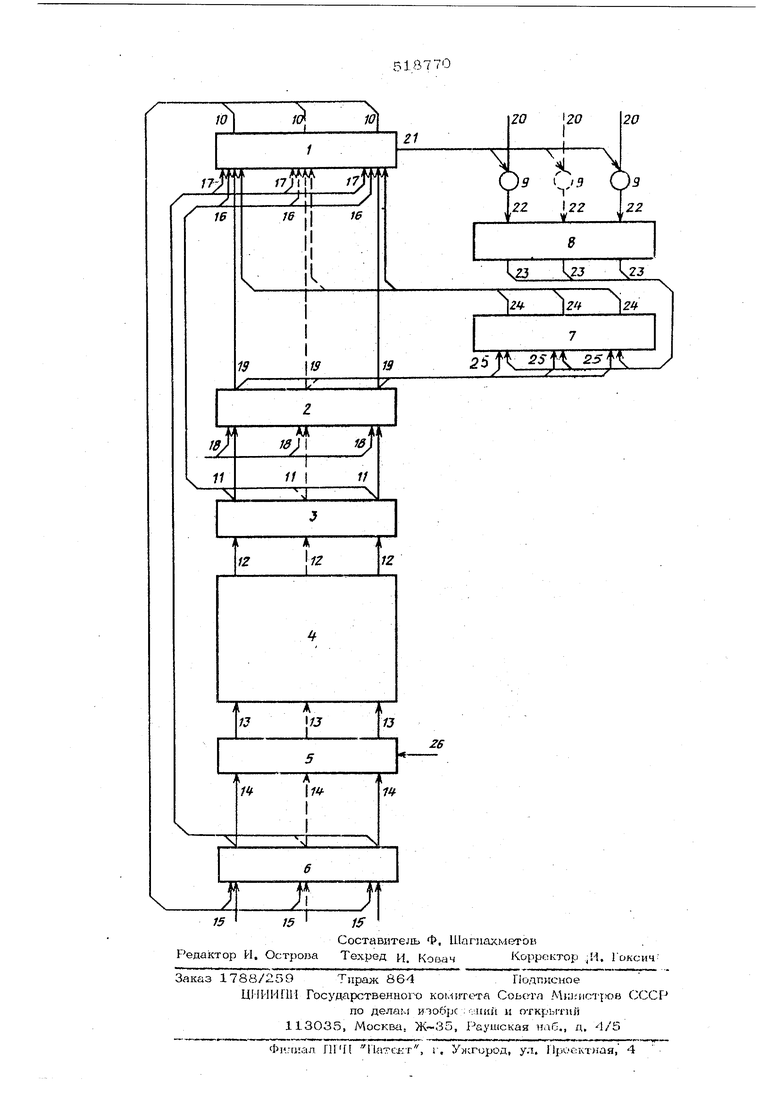

блокировки 8, элек.еиты И 9 второй груп пы, выходы cjTviiv(aTOp-5, вых.однО1Х) регист ра, блока памяти, реглстра-счетчика адреса и регистра адреса команд соответственно 10-14, входы 1)---гнстра адреса комалд 15, входы сумматора 16, 17, входы и выходы шгдекского регистра 18, 19 информацнопнь е входы элементов И второй группы 20, выход знакового разряда сумматора 21, входы и выходы - регист{: а бло-кировки 22, 23, выходы и входы элементов И первой группы 24, 25,счетный вход регистра-счетчика адреса 26,

Регистр адреса команд 6, блок памяти 4 с регистром - счетчиком адреса 5, подклюЧенным ко входам 13 и выходль1 регистром 3, подключенным к выходам 12 индексный регистр 2 и сумматор 1 соединены последовательно. Кроме того, сумматор 1 выxoдa iи 10 подшпочен ко входам регистра адреса команд 6, а входами 17 к выходам регистра адреса команд 6. входами 16 к вьгходам 11 выходного регистра 3, входами 24 к выходам эле- ментов И 7 первой группы, информационные входы 25 которой соединены с вы ходами индексного регистра 2, а управ- ляюшие - с выходами 23 регистра бло кировки 8, Выход 21 з.пакового разряда сумматора 1 через ejioMeHTbi И О вто |рой грунпь подк.аочен ко входам 22 регистра бл.6кировки 8, Входы 18 шщекс- ;юго регистра 2 подключены к итоговому регистру арифметического устройства (на чертеже не показ ан), а выходы 10 - ко входам сумматора 1, входы 15 регисара адреса команды б подюпочены к выхо- дам ri}JorpaivM.i:oro зано.минающего устрой-

елка (на чертеже не показано).

На входы 20 последояателыю во времени начиКгТя с младшего |)азряда поступаютедиличные сит-налы. На вход 26 регистра-счетчика 5 ноступак Т сзлгналы ,+1.,

В блоке 1амяти 4 хранятся табличные (значения Функций, расположенные в ячейках п.;мяти в виде таблиц (массивами) с посто ннр-псфемен ым шагом по адресам, и з} аченин аргумента Хр ,t f,R, соответстБ ощие смене шага расположения табли-огых З}1ачен15й . При этом для каждой из функций дианазон изменения аргумента, например 0,1, узловьгми гчпче)1иями X,; Г разбивается на подцианазоаш

о..а),....,,...,,),: внутри которых, шаг распол1:)жения по адресу и аргументу табличных значений функции носто; Ьыл и равен соответст-

И,

BOiHO -. , li

а перег

ходе из одного поддианазона в д|)угой удваивается, т.е. И р., ,R 7 где Н - минимальный шаг, ра.вный целой степени р основания системы счи- сления (В дандом с;гучае целой степени 2), т.е. h . Величина h и значения аргумента X , Г - 1 R рассчитываются исходя из заданной погрешности приближения функции f (х) , на- . пример по следующей методике,

Из равенства остаточного члена штгер поляционного полинома Ньнзтона нулевого пор$щка заданной погрешности получим

i max If Ч )

I

Затем по значению К., определяетсязна- чение Р I {цдз К J , где ; 1 О означает ближайшее нелое, не меньшее fl. и тем самым минимальный шаг fi h но арг тиенту табличных значе шй функщ1и f (х) для поддианазога О, . Значение Л и другие значения: Хг , T f,T2

определяются в результате репония уравнений

r-l.R

-1

If (МТ

Полученные таким образом значения

Г1 представляют собой в общем

случае полноразрядные значения аргумен-

.та X ,

I Количество узлов для ка вдого поддиатгазона определяется от)1ошеннем

Гр -- 4 Хр /Н,,. J г р.нри 4 X X, - О ,

и Хд 2 /г

...Л(,,-Х,.,,..., ДХ,,ЬЛ

При этом объем в битахтаб гицы (масси1ва) значений кааадой из функпггй равен

/ f .1 сиее

л

- L Г (

L

С1

- количество

где

fli г-0

значений одной из функций при иостоянно-

,переме}шом шаге, равное количеству яче ек памяти, занятых табличными значениями этой функции;

fog и I разрядность ячеек памяти.

Для реали.эв.ции постоянно-переменного шага необходимо храншъ для каждой из вычисляемых, функций, кроме того, значения apryivieHTa Xf , г 1, R ссбот--

ветствующне смене шага расположения табличз ых значений фу(пшии, для чего требуется объем памяти в битах, равный

лVev-C

В игрыш в объеме памяти при постоянно-неремегагоМ шаге расположения таб (личных значений .функций по cp BJOHrao с

постоялным шагом оценивается для к.аж дои из функш1й отношением

t

1Г

-т-тг-гт Л„ t- ДЛр

у ±it 2-Р

2 Пусть, напримео, .реобходимо вычисять функцию Sm X, Х С- о, i) с norpeujX, 0,10001111100,,; Х., Xj 0,11100110000 , Xj 0,11111001100 дх 0,10001111100 йХз -0,ООО1 lOlOllOf ,,00000110100,, % 10001111100 I, 110101 I. 11 U-Io- Ii -Ia-t-Ijtr IjT V-MCI. 14570 бит; /lV 1с 2 2048;Vc Ic Выигрыш в объеме намяти при постоянно-переменном шаге расположения табличных значений функции SLU 5. по сравнению с ностоя,ш1ым шагом равен Ус 20460 Устройство работает следующим образом. Аргумент К из итогового регистра арифметического устройства (на чертеже не показан) по шинам 18 пересылается |На регистр 2 и располагается в его младших разрядах, оставляя, в простейшем случае, нулевыми старшие разряды, количество которых не менее . - где К -множество вычисляемых функций. На регистр адреса команд 6 по шинам 15 пересылается адресная часть команды функция, означающей вычисление функции (элементарной или сложной) от аргумента X , Содержимое регистра 6 является ис- почтительным адресом, по которому расположено в памяти значение аргумента X , соответствуюшее началу поддиапазона L X 1 , X j) , в котором выпол няется первг.че уд1Х)ение шага табличных значений . Остальные значения аргумента Ар, Г 1,R расположе1й.1 в порждке возрастания номера г по адресам, следующим за ад1)есом значения аргумента Х , Располо.ение Х , г 1,R по разрядам ячейки блока памяти 4 аналогично расположению аргумента X в регистре 2. Старшая часть рсизрядов регистра 6, размерность которой рав.а fog.,KL, где К - множество вычисляемых функ ций, содержит адрес таблицы значений вычисляемой функции. Содержимое регистра 6 по шикам 14 пересылается в perHCTf -c4eT4HK 5 и из блока памяти 4 на выходной регис р 3

ностью не болео 6 . В сооа-ветствии с изложенной выше методикой для

заданных исходных данных расс штаны

значения

v-r2 p н fl - 2-«, ,-5 XJ ДХ dX йХб 1, 01011010 ; 1O011O002; 11011110 01101000 ОО110О11 1111 0110001,1457 0 бит 0480 бит. по шшшм 12 выбирается значение аргумента Xj , Затем на сумматоре 1 onpe-i деляется разность х-х eждy содер жимыми регистров 2 и 3, На анше 20, соответствующей младшему 1;азряду регистра блокировки 8, генерируется единичный . сигнал, который проходит через соответствующий элемент И 7 и записывается в младший разряд регистра 8, если знак разности х-х, положительный в случае вычисления функции с монотонно-убывающей производной f (X) . Затем к содержимому регистра-счетчика 5 прлбавля ется единица его младшрго разряда, и соответственно полученюму результату (адресу) из блока памяти 4 выбирается на регистр 3 значение А2 .На сумматоре 1 определяется разность , х - X . На :шине 20, соответствующей разряду регистра 8, след5тощему за младшим, генериру ется ед1шичный сиг-нал, который проходит через соответствующий элемент И 7 и записывается в соответствующий разряд регистра блокировки 8, если знак разности X -Хз положителен и т.л, до :первого результата сравнения Х-Хр О .или до перебора всех значений Xp,, R. |Для функций с мг.яотолно-возрастающей .Производной f ( 1) процесс формирова- :ния содержимого регистра 8 сводится к описанному при определении Sffn (Хр-Х). Затем из региса-ра 2 по шинам 25 аргумент X S а по шинам 23 из регистр 8 сформированная величина поступает но входы группы элементов И 9, где окрепеляется |дезул1 тат логическог-о умножепртя -а X и инверсии содержимого ре;Гистра 8. Ресзу.штат по шкмам 24 иор ;сылвется в cyiviMaTOp 1, Пос::ле .та сумматоре 1 выпол.1 яотся суммир 1вопи л, результатом которпго япдг.ется мспо/глнцельный адрес табли1;шго значения функции, его содержимого с содержимым старн. ших разрядов регастра б, определяющих вид вычисляемой функции, т,е или tg X и т.д. Из cyivJN а-,ч)ра 1 по шинам 10 результат операции пересыпается в регистр 6 и затем из него по шинам 14 - в регистрнсчетчик адреса 5, Окончательным результатом вьшЬлнения команды функция будет число (табличное значение вычисляемой функшш), выбранное из блока памяти 4 на регистр 3 по исполнительному адресу регистра 5,

Формула изобретения

Устройство для формирования адресов

табшт шых функций, содержащее регистр адреса комшщ, выходы которого соединенны с первой группой входов сумматора и через регистр-счетчик адреса - со входа ми блока памяти, выходы которого через выходной регистр соединены со второй группой входов сумматора и с первой

группой входов индексного регистра, выходы которюго соединены с третьей гру&пой входов сумматора, выходы которого соединены с первой группой входов регистра адреса команд, вторая; группа входов которого соединена с первой группой входов устройства, управляющий вход ко торого соединен со счетным входом регистра-счетчика адреса, а вторая группа входов индексного регистра соединена со второй группой входов устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит регистр блокировки, первую в вторую группы элементов И, щэичем выходы индеко|Ного регистра и регистра блокировки соединены со входами элементов И первой группы, выходы которых соединены с четвертой группой входов сумматора, выход знакового разряда которого соединен с одними входами элементов И второй грувиг . пы, другие входы которых соединены с третьей группой входов устройства, а вь| :ходы - со входами регистра блокировки

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления стандартных функций | 1980 |

|

SU942032A1 |

| Устройство для воспроизведения функций табличным методом | 1983 |

|

SU1153320A1 |

| Устройство для формирования адресов табличных функций | 1980 |

|

SU932496A1 |

| Цифровой функциональный преобразователь | 1982 |

|

SU1024894A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Функциональный преобразователь | 1974 |

|

SU517023A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

Авторы

Даты

1976-06-25—Публикация

1974-06-10—Подача