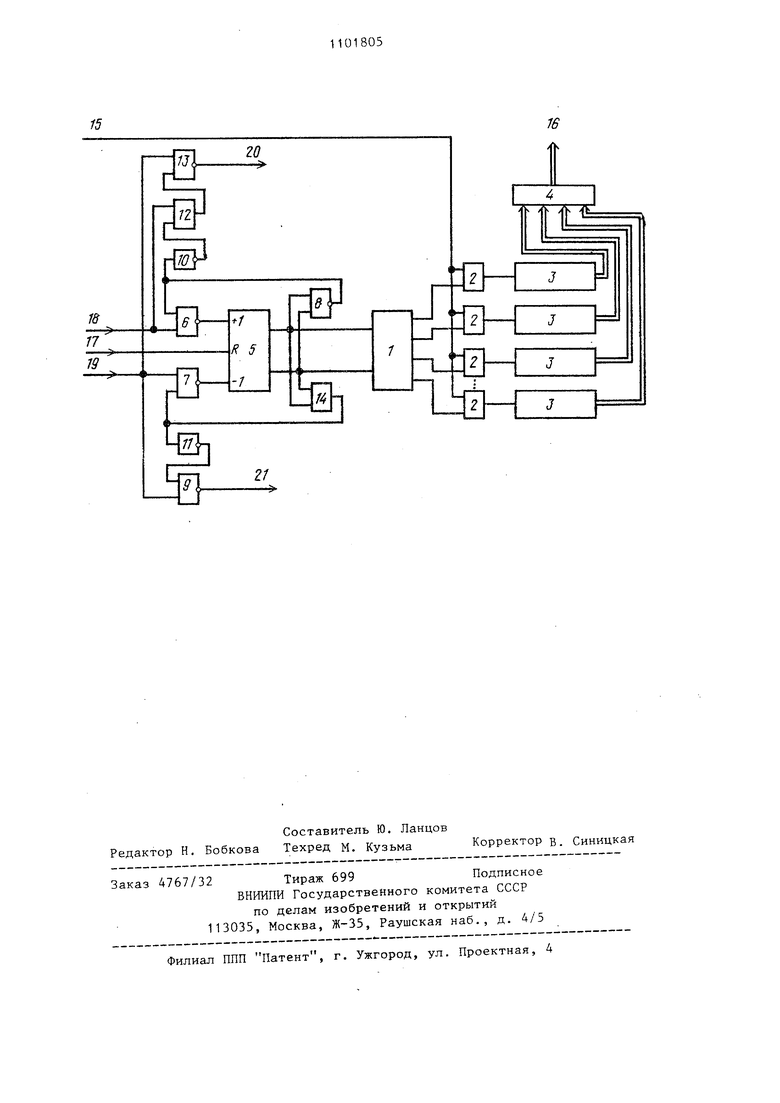

1 Изобретение относится к цифровой вычислительной технике и может быть использовано для построения унифицированных блоков синхронизации запоминающих устройств. Известно устройство для управле ния оперативной памятью, содержащее формирователи синхронизирующих сигналов и сигналов регенерации, триггера конца цикла и режима и дв элемента И-НЕ, причем выход формиро вателя синхронизирующих сигналов соединен с входом триггера конца цикла, выход которого соединен с первым входом первого элемента И-НЕ второй вход - с первьм входом триггера режима, с другим входом тригге ра конца цикла и с входом устройства, выход первого элемента И-НЕ сое динен с вторым входом триггера, режима, третий вход которого соединен с выходом формирователя сигналов ре генерации, выходы триггера режима соединены с входом второго элемента И-НЕ, выход которого соединен с входом формирователя синхронизирующих сигналов 1 JВ данном устройстве временная диаграмма ОЗУ вырабатывается с помощью формирователя синхронизирующи сигналов. Если устройство управлени должно работать с накопителями разных; типов, то временная диаграмма рассчитывается из условия нормального функционирования накопителя, имеющего самое низкое быстродействи Поскольку без технологичесьсого вмеш тельства в устройство изменить пара метры управляющих сигналов невозможно, то в остальных случаях это приводит к неоправданным потерям в быстродействии. Известно также устройство для уп равления полупроводниковой памятью содержащее блок ввода-вывода информации и блок регенерации информации, подключенные к блоку управления, элементы И и ИЛИ, генераторы импульсов и блок местного управления, первый и второй входы которого подключены к соответствующим вkoдaм блока ввода-вывода информации, третий и четвертый входы - к выходам блока регенерации информации, выходы блока местного управления соединены с одними входами элементов И, другие входы которых подключены к выходам генераторов 14мпул сов, а выходы через первый элемент 052 ИЛИ к входу блока управления, входы генераторов г-тмпульсов соединены с Бькодом второго элемента ИЛИ, входы которого подключены к одному из входом блока ввода-вывода информации и четвертому входу блока местного управления, В этом устройстве временные диаграммь:, соответствующие разным типам накопителей, формируются с помощью генераторов, частоты которых отличаются друг от друга. В зависи мости от разрядом адреса, определяющих номер накопителя с 1-;оторым производится обмен данными, блок местного управления разрешает прохождение импульсов с, соответствующего генератора через элементы И и Ш1К на вход блока упргвле1 ия. где формируются: управляющие сигналы ОЗУ. Поскольку скорость выдачи управляющих сигналов определяется частотой тактовых импульсов, поступающих на вход блока управления, то каждому типу накопителей соответствует своя временная диаграмма 2. Недостатки этого устройства заключаются в том5 что накопители даже одного типа могут существенно отличаться по быстродействию из-за техноJIoгичecкиx особенностей их производства. Кроме того, их временные диаграммы,, как правило, меняются при изменении температуры, напряжения питания и т.д. Необходимо также f.ecTb разброс параметров элементов самой схемы управления. Поэтому для надежной работы устройства частота генератора, определяющего временную диаграмму соответствзтощего накопителя, должна выбираться с достаточным запасом при учете всех этих факторов. В результате скорость обмена информацией с памятью будет как правило на 15 - 20% ниже максимально возможной при данных условиях. Другим недостатком этого устройства является необходимость быстродействия накопителя при формировании кода адреса, что затрудняет эксплуатацию устройства. Наиболее близким к изобретению по технической сущности является устройство, содержащее дешифратор, группу из п элементов И, группу из п элементов задержки и блок элементов ИЛИ, группа выходов которого является группой выходов синхронизации 31 устройства, i-я (i 1,2,...,n) гру па входов блока элементов ИЛИ соеди нена с группой выходов 1-го элемент задержки, вход которого соединен с выходом i-го элемента И группы, первый вход которого соединен с i-bi вьтходом дешифратора, вторые входы элементов И группы соединены с тактовым входом устройства С 31. Недостатком известного устройства является низкая область применения, обусловленная отсутствием возможности адаптации к быстродействию разных типов накопителей, или, если применяется один тип накопителя, требуется менять условия его синхрониз ации. Цель изобретения - расширение об ласти применения путём обеспечения возможности адаптивного изменения п раметров синхросигналов. Поставленная цель достигается те что устройство синхронизации памяти содержащее дешифратор, группу из ti элементов И, группу из п элементов задержки и блок элементов ИЛИ, груп па вьгходов которого является группой выходов сигналов синхронизации устройства, i-я ( 1 1, 2,...,п) группа входов блока элементов ИЛИ соединена с группой выходов i-ro элемента задержки, вход которого соединен с выходом i-ro элемента И группы, первый вход которого соединен с i-M выходом дешифратора, вторые входы элементов И группы соединены с тактовым входом устройства, дополнительно содержит реверсивный счетчик, элемент ИЛИ, элемент ИЛИ-Н четыре элемента И-НЕ, два элемента НЕ и элемент И, причем группа входо дешифратора соединена с группой информационных выходов реверсивного счетчика, с группой входов элемента ИЛИ и с группой входов первого элемента И-НЕ, выход которого соединен с первым входом второго эл мента И-НЕ и через первый элемент Н с первым входом элемента И, второй вход которого соединен с входом исправности памяти устройства и вторы входом второго элемента И-НЕ, выход которого соединен со счетным суммир ющим входом реверсивного счетчика, счетный вычитающий которого соединен с выходом третьего элемента И-НЕ, первый вход которого соединен с входом неисправности па5мяти устройства, с первым входом четвертого элемента И-НЕ и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом элемента И, выход элемента ИПИ-НЕ является выходом индикации конца настройки устройства, второй вход третьего элемента И-НЕ соединен с выходом элемента ИЛИ и через второй НЕ соединен с вторым входом четвертого элемента И-НЕ, выход которого является выходом индикации неисправности памяти устройства, вход установки в ноль реверсивного счетчика является установочным входом устройства . На чертеже представлена схема предлагаемого устройства синхронизации памяти. Устройство содержит дешифратор 1, группу из п элементов li 2, группу из п элементов 3 задержки, блок элементов ИЛИ 4, -реверсивный счетчик 5, четыре элемента И-НЕ 6-9, два элемента НЕ 10 и 11, элемент И 12, элемент ItnH-HE 13 и элемент ИЛИ 14, тактовый вход 15, группу выходов 16 синхронизации, установочный вход 17, вход 18 исправности памяти, вход 19 неисправности памяти, выход 20 индикации конца настройки, выход 21 индикации неисправности памяти. Устройство может работать в режимах настройки и рабочем. В начале режима настройки на установочньш вход 17 устройства подается сигнал, обнуляющий реверсивный счетчик 5, при этом на выходе элемента И-НЕ 8 появляется высокий потенциал, на выходе элемента ИЛИ 14 низкий, а на выходе дешифратора 1 устанр хгивается код, стробирующий элемент И 2, Затем с помощью ЭВМ или средств встроенного контроля начинается тестирование накопителя, при этом на вход 15 устройства периодически поступают импульсы запуска, которые через элемент И 2 проходят на вход элемента 3 задержки. Величины задержек последнего расчитываются на наиболее неблагоприятные условия работы ОЗУ, поэтому на выходах 16 элементов ИЛИ 4 формируется последовательность синхронизир тощих сигналов, обеспечивающая функционирование накопителя с достаточным запасом по временным параметрам. По окончании тестирования в устройство

выдается положительггый импульс, причем в случае правильного прохохсдеПИЯ теста он поступает ка вход 18., а в случае обнаружения ошибки - ка вход 19. Если положительный импульс поступает на вход 19, то через элемент И--НЕ 9 он выдается на выход 21 как признак неисправности накопителя и через элемент 3 - на выход 205 ка(С признак конца настройки.

Выдача этих двух сигналов свидетельствует о наличии в накопителе неисправности не зависящей от его временной диаграммы. Если положительньщ импульс поступает на вход 18, то он прокодит элемент И-НЕ 6 и увеличивает на единиду содержимое реверсивного счетчика, в результате чего на выходе элемента ИЛИ 14 появляется высокий потенциал, а на выходах дешифратора 1 устанавливается код, стробирующий элемент И 2, Затем вновь начинается тестртрование накопителя. причем импульсы залтуска проходят в этом случае через следующий элемент И 2 ка вход слецующего элемента 3 задержки. Поскольку величины задержек последнего выбираются несколько меньшими, чем у предыд тцего элемента 3, то на выходах 16 вырабв-тывается более сжатая последовательность синхронизир лощих сигналов, Если после завершения второго тестирования положительный импульс поступает на вход 19. то он проходит элемент и возвращает счетчик в исходное состояние. Одновременно с выхода 20 устройства выдается признак конца настройки. В случае поступления положительного импульса на вход 18 содержимое реверсивного счетчика вновь уЕеличи}зается на единицу.

Так1-5м образом, в режиме настройки временная диаграмма накопителя постепенно скимзе- ся и, следовательно увеличивается го быстродействие, Продесс закапчивается установкой оптимальной для данныхусловий време-п-юй диаграмм;. Если величины

2 выбраны достаточно больБ ими и обеспечивагот правильное функционирование ;-;акопителя. то имеет мёсто успешное оконча} ие тестирования при формировании временной диаграммы с помощью последнего элемента 3 задержк

В этом случае во избежании переполнения реверсивного счетчика 5. его суммир; г101дий вход блокируется никим потенциалом с выхода элемента И-НЕ 8, а положительный импульс, пршедший на вход 18. через элементы И 12 и ШШ-НЕ 13 проходит на выход 20 как признак конца настройки.

Появление признака конца настройки на вьпсоде 20 свидетельствует о v oTOBHocTH ОЗУ к работе,, и с этог момента устройство переходит в рабочий режим. При изменении условий процесса выч:исле1шй может возникнуть необходимость в переходе на временную диaгpaIvlмy. Тогда вновь необходимо провести тестировггние наког1И:теля. Во избежании потери данньп-: это 1чожно сделать посредством считывания всех ячеек на копителя и одновр)еменной их проверки с помогдьн} дополнительных контрольных разрядов в кодовом слове. При использовании накопителя на ди1 амических запоминающих микросхемах спедиальньк затрат времени на контрольное считывание как правило не требуется, так как в этом случае оно может быть совмещено с режимом регенерации,, Гюсле завершения контрольного счк:тывания всех ячеек как и в реж:;1ме настройки, на входы 18 или 19 устройства подается положите ьный импульс, меняющий состояние реверсивного счетчика 5. Об установке временной диаграммы, соответствутощей HOBLW условиям работы свьщетельствуют выдача признака конца наст1зойки с выхода 20.

1аким образом, изобретение позволяет синхронизировать работу памяти с плавной адаптацией к ее временныь1 характеристикам, что не имело места в известном устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации памяти | 1983 |

|

SU1169017A1 |

| Устройство для синхронизации памяти | 1986 |

|

SU1361528A1 |

| Устройство для синхронизации памяти | 1984 |

|

SU1247853A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

| Устройство для синхронизации памяти | 1989 |

|

SU1682993A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для обучения операторов | 1986 |

|

SU1357994A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Устройство для контроля логических схем | 1978 |

|

SU744580A1 |

УСТРОЙСТВО СИНХРОНИЗАЦИИ ПАМЯТИ, содержащее дешифратор, группу из Р элементов И, группу из п элементов задержки и блок элементов ИЛИ, группа выходов которого является группой выходов сигналов синхронизации устройства, 1-я ( 1 1,2,...п) группа входов блока элементов ИЛИ соединена с группой выходов i-ro элемента задержки, вход которого соединен с выходом i-ro элемента И группы, первый вход которого соединен с i-м выходом дешифратора, вторые входы элементов И группы соединены с тактовьм входом устройства, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности адаптивного изменения параметров синхросигналов, оно дополнительно содержит реверсивный счетчик, элемент ИЛИ, элемент ИЛИ-НЕ, четыре элемента И-НЕ, два элемента НЕ и элемент И, причем группа входов дешифратора соединена с группой информационных выходов реверсивного счетчика, с группой входов элемента ИЛИ и с группой входов первого элемента И-НЕ, выход которого соеди,нен с первым входом второго элемента И-НЕ и через первый элемент НЕ с первым входом элемента И, второй вход которого соединен с входом исправности памяти устройства и вторым входом второго элемента И-НЕ, выход которого соединен со счетным суммирующим входом реверсивного i счетчика, счетный вычитающий вход которого соединен с выходом третьего элемента И-НЕ, первый вход которого соединен с входом неисправности памяти устройства, с первым входом четвертого элемента И-НЕ и с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом элемента И, выход элемента ИЛИ-НЕ является выходом индикации конца настройки устройства, второй 00 ,вход третьего элемента И-НЕ соединен о с выходом элемента ИЛИ и через втоСП рой элемент НЕ соединен с вторым входом четвертого элемента И-НЕ, выход которого является выходом индикации неисправности памяти устройства, вход установки в ноль реверсивного счетчика является установочным входом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления оперативной памятью | 1978 |

|

SU752338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Логические основы ЦВТ | |||

| М., Советское радио, 1972, с | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ ЧЕРТЕЖЕЙ ДЛЯ ОДНООБРАЗНОЙ РАСКРОЙКИ ПРЕДМЕТОВ ОДЕЖДЫ | 1919 |

|

SU287A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1984-07-07—Публикация

1982-09-22—Подача