(54) ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Ячейка памяти | 1973 |

|

SU444245A1 |

| Ячейка памяти | 1973 |

|

SU545007A1 |

| Ясейка памяти | 1974 |

|

SU521605A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство | 1983 |

|

SU1238156A1 |

Изобретение относится к вычислительной технике и предназначено прежде всего для использования в оперативныхзапоминающих устройствах цифровых вычислительных машин, в частности, имеющих интегральное иснолНение.

Известна ячейка памяти, содержащая два двухэмиттерных транзисторов п-р-п типа,коллектор первого из которых соединен с базой второго, коллектор второго соединен с базой пер:вого, nopiBbie эмиттеры двухэмиттерных транзисторов подключены к соответствующим разрядным шинам, а вторые объединены, коллекторы первого двухэмиттерного первого нагрузочного и второго переключающего п-р-п транзисторов подключены к базе первого переключающего п-р-п транзистора, коллекторы второго двухэмиттерного, второго нагрузочного и первого переключающего транзисторов подключены к базе второго переключающего транзистора, эмиттеры переключающих транзисторов и вторые эмиттеры двухэмиттерных транзисторов подключены к числовой шине; эмиттеры нагрузочных транзисторов подключены к щине питания, а базы нагрузочных транзисторов подключены к щине смещения

Недостатком данной ячейки является относительно небольшой ток, протекающий в разрядных шинах при считывании ияформации, что обусловлено низким коэффициентом усиления р-п-р транзисторов с горизонтальной структурой.

Известна также ячейка памяти, содержаща я два многоэмиттерных п-р-п транзистора, эмиттер первого из которых соединен с базой второго, а эмиттер второго - с базой первого и два токозадающих р-п-р траНзистор.а, «аждый многоэмиттерный транзистор п-р-п типа содержит по дополнительному эмиттеру, которые через резистор подключены к шине источника питания, а коллекторы многоэмиттерных транзисторов п-р-п типа подключены к базам транзисторов р-п-р типа, соединенных между собой 2. Этой ячейке свойственна низкое быстродействие в режиме считывания.

Наиболее близки м к изобретению техническим решением является ячейка памяти, содержащая два п-р-п транзистора, первые эмиттеры которых подключены IK базе соответствующего п-р-п транзистора, два р-п-р транзистора, первые эмиттеры которых объединены, вторые эмиттеры подключены к соответствующим разрядным шинам, базы р-п-р транзисторов подключены к коллекторам соответствующих п-р-п транзисторов, адресные шины и щиНу питания 3.Однако этому прототипу свойственно относительно низкое быстродействие при считывании информации с ячейками памяти.

Цель изобретения - повышение быстродействия ячейки.

Достигается это тем, что ячейка памяти содержит дополрштельный п-р-п транзистор, база которого подключена к адресной шине, эмиттер - к шине питания, коллектор - к базам р-п-р транзисторов, вторые эмиттеры п-р-п транзисторов подключены к соответствующим (разрядным шинам.

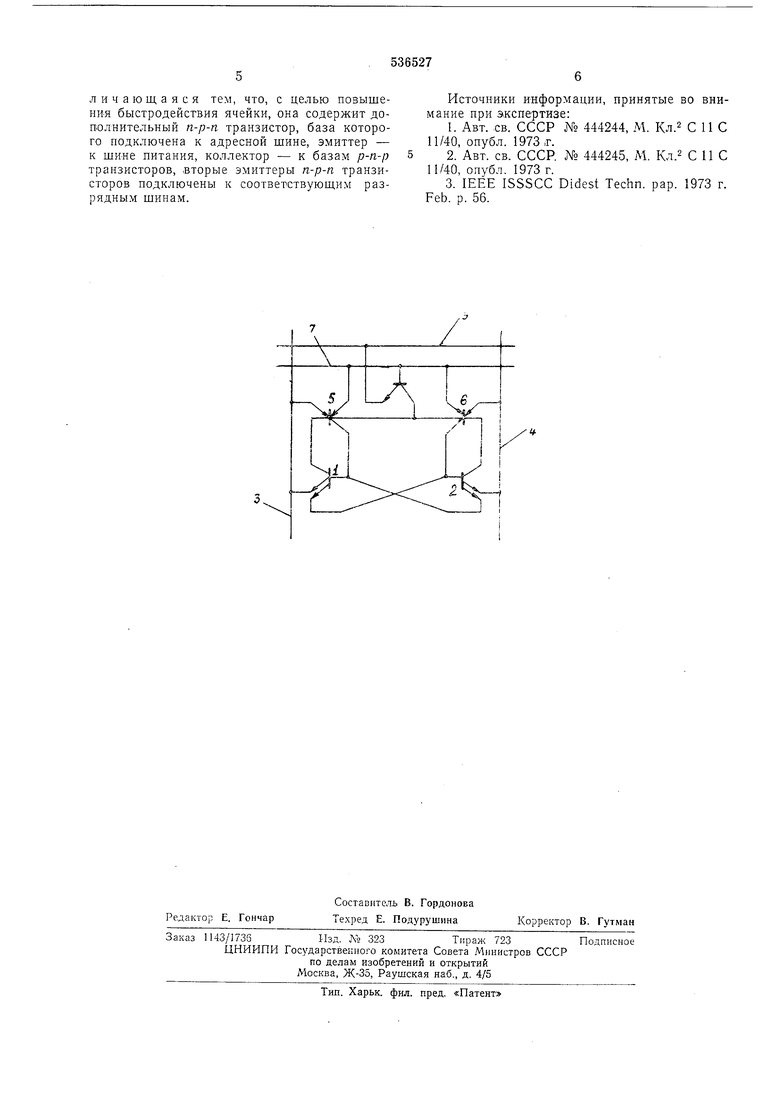

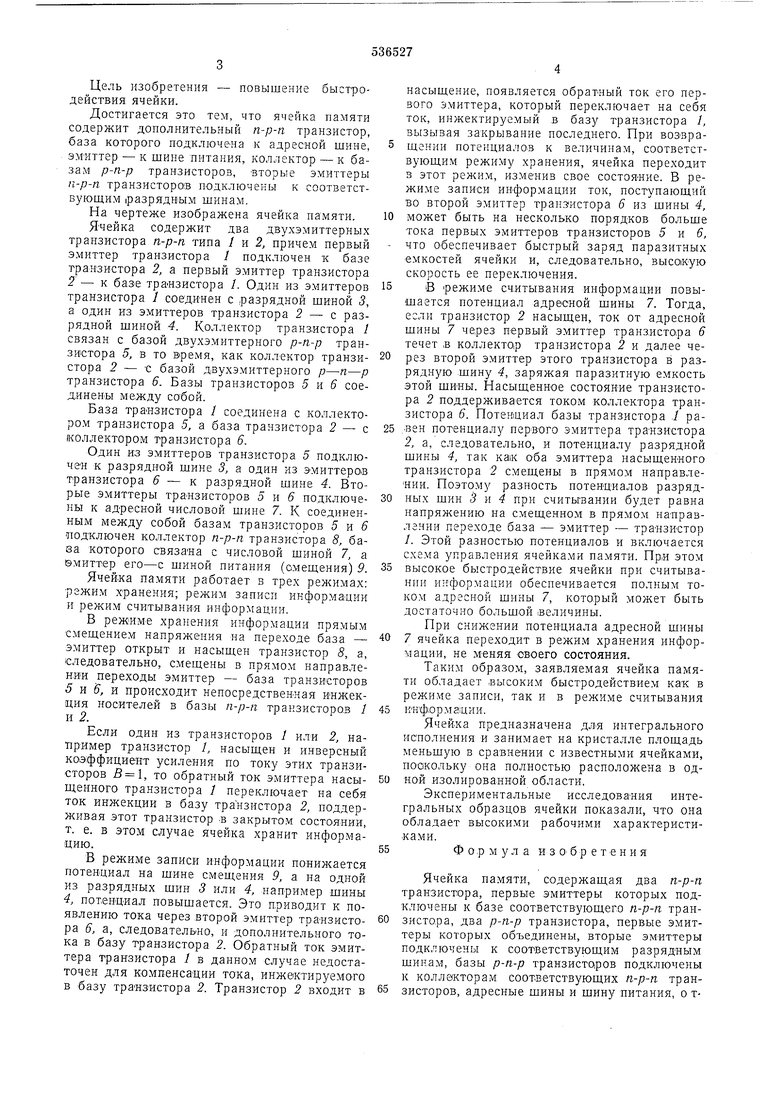

На чертеже изображена ячейка памяти.

Ячейка содержит два двухэмиттерных транзистора п-р-п типа / и 2, причем первый эмиттер транзистора / подключен к базе транзистора 2, а первый эмиттер транзистора 2- к базе транзистора /. Один из эмиттеров транзистора / соединен с разрядной шиной 5, а один из эмиттеров транзистора 2 - с разрядной шиной 4. Коллектор транзистора / связан с базой двухэмиттерного р-п-р транзистора 5, в то время, как коллектор транзистора 2 - С базой двухэмиттерного р-п-р транзистора 6. Базы транзисторов 5 и 5 соединены между собой.

База транзистора / соединена с коллектором транзистора 5, а база транзистора 2 - с коллектором транзистора 6.

Один из эмиттеров транзистора 5 подключен к разрядной шине 3, а один из эмиттеров транзистора 6 - к разрядной шине 4. Вторые эмиттеры транзисторов 5 н 6 подключены к адресной числовой шине 7. К соединенным между собой базам транзисторов 5 и 5 подключен коллектор п-р-п транзистора 8, баеа которого связана с числовой шиной 7, а вмиттер его-с шиной питания (омеш,ения) 9.

Ячейка памяти работает в трех режимах: режим хранения; режим записи информации и режим считывания информации.

В режиме хранения информации прямым смещением напряжения на переходе база - эмиттер открыт и насыщен транзистор 8, а, следовательно, смещены в прямом направлении переходы эмиттер - база транзисторов 5 и 6, и происходит непосредственная инжекция носителей в базы п-р-п транзисторов / и 2.

Если один из транзисторов 1 или 2, например транзистор /, насыщен и инверсный коэффициент усиления по току этих транзисторов В 1, то обратный ток эмиттера насыщенного транзистора / переключает на себя ток ннжекции в базу транзистора 2, поддерживая этот транзистор в закрытом состоянии, т. е. в этом случае ячейка хранит информацию.

В режИхМе записи информации понижается потенциал на шине смещения 9, а на одной из разрядных шин 3 или 4, например шины 4, потенциал повышается. Это приводит к появлению тока через второй эмиттер транзистора 6, а, следовательно, и дополнительного тока в базу транзистора 2. Обратный ток эмиттера транзистора / в данном случае недостаточен для компенсации тока, инжектируемого в базу транзистора 2. Транзистор 2 входит в

насыщение, появляется обратный ток его первого эмиттера, который переключает на себя ток, инжектируемый в базу транзистора /, вызывая закрывание последнего. При возвращении потенциалов к величинам, соответствующим режиму хранения, ячейка переходит в этот режим, изменив свое состояние. В режиме записи информации ток, поступающий во второй эмиттер тра1 зистора 6 из шины 4, может быть на несколько порядков больше тока первых эмиттеров транзисторов 5 и 5, что обеспечивает быстрый заряд паразитных емкостей ячейки и, следовательно, высокую скорость ее переключения.

В режиме считывания информации повышается потенциал адресной шины 7. Тогда, если транзистор 2 насыщен, ток от адресной шины 7 через первый эмиттер транзистора 6 течет в коллектор транзистора 2 и далее через второй эмиттер этого транзистора в разрядную шину 4, заряжая паразитную емкость этой шины. Насыщенное состояние транзистора 2 поддерживается током коллектора транзистора 6. Потенциал базы транзистора ./ ра/вен потенциалу первого эмиттера транзистора 2, а, следовательно, и потенциалу разрядной шины 4, так KaiK оба эмиттера насыщенного транзистора 2 смещены в прямом направлении. Поэтому разность потенциалов разрядных щин 3 и 4 при считывании будет равна напряжению на смещенном в прямом нанравлении переходе база - эмиттер - транзистор L Этой разностью потенциалов и включается схема управления ячейками памяти. При этом высокое быстродействие ячейки при считывании информации обеспечивается полным током адресной шины 7, который может быть достаточно большой величины.

При снижении потенциала адресной щины 7 ячейка переходит в режи.м хранения информации, не меняя овоего состояния.

Таким образом, заявляемая ячейка памяти обладает высоким быстродействием как в режиме записи, так и в режиме считывания Информащии.

Ячейка предназначена ДЛЯ интегрального исполнения и занимает на кристалле площадь меньшую в сравнении с известными ячейками, поскольку она полностью расположена в одной изолированной области.

Экспериментальные исследования интегральных образцов ячейки показали, что она обладает высокими рабочими характеристиками.

Формула изобретения

Ячейка памяти, содержащая два п-р-п транзистора, первые эмиттеры которых подключены к базе соответствующего п-р-п транзистора, два р-п-р транзистора, первые эмиттеры которых объединены, вторые эмиттеры подключены к соответствующим разрядным щинам, базы р-п-р транзисторов подключены к коллекторам соответствующих п-р-п транзисторов, адресные шины и шину питания, о тл и чающаяся тем, что, с целью повышения быстродействия ячейки, она содержит дополнительный п-р-п транзистор, база которого подключена к адресной шине, эмиттер - к шине питания, коллектор - к базам р-п-р транзисторов, вторые эмиттеры п-р-п транзисторов подключены к соответствуюшим разрядным шинам.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1976-11-25—Публикация

1974-12-20—Подача