Изобретение относится к радиотехнике и может быть использовано в системах цифровой обработки сигналов.

Цель изобретения - повЕ)1шение быстродействия.

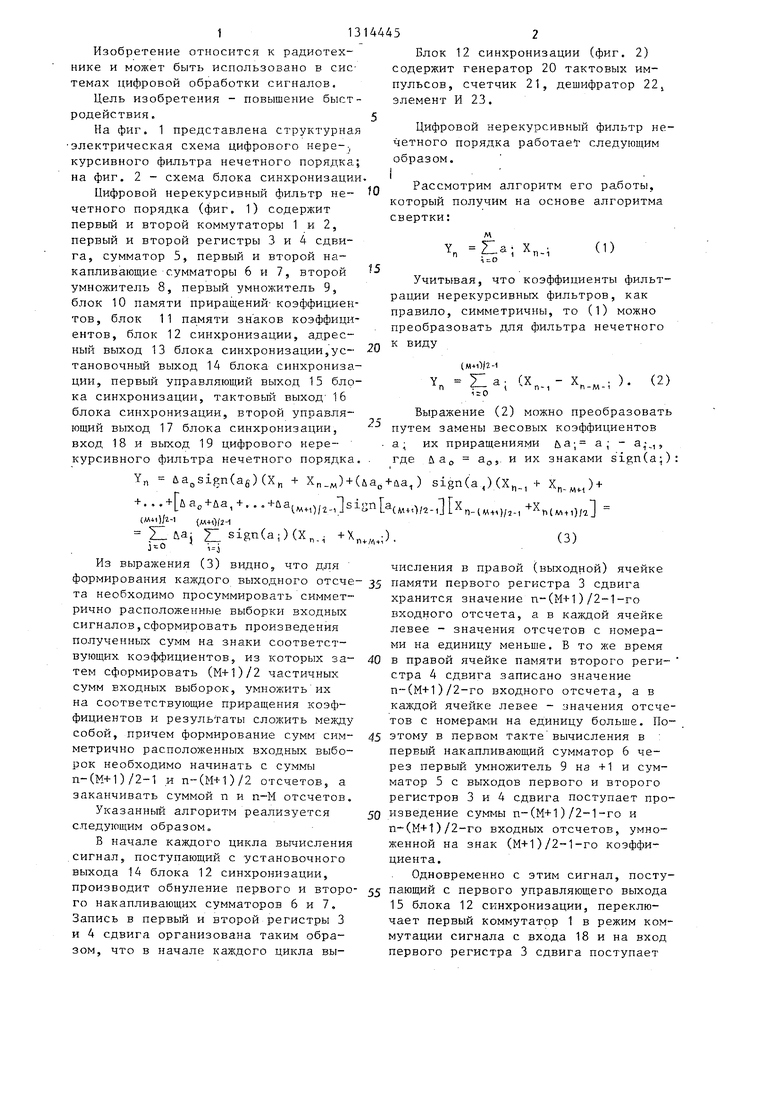

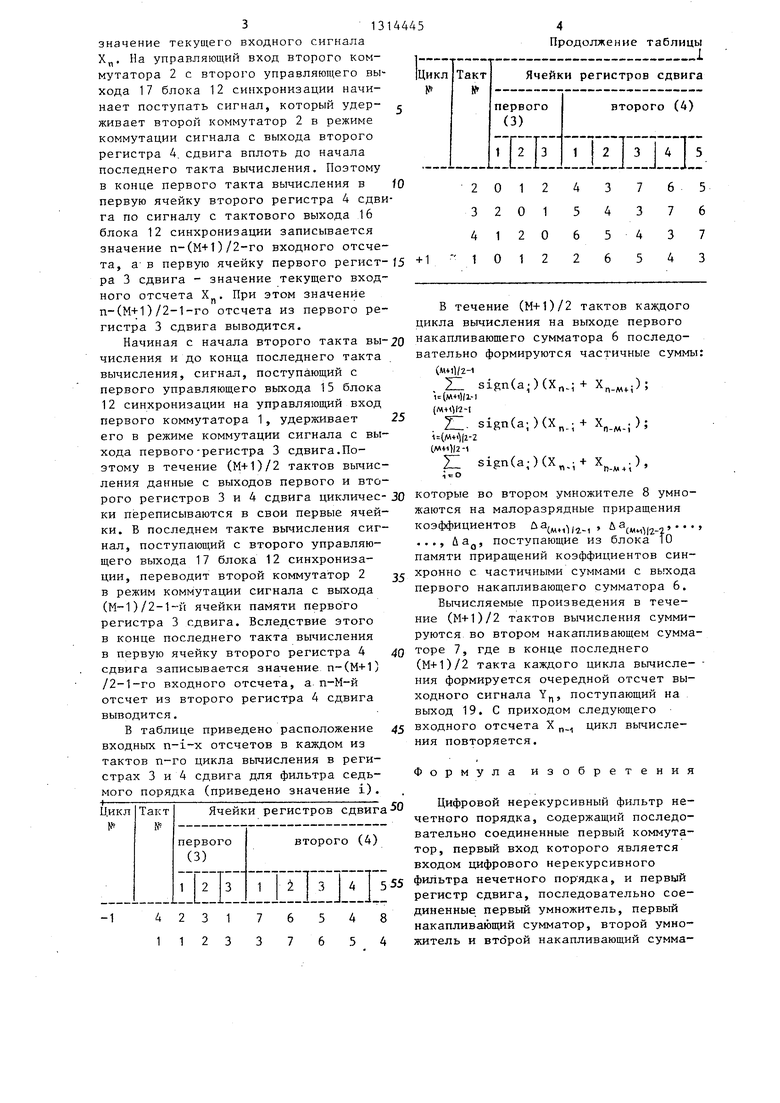

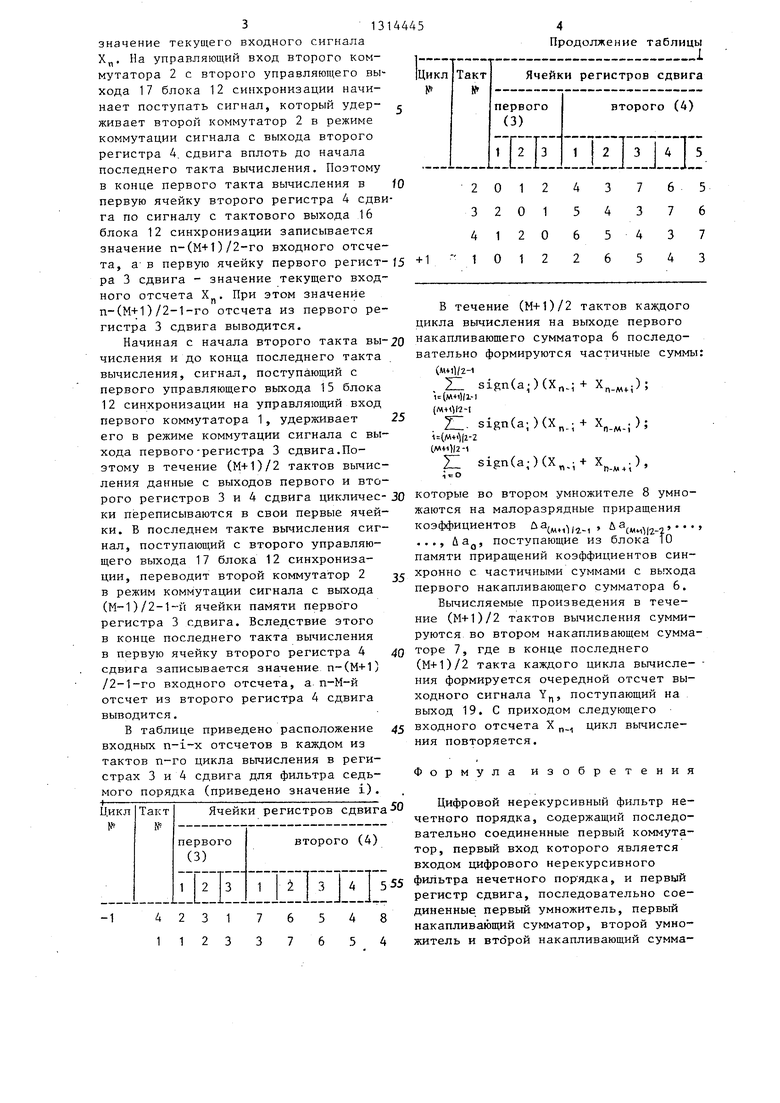

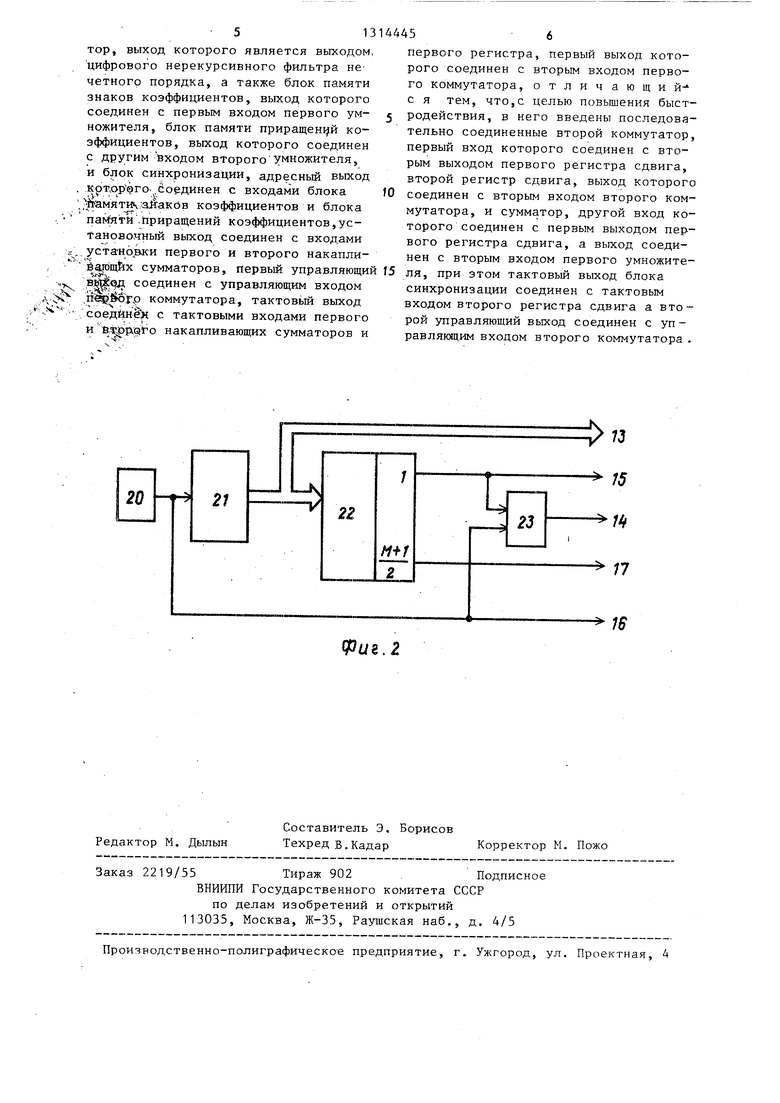

На фиг. 1 представлена структурная электрическая схема цифрового нере-., курсивного фильтра нечетного порядка; на фиг. 2 - схема блока синхронизации

Цифровой нерекурсивный фильтр нечетного порядка (фиг. 1) содержит первый и второй коммутаторы 1 и 2, первый и второй регистры 3 и 4 сдвига, сумматор 5, первый и второй накапливающие сумматоры 6 и 7, второй умножитель 8, первый умножитель 9, блок 10 памяти приращений- коэффициентов, блок 11 памяти знаков коэффициентов, блок 12 синхронизации, адресный выход 13 блока синхронизации,установочный выход 14 блока синхронизации, первый управляющий выход 15 блока синхронизации, тактовый выход 16 блока синхронизации, второй управляющий выход 17 блока синхронизации, вход 18 и выход 19 цифрового нерекурсивного фильтра нечетного порядка.

Yn

Блок 12 синхронизации (фиг. 2) содержит генератор 20 тактовых импульсов, счетчик 21, дешифратор 22j элемент И 23.

fO

Цифровой нерекурсивный фильтр нечетного порядка работает- следующим

образом, i

Рассмотрим алгоритм его работы, который получим на основе алгоритма свертки:

15

м

z:.

X,

(О

20

Учитывая, что коэффициенты фильтрации нерекурсивных фильтров, как правило, симметричны, то (1) можно преобразовать для фильтра нечетного к виду

(М-и№-1

Yn i;a

1гО

(Х„.,- Х,.„.; ).

(2)

7

Выражение (2) можно преобразовать - путем замены весовых коэффициентов а; их приращениями ua; а; - а,-,, где йао а,,. и их знаками sign(a;)

(a6)(X + Х,„) + (&а„+йа,) sign(a ,) (Х„., + Х,„„) + + ...+ ua«+ua,-f...+ua,,,,,,(,,,,.,x(,,,+X,j,,,

(М-я)/г-1 (M4)(2

Il&aj 21 si8n(a;)(X,.. +Х„,;).(3)

i--j

j o

Из выражения (3) видно, что для числения в правой (выходной) ячейке формирования каждого выходного отсче- 35 памяти первого регистра 3 сдвига

та необходимо просуммировать симметрично расположенные выборки входных сигналов,сформировать произведения полученных сумм на знаки соответствующих коэффициентов, из которых затем сформировать (M-f1)/2 частичных сумм входных выборок, умножить их на соответствую1дие приращения коэффициентов и результаты сложить между собой, причем формирование сумм симметрично расположенных входных выборок необходимо начинать с суммы п-(М+1)/2-1 и п-(М+1)/2 отсчетов, а заканчивать суммой п и п-М отсчетов.

Указанный алгоритм реализуется следующим образом„

В начале каждого цикла вычисления сигнал, поступающий с установочного выхода 14 блока 12 синхронизации.

производит обнуление первого и второ- 55 пающий с первого управляющего выхода го накапливающих сумматоров 6 и 7. 15 блока 12 синхронизации, переключает первый коммутатор 1 в режим коммутации сигнала с входа 18 и на вход первого регистра 3 сдвига поступает

Запись в первый и второй регистры 3 и 4 сдвига организована таким образом, что в начале каж,дого цикла выт13144452

Блок 12 синхронизации (фиг. 2) содержит генератор 20 тактовых импульсов, счетчик 21, дешифратор 22j элемент И 23.

Цифровой нерекурсивный фильтр нечетного порядка работает- следующим

образом, i

Рассмотрим алгоритм его работы, который получим на основе алгоритма свертки:

м

z:.

X,

(О

Учитывая, что коэффициенты фильтрации нерекурсивных фильтров, как правило, симметричны, то (1) можно преобразовать для фильтра нечетного к виду

(М-и№-1

i;a

1гО

(Х„.,- Х,.„.; ).

(2)

Выражение (2) можно преобразовать путем замены весовых коэффициентов а; их приращениями ua; а; - а,-,, где йао а,,. и их знаками sign(a;):

хранится значение п-(М-ь1)/2-1-го входного отсчета, а в каждой ячейке левее - значения отсчетов с номерами на единицу меньше. В то же время

в правой ячейке памяти второго реги- стра 4 сдвига записано значение п-(М+1)/2-го входного отсчета, а в каждой ячейке левее - значения отсчетов с номерами на единицу больше. Поэтому в первом такте вычисления в : первый накапливающий сумматор 6 через первый умножитель 9 на -1-1 и сумматор 5 с выходов первого и второго регистров 3 и 4 сдвига поступает произведение сумт-1ы п-(М+1)/2-1-го и

п-(М+1)/2-го входных отсчетов, умноженной на знак ()/2-1-го коэффициента.

Одновременно с этим сигнал, посту313

значение текущего входного сигнала Х„. На управляющий вход второго коммутатора 2 с второго управляющего выхода 17 блока 12 синхронизации начинает поступать сигнал, который удер- живает второй коммутатор 2 в режиме коммутации сигнала с выхода второго регистра 4, сдвига вплоть до начала последнего такта вычисления. Поэтому в конце первого такта вычисления в первую ячейку второго регистра 4 сдвига по сигналу с тактового выхода 16 блока 12 синхронизации записывается значение п-(М-И)/2-го входного отсчета, а- в первую ячейку первого регистра 3 сдвига - значение текущего входного отсчета Х. При этом значение п-(М+1)/2-1-го отсчета из первого регистра 3 сдвига выводится.

Начиная с начала второго такта вычисления и до конца последнего такта вычисления, сигнал, поступающий с первого управляющего выхода 15 блока 12 синхронизации на управляющий вход первого коммутатора 1, удерживает его в режиме коммутации сигнала с выхода первого-регистра 3 сдвига.Поэтому в течение (М+1)/2 тактов вычисления данные с выходов первого и второго регистров 3 и 4 сдвига циклически переписываются в свои первые ячейки. В последнем такте вычисления сигнал, поступающий с второго управляющего выхода 17 блока 12 синхронизации, переводит второй коммутатор 2 в режим коммутации сигнала с выхода (М-1)/2-1-й ячейки памяти первого регистра 3 сдвига. Вследствие этого в конце последнего такта вычисления в первую ячейку второго регистра 4 сдвига записывается значение п-(М+1) /2-1-го входного отсчета, а п-М-й отсчет из второго регистра 4 сдвига выводится.

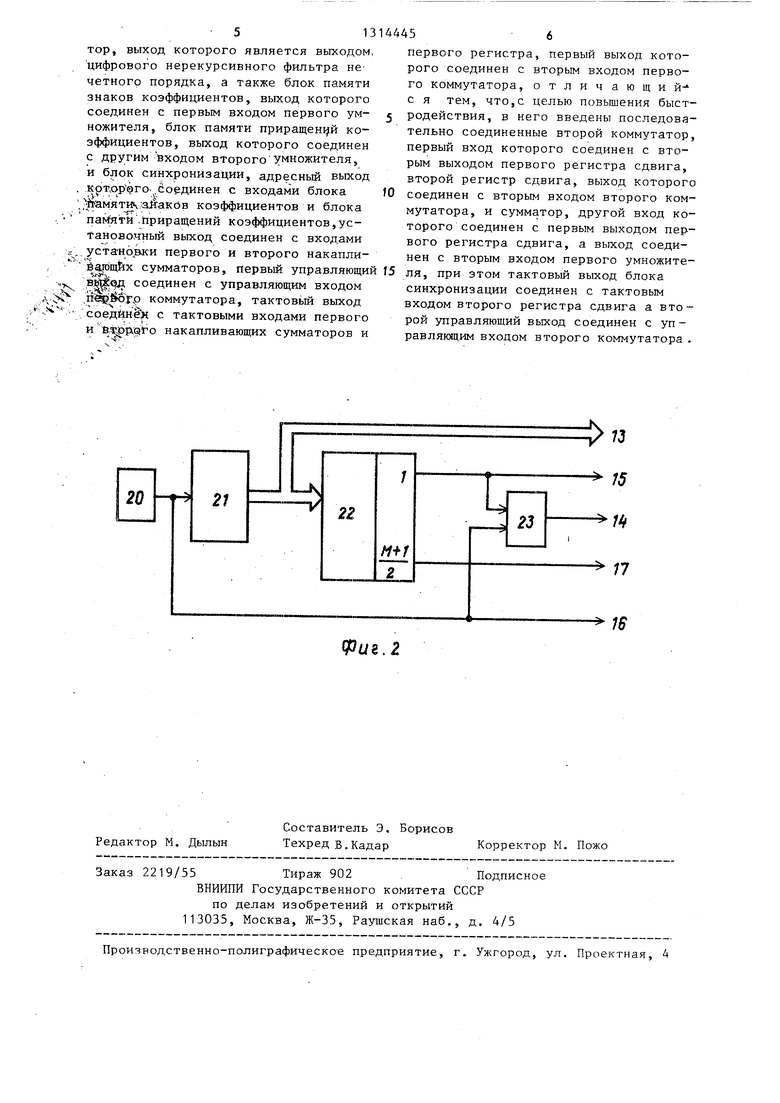

В таблице приведено расположение входных n-i-x отсчетов в каждом из тактов п-го цикла вычисления в регистрах 3 и 4 сдвига для фильтра седьмого порядка (приведено значение i).

-1

4231 1123

Продолжение таблицы

O 5

0 5 0 5 0

5

0

В течение (Мн-1)/2 тактов каж,дого цикла вычисления на выходе первого накапливающего сумматора 6 последовательно формируются частичные суммы:

(M+ll/2-l

. 21 sign(a.)(X.;+ Х„.,;);

1()/l-l (M+1V7-I

. sign(a;)(X.;+ X..j);

A(M+ (l-2

CMti);2 -1 i: sign(a;)(X,.;-b X.),

которые BO втором умножителе 8 умножаются на малоразрядные приращения коэффициентов Ла,,, , ,

йЯд, поступающие из блока

0

памяти приращений коэффициентов синхронию с частичными суммами с выхода первого накапливающего сумматора 6. Вычисляемые произведения в течение (М+1)/2 тактов вычисления суммируются во втором накапливающем сумматоре 7, где в конце последнего (М-ь1)/2 такта каждого цикла вычисле- - ния формируется очередной отсчет выходного сигнала Y, поступающий на выход 19. С приходом следующего входного отсчета X „ цикл вьгчисле- ния повторяется.

Формула изобретения

Цифровой нерекурсивный фильтр нечетного порядка, содержащий последовательно соединенные первый коммутатор, первый вход которого является входом цифрового нерекурсивного фильтра нечетного пор ядка, и первый регистр сдвига, последовательно соединенные первый умножитель, первый накапливающий сумматор, второй умножитель и второй накапливающий сумматор, выход которого является выходом, цифрового нерекурсивного фильтра нечетного порядка, а также блок памяти знаков коэффициентов, выход которого соединен с первым входом первого умножителя, блок памяти приращен1 й коэффициентов, выход которого соединен с другим входом второго умножителя, и блок синхронизации, адресный выход . крт,ор (эго .ёоединен с входами блока .амятич. зАаков коэффициентов и блока паМ;ятй .приращений коэффициентов,ус- Тановоиный выход соединен с входами установки первого и второго накаплиЛ Сf-..

ёагощйх сумматоров, первый управляющий f5 ля, при этом тактовый выход блока зв.ед соединен с управляющим входом коммутатора, тактовьш выход соедйне) с тактовыми входами первого

синхронизации соединен с тактовым входом второго регистра сдвига а в рой управляющий выход соединен с у равляющим входом второго коммутато

и BiiopiGjt o накапливающих сумматоров и

20

21

22

Редактор М. Дылын

Составитель Э. Борисов

Техред В.КадарКорректор М. Пожо

Заказ 2219/55Тираж 902Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

144456

первого регистра, первый выход которого соединен с вторым входом первого коммутатора, отличающий- с я тем, что,с целью повышения быст- 5 родействия, в него введены последовательно соединенные второй коммутатор, первый вход которого соединен с вторым выходом первого регистра сдвига, второй регистр сдвига, выход которого О соединен с вторьм входом второго коммутатора, и сумматор, другой вход которого соединен с первым выходом первого регистра сдвига, а выход соединен с вторым входом первого умножителя, при этом тактовый выход блока

синхронизации соединен с тактовым входом второго регистра сдвига а второй управляющий выход соединен с уп - равляющим входом второго коммутатора .

23

Н±Г 2

- 77

ив.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1332519A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1483608A1 |

| Цифровой нерекурсивный фильтр | 1980 |

|

SU942247A1 |

| Устройство для контроля цифровых нерекурсивных фильтров | 1986 |

|

SU1406731A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Нерекурсивный цифровой фильтр-дециматор | 1986 |

|

SU1354394A1 |

| Цифровой нерекурсивный фильтр | 1989 |

|

SU1665502A1 |

| Цифровой фильтр | 1986 |

|

SU1357976A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьше- ние быстродействия. Устр-во содержит два коммутатора 1 и 2, два регистра сдвига (PC) 3 и 4, сумматор 5, два . накапливающих сумматора 6 и 7, два умножителя 8 и 9, блок памяти 10 приращений коэффициентов, блок памя- ти 11 знаков коэффициентов и блок синхронизации (БС) 12. Для формирования каждого выходного отсчета в устр-ве осуществляются следующие операции: суммирование симметрично расположенных выборок входных сигналов, формирование произведения полученных сумм на знаки соответствующих коэффициентов, из которых затем формируют частичные суммы входных выборок, умножение их на соответствующие приращения коэффициентов и сложение результатов между собой. Цель достигается введением коммутатора 2, PC 4 и сумматора 5. Дана схема БС 12. 2 ид. 1 табл. СЛ 8ьао, : 4 4 СЛ

| Цифровой нерекурсивный фильтр | 1980 |

|

SU942247A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПОЯСНОЙ ПРИБОР ДЛЯ НОСКИ ЖИДКОСТЕЙ В ВЕДРАХ | 1923 |

|

SU1124A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-05-30—Публикация

1985-11-18—Подача