пторого сумматора сотен, вход перено которого соединены соответственса которого соединен с выходом пере но с выходами второго и треть-i носа первого сумматора сотен, вторые его сумматора единиц и десятпходы первого и второго разрядов ков.

1193824

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехдекадный преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU943705A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1005027A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU930313A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU955039A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОдаСЯТИЧНОГО КОДА в двоичный, содержащий сумматор единиц и десятков, первый и второй сумматоры сотен и сумматор результата, первая группа входов которого соединена с выходами первого и второго сумматоров сотен в соответствии с весами разрядов, вход первого разряда преобразователя является выходом первого разряда преобразователя, входы второго, третьего и четвертого разрядов которого соединены соотве Т ственно с первыми входами сумматора единиц и десятков, вькод первого разряда которого является выходом второго разряда преобразователя, входы пятого, шестого и седьмого разрядов которого соединены соответственно с второй группой входов сумматора единиц и десятковд входы девятого, десятого и 1одиннаддатого разрядов преобразователя соединены с первой группой входов второго сумматора сотен, входы десятого, одиннадцатоГо и двенадцатого разрядов преобразователя соединены соответственно с первой группой входов второго, третьего и четвертого разря дов первого сумматора сотен и второй группой входов первого, второго li третьего разрядов второго сумматора сотен, вход девятого разряда Преобразователя соединен с вторым входом четвертого разряда первого сумматора сотен, вход переноса которого, входы переноса сумматора единиц и десятков, сумматор результата и второй вход пятого разряда сумматора результата соединены с входом логического нуля преобразователя, выходы с четвертого по восьмой разрядов которого соединены соответственно с выходами с первого по пятый разрядов сумматора результата, отличающийся, i тем, что, с целью упрощения преобразователя, он содержит три элемента СЛ .ИЛИ, первые входы которых соединены соотвественно с выходами переноса сумматора единиц и сотен, второго сумматора сотен и сумматора результата, вторые входы с первого по четвертьи разрядов которого соединены соответственно с входами с пятого (Г по восьмой разрядов преобразователя, выход третьего разряда -которого соединен с выходом первого разряда первого сумматора сотен, первый вход liU первого разряда которого соединен с входом девятого разряда преобра;зователя, входы восьмого и двенадцатого ра зрядов которого соединены с вторыми входами первого и второго элементов ШЖ, выходы которых соединены соответственно с вторым входом третьего разряда первого сумматора сотен и выходом десятого разряда преобразователя, выход девятого разряда которого соединен с выходом третьего эелемента ИЛИ, второй вход которого соединен с выходом третьего разряда

Изобретение Относится к цифровой вычислительной технике и может быть использовано при построении устройств ввода информацииj станков с программным управлением графопостроителей икассовых аппаратов.

Целью изобретения является упрощение преобразователя.

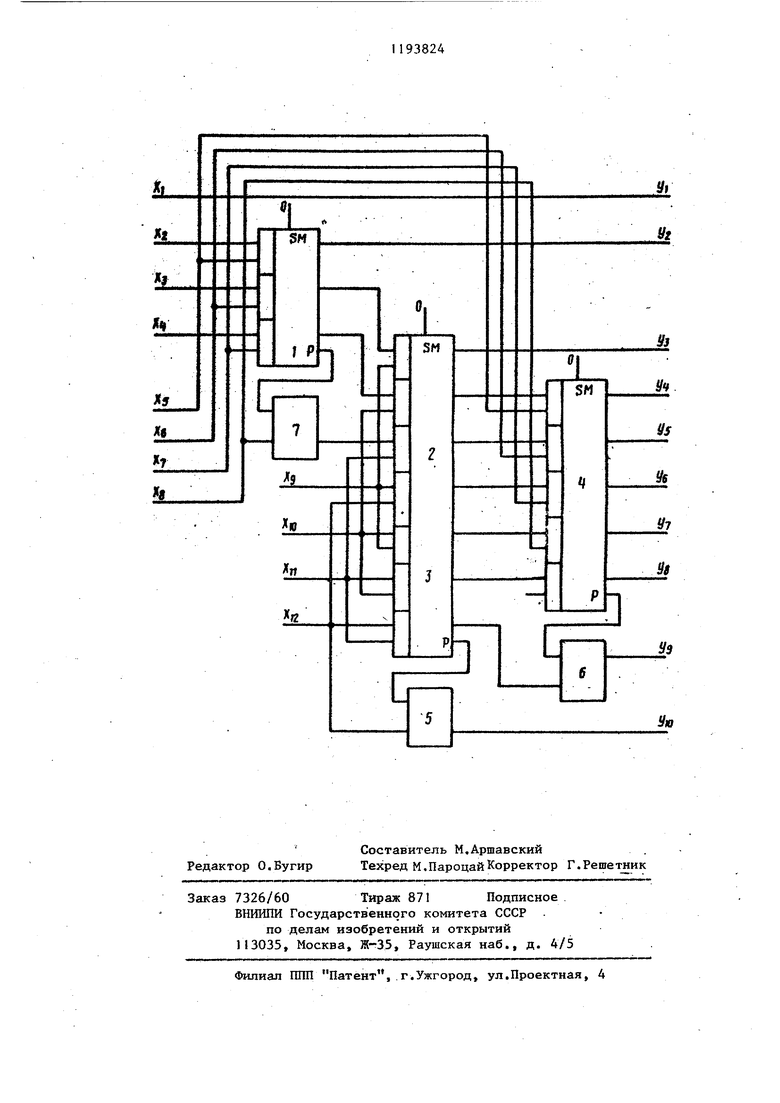

На чертеже приведена функциональная схема предлагаемого преобразователя .

Устройство соедржит сумматор 1 единиц и десятков, первый 2 и второй 3 сумматоры сотен, сумматор 4 результата, элементы ИЛИ 5-7, Х - X,j входы преобразователя, Y, - У,,, - выходы преобразователя, причем входы Х.-Х с первого по четвертый разрядов являются входами единиц, входы X -Xjвходами десятков, а входы входами сотен.

Нарастание веса разрядов на чертеже идет сверху вниз.

Преобразователь работает следуюпдам образом.

Работа предлагаемого устройства прослеживается на примере преобразования любого числа от О до 999. Пусть введено число 358. Сразу определяется Y,. Сумматор I формирует сигналы

1, и ita выходе переноса - 1.

Y2 Сумматоры, 2 и 3 формируют Y 1, и на выходе переноса-0, т.е. элемент ИЛИ 5 выдает сигнал Yio 0. Сумматор 4 формирует Y4 О, Yy О, Y 1.

О, и на выходе пере1

носа - О, Поскольку на элемент ИЛИ 7 поступает единица с выхода третьего разряда сумматора 3, Y 1. Таким. образом, на выходе формируется число (МО 100110- 358,0.

k

3M

lL

Д

I p

A.

Хю

Xn

/i

Уг

9з

SM

yt

SM

Us

Уб

У7

3i

5

УЮ

| Трехдекадный преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU943705A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU930313A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-22—Подача