(54) МИКРОПРОГРАММНАЯ СИСТЕМА ОБРАБОТКИ

ДАННЫХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Система обработки данных | 1980 |

|

SU1003063A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1982 |

|

SU1130879A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Микропрограммное устройство управления | 1981 |

|

SU959078A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

1

Изобретение относится тс вычиспитепьной технике и предназначено для применения в системах управления цифровых вычислительных машин с ; микропрограммным управлением, например, в модульных микро-ЭВМ, содержащих несколько одинаковых или различных БИС, предназначе ных для преобразования информации, и одни или несколько БИС, образующих устройство микропрограммного управления. JQ

Известны микропрограммные блоки обработки данных и устройства микропрограммного управления, содержащие один блок преобразования информации, запоминающее устройство, регистры, дещифрато- is ры и схемы управления i .

Недостатками данных устройств являются неэффективное использование микропрограммной памяти и потери в быстродействии, связанньш с тем, что при ус- -20 ловных переходах необходимо задерживать выборку следующей микрокоманды до завершения вьшолнения в блоке преобразования информации текущей микрокоманды и образования признаков результата.

Наиболее близкой к предлагаемой по технической .-сущности, является микропрограммная система обработки данньгх, применение которой позволяет повысить быстродействие устройства и эффективность использования микропрограммной

памяти XI

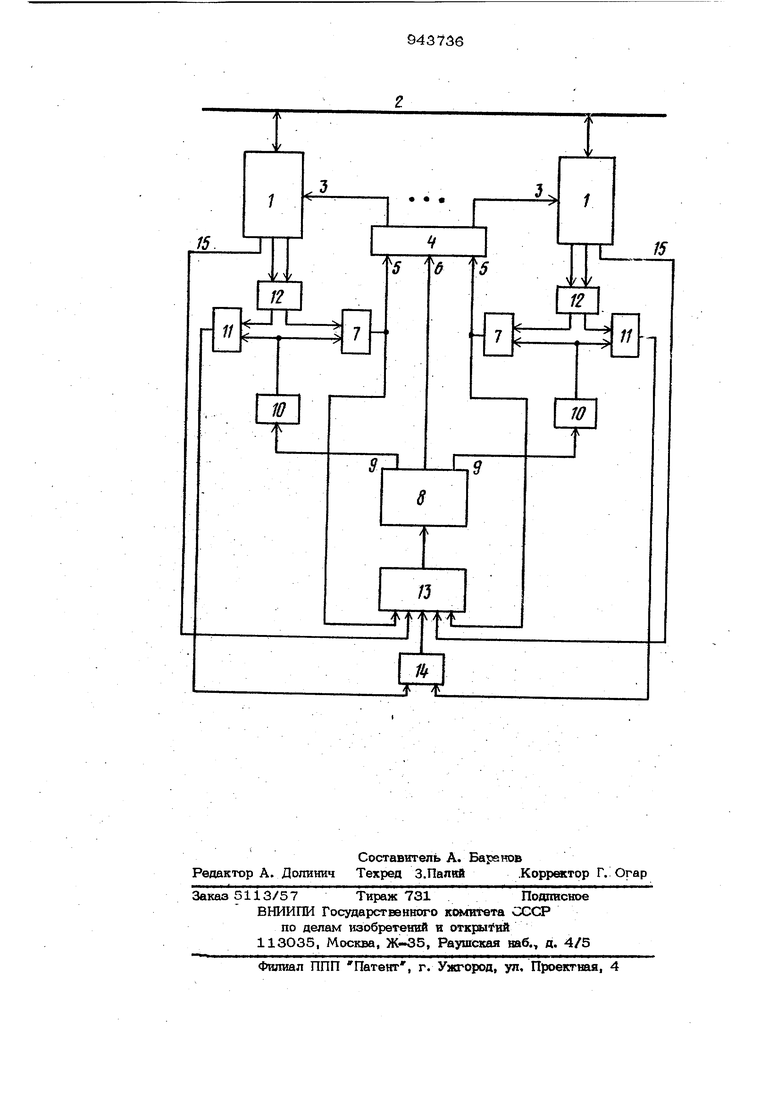

Система содержит несколько блоков преобразования информации, каждый из которых имеет шину условий, подключенную к соответствующему входу блока управления последовательностью микрок(данд. Управляющие входы блоков подключены к выходам демупьтшшексора, информационный вход которого подкшочен к выходу блока микропрограммной памяти. Вход микропрограммной памяти подключен к выходу регистра адреса, который подключен также ко входу блока. Выходы разрядов циклического .сдвигового регист р& приключены к управляюшим 39-1 входам демультиллоксоро и блока управ- лсмшя последовите.шлгостью ктикрокоманд. IIpiHHiran работы системы заключается п следующем. Из блока микропрограммной памяти, хранящего MUKponporpaMNdbi, по которым должны работать блоки преобразоват я информации, через постоянные временные интервалы, задаваемые схемами синхро шзатт, считываются микрокоманды. Каж дая считанная микрокоманда с выхода бло ка поступает на вход демультиплексора, а затем на вход блока преобразования информации, которому соответствует разрешающее значешш определенного разряда регистра и соответствующего управляющего входа демультиплексора. В соответствующем блоке начинает отрабатываться микрокоманда. Поступив на управляющий вход блока управления последовательностью микрокоманд то же разрещаю щее значение регистра разрешает формирование блоком следующего адреса для микрокоманды очередного блока, для которого на его шине условий выставлены признаки результата п :гедыдушей микрококоманды. Сформированный блоком адрес, в зависимости от значения содержимого регистра адреса и признаков условий на щине, передается на регистр адреса, осушествляется сдвиг в регистре, и на выхо дах микропрограммной памяти появляется новая микрокоманда. Таким образом, несколько блоков преобразования информашга управляются от общего блока микропрограммной памяти в режиме разделения времени. Если процесс переработки информации можно распараллелить между несколькими обрабатывающими блоками или если блоки преобразования информации работают по независимым микропрограм мам, то описанная система позволяет повысить общее быстродействие и повысить эффективность использования микропрограммной памяш, так как сокращаются потери времени из-за ее простоев в случае условных переходов. Действительно, микропрограммная память не ждет признаков результата операшга, как в случае с одним блоком преобразования информации, а осуществляет выдачу микрокоманды для другого блока 2. Однако извёстн1 е устройство обладает следующими недостатками. Порядок и последовательность блоков преобразования информпадш строго определен последовательностью выдачи разрещающих сигналов цикличес-ктгм сдвиговым регист04ром. Фактически , считатюя микрокоманда может быть послана только в один блок преобразования информации, тем самым исключень обмен инфop Iaциeй между блоками и одновременное управление несколькими блоками. Кроме того, в известном устройстве микрокоманды из микропрограммной памяти считываются через постоянные временные интервалы, которые равны циклу микропрограммной памяти и не ведут к ее простою только тогда, когда правильно выбрано соотношение между циклом микропрограммной памяти, количеством блоков преобразования информации, а также если время выполнения микрокоманд в разных блоках одинаково. Иначе указанные временные интервалы выбираются, исходя из быстродействия самого медленного блока преобразования информации, что снижает быстродействие системы. Цель изобретения - увеличение функциональных возможностей и увеличение быстродействия. Указанная цель достигается тем, что в устройство, содержащее группу обра v-батывающих блоков, блок микропрограммной памяти, блок управления, коммутатор, причем входы-выходы обрабатывающих блоков группы являются входамивыходами системы, первые выходы обрабатывающих блоков группы подключены соответственно к группе входов блока управления, а входы обрабатывающих блоков группы соединены соответственно с выходами коммутатора, информационный вход которого соединен с выходом блока микропрограммной памяти, вход которой подключен к выходу блока управления, введены группа триггеров занятости, группа триггеров управления, первая и вторая группы элементов И, элемент ИЛИ, причем вторые и третьи выходы обрабатывающих блоков группы подключены ко входам соответствующих триггеров занятости группы, первые выходы триггеров занятости группы подключены к первым входам соответствующих элементов И первой группы, а вторые выходы триггеров занятости группы соединены с первыми входами соответствующих элементов И второй группы, при этом вторые входы элементов И первой и второй грутш подключены к выходам соответствующих триггеров управления группы, выходы элементов И первой группы соединены со входами элемента ИЛИ , выход которого соединен с первым управляющим входом I блока управления, выходы элементов И второй группы подключены ко входам коммутатора и вторым управляющим входам блока управления, а входы тригге- ров управления группы подключены к вых дам блока микропрограммной памяти. Схема предлагаемой микропрограммной системы обработки данных приведена на чертеже. Группа обрабатывающих блоков 1 связана между собой шиной данных 2. Упреш ляющий вход ,3 каждого обрабатывающег блока 1 подключен к соответствующему выходу коммутатора 4, и гeющeгo входы 5 и 6. Ко входам 5 подключены выходы элементов И второй группы 7, а вход 6 подключен к первому выходу блока микропрограммной памяти 8, имеющей вторые выходы 9, связанные с установочными входами триггеров группы управления 10. Выход каждого триггера группы управления 1О подключен ко вторым входам соответствующих элементов И 7 и элементов И 11, первые входы которых подключены соответственно к единичному и нулевому выходам триггера занятости группы 12. Триггеры занятости группы имеют нулевой и единичный установочные 1 ходь1, подключенные к соответствующим выходам обрабатывающего блока 1. Выходы элементов И 7 также подключены к соответствующим управляюпгак1 входам блока управления (последовательностью микрокоманд) 13, имеющего вход блокировки, связанный с выходом элемента ИЛИ 14. Ко входам элемента ИЛИ 14 подключены выходы элементов И первой группы 11. Каждый обрабатывающий бло имеет щину условий 15, подключенную к соответствующим входам блока управления последовательностью микрокоманд 13, выход которой подключен ко входу блока микропрограммной памяти 8. Синхронизирующие цепи, а также шина, свя- зывающая вход блока управления последо вательностью микрокоманд и выход блока микропрограммной памяти, включающий в себя, кроме накопителя, схемы дешифрации и регистр адреса, на чертеже не по- казаны. Предлагаемая микропрограммная система обработки данных работает следук щим образом. Из блока управления последовательностью микрокоманд 13 в блок микропрограммной памяти 8 подается адрес микрокоманды. Через интервал времени, необходимый для считывания информации ИЗ блока микропрограммной памяти 8, на выходах последней появляется информация, которая состоит из двух частей. Первая часть представляет собой микрокоманду, поступающую на информационный вход 6 ксммутатора 4. Вторая часть содержит количество разрядов, равное количеству обрабатывающих блоков 1. Сигнал с каждого разряда выхода 9 поступает на вход соответствующего триггера группы управления 10 и устанавливает его в состояние, соответствующее значению указанного разряда. Если триггер 10 устанавливается в 1, то его единичный выход при единичном состоянии триггера занятости 12 открывает элемент И 7, тем самьш- разрешая поступление микрокоманды через коммутатор 4 на управляющие входы 3 соответствующего обрабатывающего блока 1. Если же триггер Ю устанавливается в О, элемент И 7 по входу 5 коммутатора 4 запрещает прохождение микрокоманды на вход 3. Разрешающий сигнал с выхода элемента И 7, поступая на вход блока управления последовательностью микрокоманд 13, разрешает формирование и считывание следующей микрокомавды, адрес которой формируется, исходя из адресной части предыдущей микрокоманды или содерж1а1ого регистра адреса и состоя.ния шины условия 15 обрабатывающего блока 1, который к этому времени завершает выполнение своей макрокоманды. Если указать в одном дополнительном разряде соответствующей микрокоманды единицу, а в остальных нyлli, то данная мтасрокоманда управляет только соотвётствующ11М этой единице обрабатывающим блокич- 1. Если процесс переработки информащш можно распараллелить между несколькими обрабатывающттми блоками или если обрабатывающие блоки могут работать по независимым микропрограммам, то задавая единицы в разных разрядах микрокоманд соответствующих микропрограмм, можно управлять несколькими обрабатывающими блоками 1 от общего блока микропрограммной памяти 8 в режиме разделения времени. Поскольку в этся случае микропрограммная память не ждет признаков результата операции при условных переходах, а осуществляет выдачу микрокоманды для другого блока, то сокращаются потери времени из-за простоев памяти и увеличивается быстродействие по сравнению с системами с одним обрабатываюштоу блоком. Так как в общем случае обрабатывающие блоки 1 могут быть различными по фучкшюнальным возможностям, а также по быстродействию, то к моменту выдачи м1-гкрокоманды в некотором блоке 1 , может оказаться, что он не завершил вы полнение предыдущей микрокомавды. Чтобы этого не случ1шось, в момент вре м ени, когда некоторый обрабатывающий блок 1 начал отрабатывать поступив - Шую .на его - вход: микрокоманду, по установочному входу устанавливается в О триггер занятости 12, который уста Иавливается в 1 после заверщения выполнения микрокоманды. Если ira выходах блока микроирог эаммной памяти появляет ся микрокоманда, относящаяся к блоку 1 Триггер занятости которого находится в нуле, на выходе элемента И 11 появляет ся ОЕгнал, который через элемент ИЛИ 1 блокирует выдачу следующей микрокоманды. Таким образом, предыдущая микрокоманда на выходах блока микропрограммно памяти 8 не пропадает, а поступает в выбранный блок, как только триггер 12 установится в 1. В этот момент снимается блокировка на выходе элемента И 11 и открывается элемент И 7. Таким образом, интервалы времеш5, через которые происходит обращение к блоку .микропрограммной памяти 8, оп деляются не самым медленным обрабатывающим блоком, а по. крайней мере средним быстродействием входящих в сио тему обрабатывающих блоков. За счет этого повышается быстродействие систем Если указать единицу сразу в несколь ких разрядах, появляющихся на выходах 9 блока микропрограммной памяти то считанная микрокоманда подается сразу на несколько обрабатывающих блоков 1 одновременно. Это необходимо в случаях, когда указанньте блоки обрабатывают параллельно, например, старшие и младшие разряды информашш (наращив ние по разрядности), когда имеются специальные микрокоманды, обеспечивающие информационный обмен между блоками 1 по шине данных 2, когда одна и та же микрокоманда интерпретируется по разному различными обрабатывающими блоками 1 за счёт их настройки (коммутацией внешних связей или применением остаточного управления) и т. д. Таким образом, указание в самой микрокоманде одного или нескольких обрабатываюшж блоков 1 позволяет управлять последовательностью работы блока 1, осуществлять управление их одновременной работой (в случае необходиости) и, следовательно, увеличить функциональные возможности предлагаемой системы по сравнению с известиыми. Предлагаемая--микропрограммная система обработки данных применяется в икро-ЭВМ, выполненной на больших интегральных схемах. Фомула изобретения Микропрограммная система обработки данных, содержащая группу обрабатывающих блокой, блок микропрсж-раммной памяти, блок управления, коммутатор, причем входы-выходы обрабатывающих блоков грутшы являются . входами-выходами системы, первые выходы обрабатывающих блоков группы подключены соответственно к группе входов блока управления, а входы обрабатывающих блоков группы соединены соответственно с выходами коммутатора, информационный вход которого соединен с выходсм блока микропрограммной памяти, вход которого подключен к выходу блока управления, отличающаяс я тем, что с целью повышения быстродействия, в него введены группа триггеров занятости, группа триггеров управления, первая и вторая группы элементов И, элемент ИЛИ, причем вторые и третьи выходы обрабатывающих блоков грушхы подключены ко входам соответствующих триггеров занятости группы, первые выходы триггеров занятости группы подключены к первым входам соответствующих элементов И первой группы, а вторые выходы триггеров занятости группы соединены с первыми входами соответствующих, элементов И второй группы, при этом вторые входы элементов И Первой и второй групп подключены к выходам соответствующих триггеров управления группы, выходы элементов И первой групгаы соединены со входами элемента ИЛИ, выход которого соединен с первым управляющим входом блока управленнил, выходЬ элементов И второй группы подключены ко входам коммутатора и вторым управляющим входам блока управления, а входы триггеров управления группы подключены к выходам блока микропрограммной памяти. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 342380, кл, G, 06 F 9/00, 1968. 2.Патент США № 3689895, кл. 342-172.5, 1972 (прототип).

Авторы

Даты

1982-07-15—Публикация

1977-12-15—Подача