(St) УИНОМИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный генератор импульсов | 1989 |

|

SU1619440A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

| Устройство для контроля фазочастотных характеристик четырехполюсников | 1989 |

|

SU1758600A1 |

| Умножитель частоты периодических импульсов | 1980 |

|

SU935956A1 |

| Генератор качающейся частоты | 1982 |

|

SU1053261A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСОВ | 1979 |

|

SU826343A1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Умножитель частоты | 1986 |

|

SU1385230A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

1

Изобретение относится к радиотехнике и может использоваться для умножения частоты сигналовв цифровых устройствах различного назначения. .

Известен умножитель частоты, содержащий последовательно соединенные накопительный счетчик, регистр памяти, первый делитель частоты и преобразователь импульсного сигнала в гармонический, а также второй делитель частоты и перестраиваемый генератор тактовых импульсов, выход которого соединен с сигнальными входами первого и второго делителей частоты 1 :

Однако в известном умножителе частоты имеется несинхронность частоты следования входных импульсов и частоты следования импульсов измерительной формируемой последовательности, что приводит к возникновению разрывов фазы выходного гармонического сигнала, следствием чего .

является появление в спектре выходного сигнала побочных гармоник, а также к сужению диапазона входных частот при сохранении заданной точности умножения.

Цель изобретения - уменьшение линейных искажений при одновременном расширении диапазона входных частот.

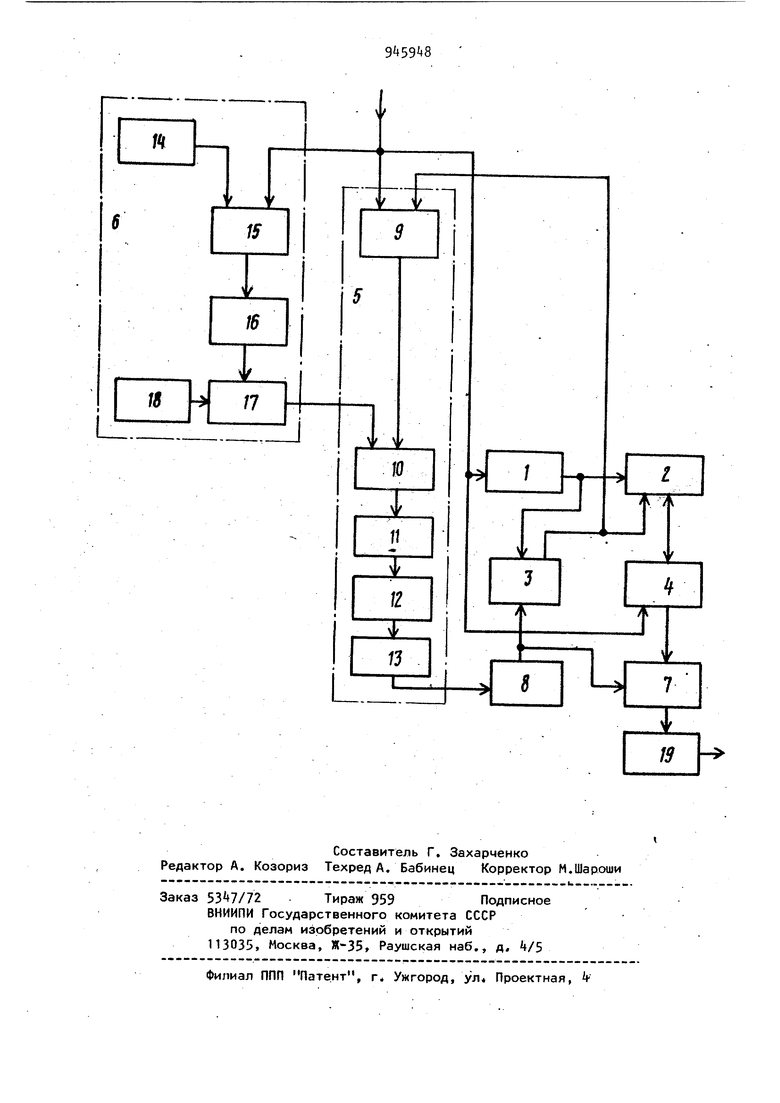

Для этого в умножитель частоты, содержащий последовательно соединен10ные накопительный счетчик, регистр памяти, первый делитель частоты и преобразователь импульсного сигнала в гармоничесий, а также второй делитель частоты и перестраиваемый ге15нератор тактовых импульсов, выход которого соединен с сигнальными входами первого и второго делителей частоты, введены последовательно , соединенные блок стабилизации уси20ления и блок автоматической подстройки кратности частот, выход которого соединен с управлящим входом, перестраиваемого генератора такте8ЫХ импульсов, a также блок задержки, выход которого соединен с сигнальным входом .накопительного счетчика и управлящим входом эторого делителя частоты, при этом выход второго делителя мастоты соединен со счетным входом накопительного счетчика и первым сигнальным входом блока автоматической подстройки кратности частот, а вход блока стабилизации усиления, второй сиг,1нальный вход блока автоматической подстройки кратности частот, вход блока задержки и управляющий вход pe гистра памяти объединены и точка их соединения является входом умножителя частоты. При этом блок стабилизации усиления содержит последовательно соединенные первый генератор тактовых импульсов, элемент.И, накопительный счетчик и управляемый делитель частоты, к входу которого подключен выход второго генератора тактовых импульсов, при этом второй вход элемента И является входом, а выход управляемого делителя частоты - выходом блока стабилизации усиления, Блок автоматической подстройки кратности частот содержит последовательно соединенные формироватввль сигнала ошибки; элемент И, реверсивный счетчик, цифроаналогойый преобразователь и усилитель, при этом первый и второй входы формирователя сигнала ошибки являются соответствеи но первым и вторым сигнальными входа ми, а выход усилителя - выходом блок автоматической подстройки кратности частот. На чертеже представлена структурная электрическая схема предложенного устройства. Умножитель частоты содержит блЬк J задержки, накопительный счетчик 2 второй делитель 3 частоты, регистр 4 памяти, блок f автоматической под- . стройки кратности частот, блок 6 стабилизации усиления, первый делитель 7 частоты, перестраиваемый ге нератор 8 тактовых импульсов. Блок 5 автоматической подстройки кратности частот содержит формирователь 9 сигнала ошибки,элемент И 10, реверсивный счетчик 11, цифрозналоговый преобоазователь С ЦАП )12 и усилитель 13. Блок 6 стабилизации усиления содержит первый генератор I тактовых импульсов, элемент И 15, накопительный счетчик 16, управляемый делитель 17 частоты и второй генератор 18 тактовых импульсов, К выходу второго делителя частоты 7 подключен преобразователь 19 импульсного сигнала в гармонический. Умножитель частоты работает следующим образом. Соотношение между частотами следования импульсов, формируемых генератором 14 и генератором 18, определяется условием обеспечения устой-чивости цепи автомотической подстройки кратности частот цифрового умножителя: « , где f - частота следования тактовых импульсов, формируемь х генератором 14; частота следования тактовых импульсов, формируемых генератором 18; крутизна генератора 8 тактовых импульсов; коэффициент усиления усилителя 13; начальный период перестраиваемого генератора 8 тактовых импульсов, В J-ый период умножаемой частоты f 1-ый входной импульс поступает через блок 1 задержки на сигнальный вход накопительного счетчика 2 и управляющий вход делителя 3. частоты, а также непосредственно на управляющий вход регистра 4 памяти, первый сигнальный вход блока 5 и вход блока 6. При этом регистр Ц памяти фиксирует информацию с выхода накопительного счетчика 2 Блок 1 задержки обе спечивает задержку 1-го импульса на вреМя Т . При поступлении задержанного на время ТГ 1-го импульса умножаемой частоты fy на управляющие вхо ды накопительного счетчика 2 и делителя частоты 3 происходит сброс накопительного счетчика 2 и делителя 3 частоты в нуль. Генератор 8 формирует импульсы с периодом Т0(i), Делитель 3 частоты осуществляет умножение периода 1 (I) следования тактовых импульсов генератора 8 в п раз. Импульсы с периодом следования Т О) ,{О с выхода делителя 3 частоты поступают на счетный вход накопительного счетчика 2, который осуществляет измерение длительности Ту I-го периода

,5

следования импульсов умножаемой частоты путем подсчета числа fJ( импульсов с периодом Т(i), поступающих на его вход за период

- -Hijtn-t -€

где Ту - i-ый период следования импульсов умножаемой частоть

. , :

T.,(i)- длительность периода следования тактовых импульсов в i-M периоде следования

импульсов умножаемой частоты f.

X

коэффициент деления часто

п ты делителя 3, равный требуемому коэффициенту умножения цифрового умножителя:

t (i) - ошибка измерения Т,, вызванная конечной величиной дискрета п-Т.(|). Одновременно в i-м периоде следования импульсов умножаемой частоты fУ формирователь 9 сигнала ошибки осуществляет измерение модуля ошибки . t ( I ) и ее знака

t{i).i;.;(i) .

По окончании 1-го периода следования входных Импульсов сигнал ошибки t(i) с выхода формирователя 9 поступает на первый вход элемента И 10, Одновременно с сигналом ошибки t(I) на второй вход элемента И -10 поступает сигнал с блока 6 стабилизации усиления, Этот сигнал фор мируют в i-M периоде .следования импульсов умножаемой частоты следующим обраЗОМ.-; . ., . . . V: , .

Импульсы с периодом Т д, с генератора 14 пост;уг1ают на первый вход элемента И 15. Импульсы умножаемой . частоты fy поступают на второй вход элемента И 15 Счетчик 1б осуществляет грубое измерение длительности Т периода следования импульсов y iHOжаемой частоты f путем подсчета числа импульсов Q с периодом Т, поступающих на еГр вход за период TV Q,. :

Число Q с выхода счетчика 16 поступает на управляющий вход управляемого делителя 17.

Управляемый делитель 17 обеспечивает умножение периода Тд следования импульсов с генератора 18 на число Q.

В {I+1)-м периоде умножаемой частоты fjx импульсы с периодом следования ТБ-Q с выхода блока 6 поступают на второй вход элемента И 10, Ре- ;

версивный счетчик 11 осуществляет измерение ошибки t(l) путем подсчета числа N импульсов с периодом Tp.Q, поступающих на его вход за 5 время ошибки t(i)

N .:tti /orir.

ЦифроаналоговыГ1 преобразователь 12 формирует напряжение, пропорциональное коду N реверсивного счетчика to 11. Сигнал с выхода ЦАП 12 усиливается в К раз усилителем 13 и поступает на управляющий вход генератора 8. Под воздействием этого сигнала период следования тактовых импульсов 15 в зависимости от величины и знака ошибки t(i) изменяется таким образом, что ошибка t(i) уменьшается,

С приходом (i+l)-го импульса ум- . ножаемой частоты fj( регистр памяти 20 фиксирует число с выхода накопительного счетчика 2. Число Х с вы- хода регистра памяти вводится на управляющий вход делителя 7«На сигнальный вход делителя 7 поступают 25 импульсы с периодом Тр(1+1), Делитель 7 обеспечивает умножение периода следования импульсов T0(l-fl) на число /: .Преобразователь 19 осуществляет преобразование импульсного 30 сигнала в гармонический:.

В последующих тактах-работы умножителя величина ошибки уменьшается до нуля, и устанавливается режим крат частотъ. следования входных им пульсов и формируемой последователь35ности импульсов.. , ; Таким образом в предложенном умножителе частоты следования реализуется синхронность частоты следо-, д вания,входных импульсов и частоты .следования импульсов формируемой последовательности путём автоматического установления и поддержания кратности их периодов и обеспечивает тем самым положительный эффект 45уменьшение нелинейных искажений при одновременном расширении диапазона входных частот.

50

Формула изобретения

тактовых импульсов, выход которого соединен с сигнальными входами первого и второго делителей частоты, отличающийся тем, что, с целью уменьшения нелинейных искажений при одновременном расширении диапазона входных частот, в него ввдены последовательно соединенные блок стабилизации усиления и блок автоматической подстройки кратности частот, выход которого соединен с управляющим входом перестраиваемого генератора тактовых импульсов, а также блок задержки, выход которого соединен с сигнальным входом накопительного счетчика и управляющим входом второго делителя частоты, пр этом выход второго делителя частоты соединен со счетным входом накопительного счетчика и первым сигнальным входом блока автоматической подстройки кратности частот, а вход блока стабилизации усиления, второй сигнальный вход блока автоматической подстройки кратности частот, вход блока задержки и управляющий вход регистра памяти объединены и .точка их соединения является входом умножителя частоты.

входы формирователя сигнала ошибки являются соответственно первым и вторым сигнальными входами, а выход усилителя - выходом блока автоматической подстройки кратности частот.

Источники информации, принятые во внимание при экспертизе

1, Патент Великобритании № НЮЗЭО, кл. Н 03 К 5/00, опублик. 1976 (прототип).

Авторы

Даты

1982-07-23—Публикация

1980-12-09—Подача