Изобретение относится к вычислительной технике и может быть использовано при построении специализиро- ванных устройств для упорядоченного хранения и выдачи информации по безадресному принципу.

Известно запоминающее устройство, предназначенное для хранения и упорядоченного считывания информации, построенное на принципе сдвигающего регистра l.

Недостатком такого устройства является низкая надежность информации, так как выход из строя одного разряда сдвигающего регистра ведет к потере информации во всем разрядном сечении. Кроме того, при сдвиге всего массива вероятность сбоя на шинах передачи информации зависит от числа слов, хранящихся в запоминающем устройстве.

Наиболее близким по технической сущности к предлагаемому является стековое запоминающее устройство, содержащее реверсивнмй счетчик, выход которого соединен через дешифратор и вентили записи информации с входом элементов памяти, к вторым входам которых подключены информационные разрядные шины устройства 2 Недостатком известного устройства является низкая надежность хранения информации и возможность ее искажения в процессе считывания.

Цель изобретения - повышение надежности запоминающего устройства в процессе считывания информации.

Поставленная цель достигается тем, что в устройство, содержащее элемен10ты памяти, первые входы которых подключены к шине записи, вторые - к шине управления записью, третьи - к одной из информационных разрядных шин, четвертые - к шине установки в

15 О, пятые - к шине управления считыванием, выход элемента памяти подключен к другой разрядной шине, введены управляющие элементы памяти, первый выход каждого из которых, кро20ме последнего, подключен к пятому входу каждого из элементов памяти, второй выход каждого управляющего элемента памяти соединен с восьмым входом последующего управляющего

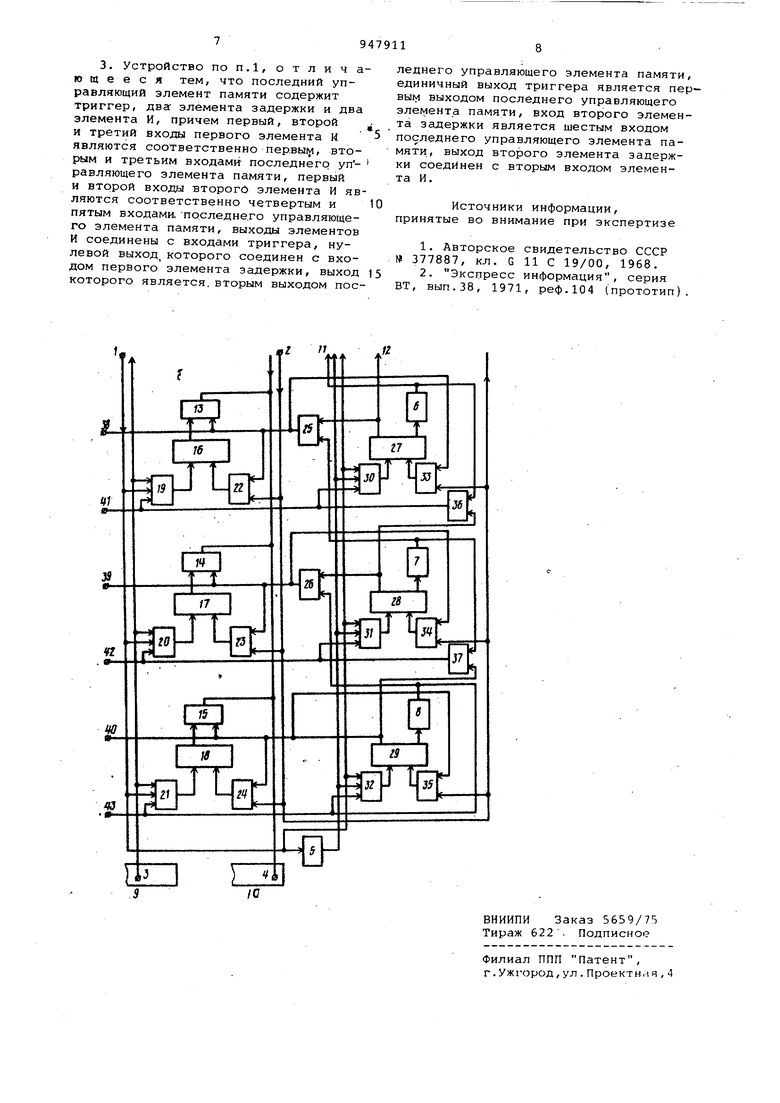

25 элемента памяти, первые и вторые входы каждого управляющего элемента памяти подключены соответственно к шинам записи и считывания, третьи входа) каждого управляющего элемента 30 памяти подключены к шинам управления записью, четвертые входы каждого управляющего элемента памяти подключены к шине Установка в О, пятые входы каждого управляющего элемента памяти соединены с первым выходом данного управляющего элемента памяти шестой и седьмоЯ входы каждого управ ляющего элемента памяти, кроме последнего, соединены соответственно с третьим выходом предыдущего управляю щего элемента памяти и восьмым входо последующего управляющего элемента памяти, шестой вход последнего управ ляющего элемента памяти подключен к шине записи. Кроме того, каждый управляющий элемент памяти, кроме последнего, со держит триггер, элементы И и элемент задержки, причем выход первого элемента И является первым выходом управляющего элемента памяти, один из входов - восьмым входом управляющего элемента памяти, другой вход первого элемента И соединен с единичным выходом триггера и является третьим вы ходом управляющего элемента памяти, нулевой выход триггера соединен с входом элемента задержки, выход которого является вторым выходом управ ляющего элемента памяти, первый и второй входы триггера соединены с вы ходами соответственно второго и третьего элементов И, первый, второй и третий входы второго элемента И явля ются соответственно первым, вторым и третьим входами управляющего элемента памяти, пеовый и втооой входы тое тьего элемента И являются соответственно четвертым и пятым входами управляющего элемента памяти, первый и второй входы четвертого элемен-та И являются соответственно шеетым и седьмым входами управляющего элемента памяти, выход четвертого элемента И соединен с третьим входом второго элемента И. Также последний управляющий элемент памяти содержит триггер, два элемента задержки и два элемента И, причем первый, второй и третий входы первого элемента И являются соответственно первым, вторым и тpetьим входами последнего управляющего элемента памяти, первый и второй входы второго элемента И являются соответственно четвертым и пятым входами последнего управляющего элемента па мятк, выходы элементов И соединены с взсодами триггера, нулевой выход которого соединен с входом первого элемента задержки, выход которого яв ляется вторым выходом последнего управляющего элемента памяти, единичный выход триггера является первым выходом управляющего элемента памяти, вход второго элемента задержки является шестым входом последнего уп равляющего элемента памяти, выход второго элемента задержки соединен с вторым входом элемента и. На чертеже приведена структура одноразрядного стекового запоминающего устройства. Устройство содержит шину записи информации 1, шину 2 Установка в О, информационные разрядные шины (входную)3 и выходную 4, элементы 5-8 линии задержки, входное 9 и выходное 10 слова устройства, нулевой 11 и единичный 12 выходы триггера управляющего элемента памяти (УЭП) , поступающие на i+1 слово памяти, выходные вентили 13-15 считывания информации, элементы 16-18 памяти (триг геры), входные вентили 19-21 записи информации, вентили 22-24 установки элементов памяти в О, вентили 25 и 26 управления считыванием информации, триггеры 27-29 управляющих элементов памяти, вентили 30-32 записи информации в УЭП, вентили 33-35 установки УЭП в О, вентили 36 и 37 управления записью информации, шины 38-40 управления считыванием в i, i-1 и первом словах памяти, шины 41-43 управления записью в i ,i-1 и. первое слово памяти.. Устройство работает следующим образом. Из всего массива памяти запоминающего устройства в.каждый момент времени используется только информация, расположенная на границе свободной и занятой зон. Поэтому достаточно описать работу в двух режимах: запись в стек и чтение из стека. Запись информации в стек. Допустим в l,2,...,i-2 слове устройства записана информация, т.е. в триггерах УЭП этих слов записаны единицы. Триггеры 27 и 28 находятся в нулевом состоянии. Таким образом подготовлена схема управления записью в регистр (слово) памяти 17. Кроме того, сигнал с вентиля 37 поступает на входной вентиль УЭП 31. Запись в память осуществляется через вентиль 22, на второй и третий входы которого поступают сигналы с -шины 3 и сигнал записи информации с шины 1. После того, как записано информационное слово в триггер 28 заносится единица/ которая показывает, что данное слово памяти занято информацией. При записи информации в первое слово стека сигнал на разре иение записи выставляется на шине 43 не по сигналу с выхода вентиля управления записью, как при записи в последующие слова стека, а непосредственно по сигналу с выхода триггера 29 УЭП первого слова. Чтение информации из стека. Допустим,с первого по i-1 слова стека заняты информацией, тогда все тр 1ггеры УЭП этих слов, в том числе и триггеры i8 и 29 находятся в единичном состоянии. Чтение осуществляется в два та1кта. Сначала считывается информационное слово, а затем происходит гашение информации как в информационной части стека, так и в УЭП. В рассматриваемом случае схема 26 подготовлена сигналами с триггеров 28 и 29 и по шине 39 выдается высокий разрешающий сигнал управ ления считыванием информации. Через схему 15 состояние триггера 18 перепишется на выход на шину 4. После этого поступит сигнал гашения по шине 2, по которому обнулится считанное слово через вентиль 23, и с задержкой обнулится триггер УЭП через схему 34.. При считывании информации из первого слова стека высокий разрешающий сигнал на шину 40 выдается не по сигнал с вентиля управления считыванием инфор мации, как в остальных словах стека а непосредственно по сигналу с выхода триггера УЭП 29. Надежность работы стека определяется двумя параметрами: числом передач информации по шинам в процессе чтения и надежностью элементов памяти . При использовании сдвигающего ре гистра число передач в процессе счи тывания информации зависит от числа разрядов в одном слове стека и от числа занятых слов памяти. При использовании бессдвигового устройств число передач не зависит от числа слов, хранящихся в памяти, а определяется только числом разрядов в слове. Надежность устройства, кроме того, определяется надежностью работы отдельных элементов. Отказ одного элемента в сдвигающем регистре приводит к потере информации во всем разрядном сечении. В то время, как в устройстве без сдвига информации происходит потеря только в одном разряде одного информационного слова Например, если проанализировать работу стека объемом в двадцать слоэ построенного по принципу сдвигающего регистра и по бессдвиговому принципу с точки зрения надежности, то, используя вышеизложенное, можно сказать, что надежность такого устройства, построенного по бессдвиговому принципу возрастает в двадцать раз при полностью заполненном стеке по сравнению с устройством, построенном по принципу сдвигающего регистра. Формула изобретения Одноразрядное стековое запоминающее устройство, содержащее элементы памяти, первые входы которых подключены к шине записи, вторые - к шине управления записью, третьи - к одной из информационных разрядных шин, четвертые - к шине установки в О, пятые - к шине управления считыванием, выход элемента памяти подключен к другой разрядной шине, отличающееся тем, что, с целью повышения надежности устройства, в него введены управляющие элементы памяти, первый выход каждого из которых, кроме последнего, подключен к пятому входу каждого из элементов памяти, второй выход каждого управляющего элемента памяти подключен к восьмому входу последующего управляющего элемента памяти, первые и вторые входы каждого управляющего элемента памяти подключены соответственно к шинам записи и считывания, третьи входы каждого управляющего элемента памяти подключены к шинам управления записью-, четвертые входы каждого управляющего элемента памяти подключены к шине Установка в О, пятые входы каждого управляющего элемента памяти соединены с первым выходом данного управляющего элемента памяти, шестой и седьмой BKOfstt каждого управляющего элемента памяти, кроме последнего, соединены соответственно с третьим выходом предыдущего управляющего эле.мента памяти и восьмым входом последующего управляющего элемента, шестой вход последнего управляющего элемента памяти подключен к шине записи. 2. Устройство по п.1, о т л и ч аю щ е е с я тем/ что каждый управляющий элемент памяти, кроме последнего, содержит триггер, элементы И и элемент задержки, причем выход первого элемента И является первым выходом управляющего элемента памяти, один из входоввосьмым входом управляющего элемента памяти, другой вход первого элемента И соединен с единичным .выходом триггера и явлйется третьим выходом управляющего элемента памяти, нулевой выход триггера соединен с входом элемента задержки, выход которого является вторым выходом управляющего элемента памяти, первый и второй входы триггера соединены с выходами соответственно второго и третьего элементов И, первый, второй и третий входы второго элемента И являются соответственно первым, вторым и третьим вхоцамн управляющего элемента памяти, первый и второй входы третьего элемента И являются соответственно четвертым и пятым входами управляющего элемента памяти, первый и второй входы четвертого элемента И являются соответственно шестым и седьмым входами управляющего элемента памяти, выход четвертого элемента И соединен с третьим входом второго элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с замещениемдЕфЕКТНыХ ячЕЕК | 1978 |

|

SU803009A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Устройство управления для доменной памяти | 1984 |

|

SU1265856A1 |

| Запоминающее устройство | 1975 |

|

SU714496A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Запоминающее устройство с обнаружением отказов | 1981 |

|

SU1005192A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

Авторы

Даты

1982-07-30—Публикация

1980-10-27—Подача