(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Запоминающее устройство | 1975 |

|

SU604032A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| СПОСОБ ЗАПИСИ ИНФОРМАЦИИ В ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МАГНИТНЫХ СЕРДЕЧНИКАХ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА СЕРДЕЧНИКАХ | 1992 |

|

RU2101784C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1101890A1 |

| Устройство для отображения инфор-МАции | 1979 |

|

SU830370A1 |

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ).

Известно ЗУ, содержащее адресные ключи, выход каждого из которых подключен к общему формирователю или накопителю, а вход - к соответствующему выходу дешифратора, а также элемент задержки, вход которого соединен с щиной «Обращение, а выход - к входу общего формирователя. В таком ЗУ адресные ключи предназначены для коммутации тока общего формирователя в выбранный адрес накопителя. Адресный ключ представляет собой транзистор, работающий а ключевом режиме, который под действием сигнала с дещифратора переходит из режима отсечки в режим насыщения. Важной особенностью такого ЗУ является то, что из группы адресных ключей по координате X (или Y) при каждом обращении к ЗУ срабатывает только один ключ, выбранный дешифратором. Такая особенность позволяет миниатюризировать адресные ключи, выполнив всю такую группу или часть ее в одном корпусе микросхемы, расчитанном на мощность рассеивания одного ключа 1.

Недостатком этого ЗУ является то. что при использовании в нем магнитного накопителя мощность сигнала со стандартного 5 логического элемента дешифратора недостаточна для введения транзистора адресного ключа в режим насыщения.

Наиболее близким к предлагаемому по Q технической сущности и достигаемому эффекту является ЗУ, содержащее адресные формирователи, выходной каскад каждого из которых подключен к общему формирователю или магнитному накопителю, а первый выход предварительного каскада - 15 к соответствующему выходу дешифратора, а также элемент задержки, вход которого соединен с шиной «обращение, а выход - к входу общего формирователя, а также шину «Питание. В таком ЗУ мои ность 2Q сигнала выбранного адреса на один-два порядка больще мощности сигнала со стандартного логического элемента, поэтому адресный ключ выполняется в виде двухкаскадного формирователя, первый каскад

которого является усилителем мощности, а второй - ключом 2.

В адресной цепи такого ЗУ большая часть мощности рассеивается предварительными каскадами адресных формирователей, причем она практически не зависит от того выбран адресный формирователь или нет. Объясняется это тем, что в монокристальных интегральных схемах предварительный каскад (усилитель мощности) подключение его к выходному каскаду выполняется с непосредственными связями без реактивных элементов и трансформаторов. Это приводит к необходимости размещать, как правило, каждый адресный формирователь в отдельном корпусе и является недостатком такого ЗУ, так как усложняет устройство и снижает надежность, увеличивая количество микросхем, паек и габариты устройства.

Цель изобретения - упрощение устройства и повыщение его надежности.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее две группы адресных формирователей, одни выхбды выходного каскада каждого из адресных формирователей первой группы подключены к выходу формирователя тока, другие - к одним соответствующим входам накопителя, выходы адресных формирователей второй группы подключены к другим соответствующим входам накопителя, первые входы предварительного каскада адресных формирователей первой и второй групп подключены к соответствующим выходам дещифратора, элемент задержки, вход которого подключен к щине «Обращение, а выход - к входу формирователя тока, и щину питания, введены формирователь напряжения, элемент ИЛИ, ключи и ограничитель амплитуды, вход которого подключен к выходу формирователя тока, а выход - к первому входу формирователя напряжения, второй вход которого соединён с щиной «Обращение, а третий - с щиной «Питание выход формирователя напряжения соединен с первыми входами ключей, выходы каждого из -которых подключены к второму входу предварительного каскада адресных формирователей первой и второй групп, а вторые входы ключей через соответствующий элемент ИЛИ подключены к соответствующим вторым входам предварительных каскадов адресных формирователей первой и второй групп.

Сущность изобретения - упрощение устройства и повыщение надежности - состоит в уменьщении времени питания адресных формирователей путем запитки их предварительных каскадов через ключи от формирователя напряжения, причем ключи определяют адрес подачи питания за счет управления через элементы ИЛИ -

от первых входов предварительных каскадов, а формирователь напряжения задает амплитуду и длительность этого питания с помощью ограничителя напряжения, преобразующего управляющий сигнал (перепад напряжения от адресного тока) до стандартного уровня.

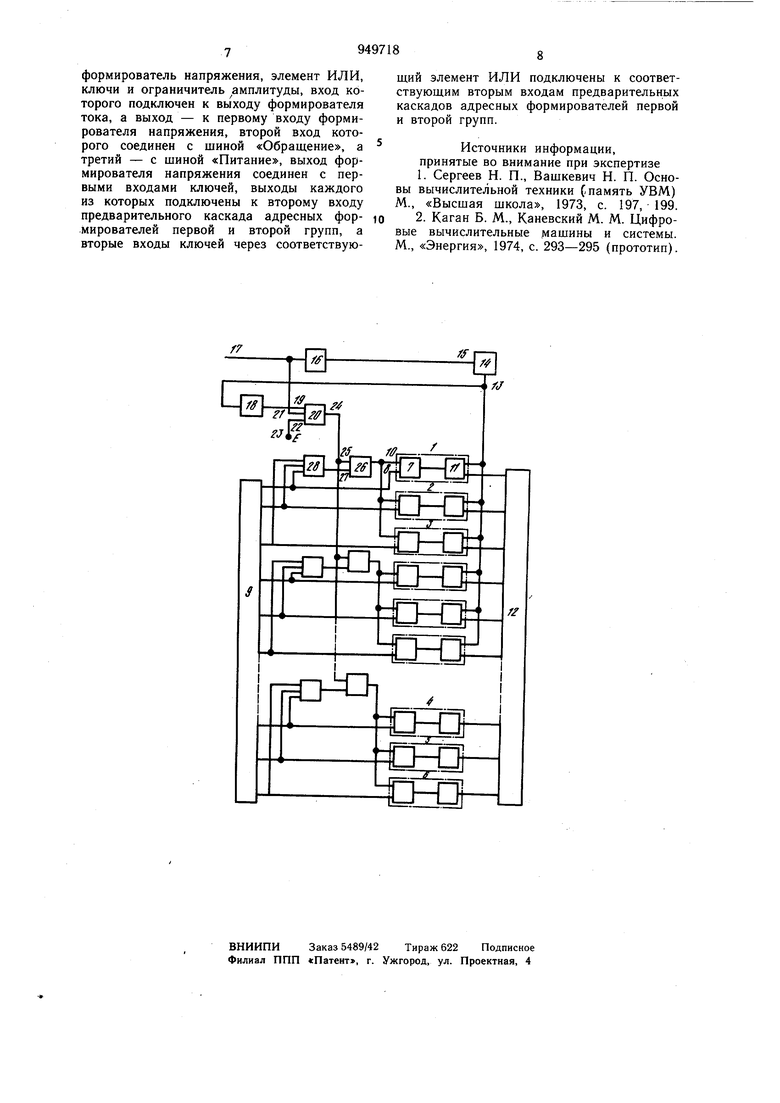

На чертеже представлена схема предлагаемого устройства.

Устройство содержит первую группу 1-3 адресных формирователей по координате X и вторую группу 4-6 по координате Y, состоящие из предварительного каскада 7 с первым входом 8, подключенным к соответствующему выходу дещифратора 9, вторым входом 10 и выходным каскадом 11,

подключенным к накопителю 12 (по координате выборки Y) или к выходу 13 формирователя 14 тока (по координате выборки X), вход 15 последнего соединен с выходом элемента задержки 16, вход которого соединен с щиной 17 «Обращение. Оно содержит также ограничитель 18 амплитуды, выход которого подключен к первому входу 19 формирователя 20 напряжения, имеющего второй вход 21 и у которого третий вход 22 соединен с щиной 23 «Питание, а выход

5 24 - с первым входом 25 ключей 26, второй вход 27 каждого из которых соединен с выходом элемента 28 ИЛИ, входы которого соединены с соответствующим первыми входами 8 предварительных каскадов 7. Вход, ограничителя 18 амплитуды

соединен с выходом 13 формирователя 14 тока, второй вход 21 формирователя 20 напряжения соединен с щиной 17 «Обращение, а выход ключей 26 соединен с вторым входом 10 предварительного каскада 7

j соответствующих адресных формирователей 1-6. Необходимо отметить, что ключи 26 лищь функционально выделены в отдельный элемент. Так как рассеиваемая ими мощность незначительна, то при реализации ЗУ целесообразно размещать их в

0 корпусе микросхемы адресных формирователей.

Устройство работает следующим образом.

С выхода дещифратора 9 разрешающий

5 потенциал подается, например, на вход 8 предварительного каскада 7 адресного формирователя 1 и через элемент 28 ИЛИ на второй вход 27 ключа 26. При поступлении сигнала на щину 17 «Обращение срабатывает формирователь 20 напряжения, который из напряжения Е на шине 23 Питание формирует напряжение И, равное номинальному напряжению питания предварительного каскада 7 адресного формирователя 1 плюс падение напряжения на ключе 26. Напряжение И через выбранный ключ 26 поступает на второй вход 10 предварительного каскада 7 адресных формирователей первой группы 1-3, что приводит, поскольку разрешающий потенциал подается только на вход 8 предварительного каскада 7 адресного формирователя 1, к срабатыванию выходного каскада 11 этого формирователя. Сигнал на шине 17 «Обращение, пройдя через элемент задержки 16, поступает на вход 15 формирователя 14 тока, который посылает через открытый выходной каскад 11 адресного формирователя 1 в накопитель 12 импульс адресного тока с определенным фронтом, длительностью и амплитудой. Одновременно ограничитель 18 амплитуды формирует из перепада напряжения адресного тока на выходе 13формирователя 14 импульс напряжения с уровнем стандартных логических элементов, который поступает на первый вход 19 формирователя 20 напряжения. В схеме формирователя 20 напряжения первый вход 19 и второй вход 21 представляют входы элемента ИЛИ. Поэтому выключение формирователя 20 напряжения, а значит и отключение питания от предварительных каскадов, произойдет в определенный момент - момент запирания формирователя 14тока. Наступление этого момента может меняться, во-первых, в зависимости от режима считывания или записи, а во-вторых, из-за разброса задержки выключения общего формирователя по отношению к времени выключения входного сигнала, которая зависит от схемы построения формирователя 14 тока, нестабильности параметров его элементов, времени рассасывания и температуры окружающей среды. Выключение формирователя напряжения с помощью управляющего сигнала (перепада напряжения адресного тока) позволяет исключить возможность выключения питания предварительных каскадов раньше выключения адресного тока, протекающего через выходной каскад адресного формирователя. Это позволяет обеспечить нормальную работу ЗУ, т. е. надежную запись без потери быстродействия и исключить возникновение на выходном каскаде адресных формирователей выбросов напряжения, превышающих пределы допустимых. Таким образом, в предлагаемом ЗУ запитка предварительных каскадов осуществляется через ключи от формирователей напряжения, причем ключи с помощью элементов ИЛИ определяют адрес подачи питания, а формирователь напряжения с помощью ограничителя амплитуды задает необходимую длительность и амплитуду. Одновременно с подачей напряжения на адресный формирователь первой группы 1 будет запитан предварительный каскад 7 адресных формирователей второй группы 2 и 3, т. е. в нашем примере рассеивание мощности будет производится также предварительными каскадами 7 адресных фор мирователей первой группы 2 и 3. Аналогично протекают процессы в формирователях второй группы 4, 5 и 6 по координате Y, а также при последующих обращениях к ЗУ, и, таким образом, выделение мощности в нашем примере, происходит только в трех, по каждой координате, адресных формирователях во время посылки общим формирователем импульса тока в магнитный накопитель. Количество адресных формирователей выбирается из оптимального, с точки зрения конструктивного исполнения, для данного ЗУ, соотношение между количество. ключей 26, элементов 28 ИЛИ, мощностью рассеивания предварительных каскадов 7 и допустимой мощностью рассеивания одним корпусом микросхемы. В предлагаемом ЗУ возможно уменьшение в 10-20 раз количество корпусов микросхем адресных формирователей и количество паек, а также соответствующее уменьшение рассеиваемой мощности, габаритов и повышение надежности. Предварительные каскады адресных формирователей находятся в рабочем состоянии лишь часть рабочего времени устройства, это дополнительно повышает надежность адресных формирователей и устройства в целом. Необходимо отметить, что в формирователе 20 напряжения можно использовать маломощную схему стабилизатора, например эмиттерный повторитель, запитанный от напряжения, выделенного на стабилитроне. Это позволит снизить требования к стабильности источника питания Е или расширить зону устойчивой работы ЗУ. Если запитывать формирователь 20 напряжения от источника, которым запитан формирователь 14 тока, то это приведет еще к одному приемуществу - уменьшению количества номиналов источников питания ЗУ. Формула изобретения Запоминающее устройство, содержащее две группы адресных формирователей, одни ВЫХОДЫвыходного каскада каждого из адресных формирователей, первой группы подключены к выходу формирователя тока, другие - к одним соответствующим входам накопителя, выходы адресных формирователей второй группы подключены к другим соответствующим входам накопителя, первые входы предварительного каскада адресных формирователей первой и второй групп подключены к соответствующим выходам дешифратора, элемент задержки, вход которого подключен к шине «Обращение, а выход - к входу формирователя тока, и шину питания, отличающееся тем, что, с целью упрощения устройства и повышения его надежности, оно содержит

формирователь напряжения, элемент ИЛИ, ключи и ограничитель амплитуды, вход которого подключен к выходу формирователя тока, а выход - к первому входу формирователя напряжения, второй вход которого соединен с шиной «Обращение, а третий - с шиной «Питание, выход формирователя напряжения соединен с первыми входами ключей, выходы каждого из которых подключены к второму входу предварительного каскада адресных фор.мирователей первой и второй групп, а вторые входы ключей через соответствуюший элемент ИЛИ подключены к соответствующим вторым входам предварительных каскадов адресных формирователей первой и второй групп.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-08-07—Публикация

1979-07-06—Подача