(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство | 1979 |

|

SU809367A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1305775A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU934554A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU942140A1 |

1

Изобретение относится к области вычисмительнон техники и может быть применено для 11острое1-И1Я oiie)tiri :;Hbix и буферных запоминающих устройств (ЗУ) цифровых вычисли- . тельных маипп) и счетно-ре1иаю1дих приборов.

Извест11Ь е запоминающие устройства со схемами обс.чуживания характеризуются потреблением больтиой МОИ1НОСТИ и содержат многокомпонентные и сложные узлы. Примером может служить известное ЗУ на активных элементах,, в котором использован усилитель считывания из нескольких каскадов, согласующих уровни входного и выходного сигналов, а также ЗУ. усилитель считывания которого cocTOirr из входного, вьЕходного и согласуютт1его тртпчхфного каскадов. При этом входной каскад для обеспечения неразрушаюшего. считывания выпо.чнен по дифференциальной схеме с обшей базой с малым входным сонротивлением.

Наиболее близким техническим решением к нредложенному является ЗУ, содержа1пее де(иифратор адреса и матрицу заноминающ|1Х элементов на полупроводниковых T)iirrepax. адресные входы которых сое.:1инены с адресны.ми илинами, подключенными через разде.И тельные элементы к нише и1гг;:П1ия, а разрядные входы -- с выхода.ми блоков записи и с входами блоков считывания.

Блок считывания в таком ЗУ обеспечивает не.разрушающее считывание и содержит элементы, формирующне опорный потенциал на пнформацион 1ых шинах, причем сигнал на вь1ходе его входного каскада онределяется ур(из5нем опорного потен1и1ала и для его согласовання с выходным каскадом требуется согласующ41Й каскад.

Это усложняет устройство i; увеличивает потребляемую мощность.

К увеличению потребляемой устройством мощности приводит также отсчтствие в нем э.лементов и связей, которые б.1окпрова. бы включение блока записи ири отс тств1П ciuналов на адресш х входах. При уве.

объема ЗУ все входы записи одноименных пазрядов объед4шяются и отсутствие блокнро1жи приводит к . что при ноступлении сигналов заннси включаются блоки записи все.х моду.чей ЗУ, а не To.ibKo того, к которому нанрав.1ено обран1ение.

Целью изобретеиия является снижение потреб.чяемой МОПлНОСТИ.

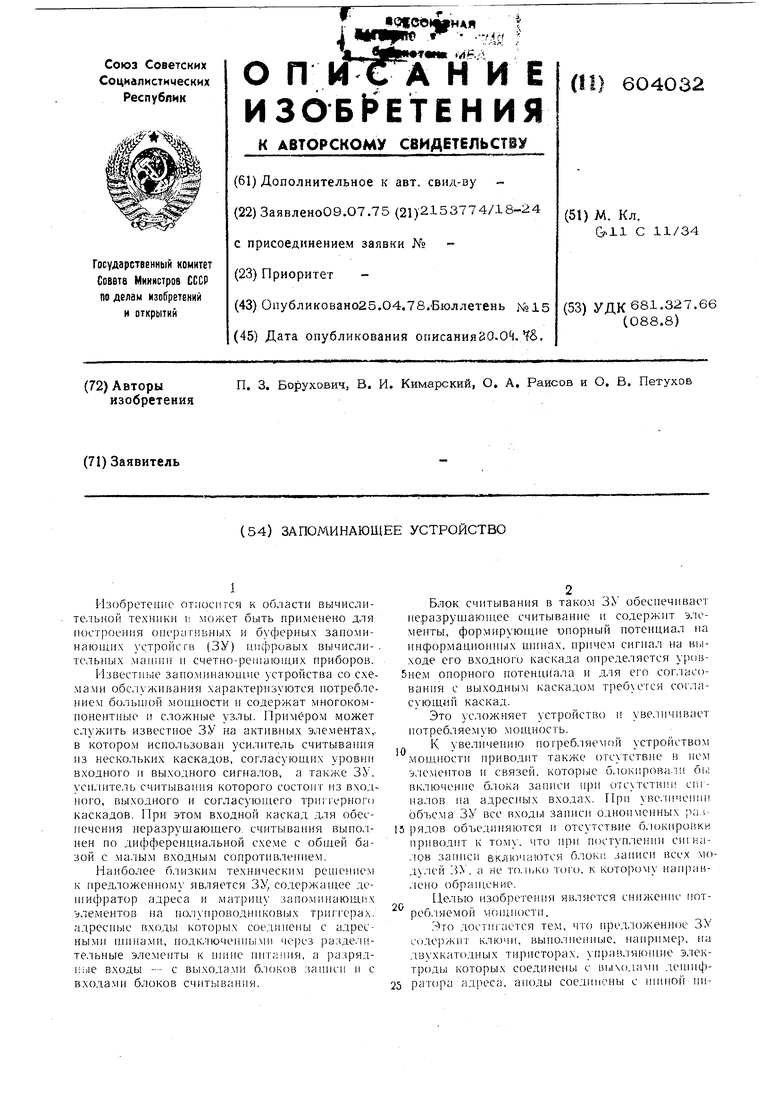

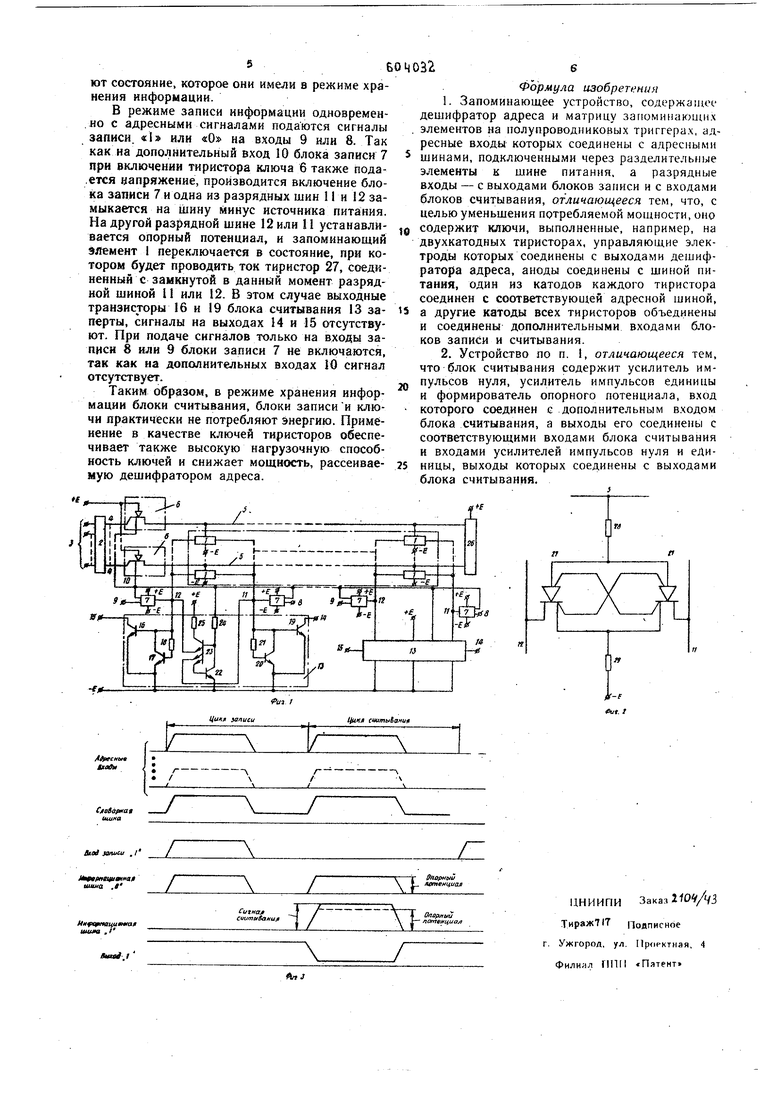

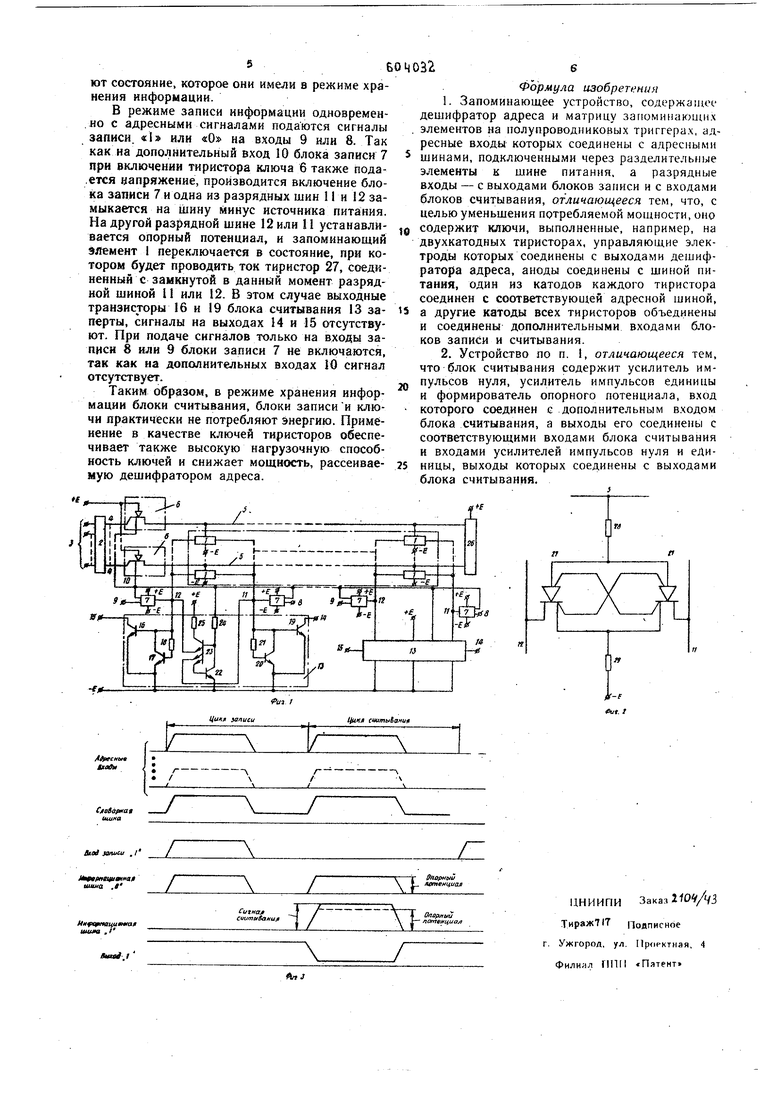

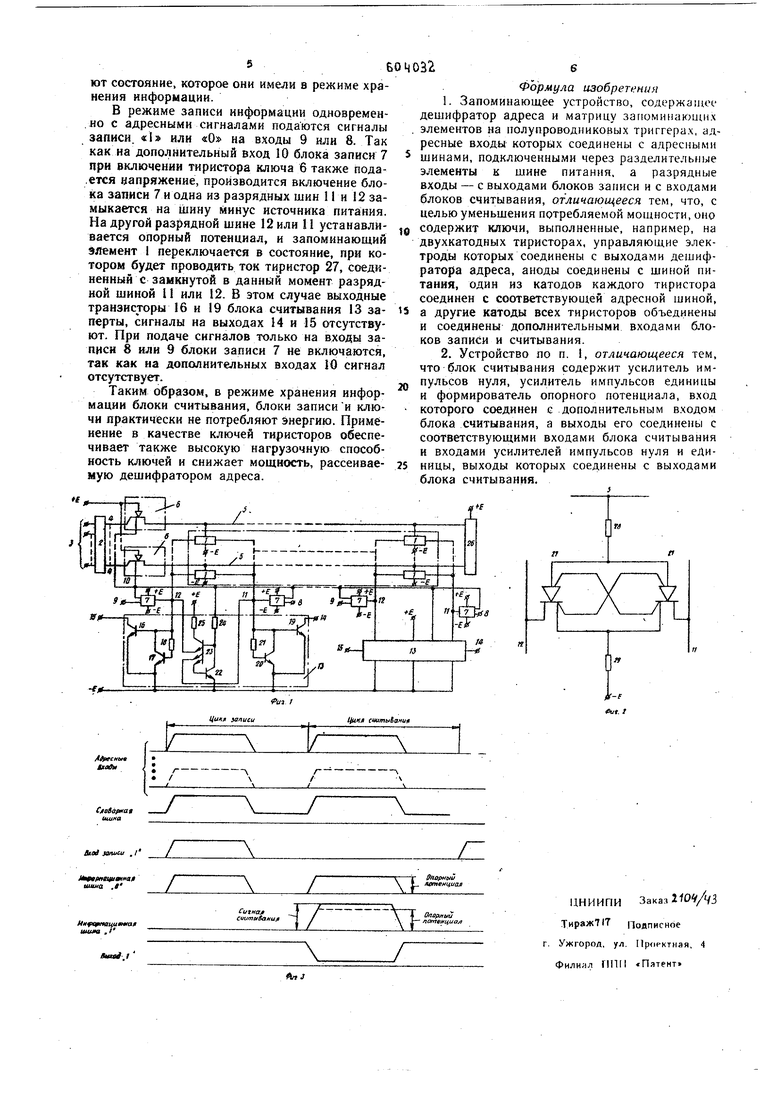

Это доспнается тем, что предложенное ЗУ содержит ключи, выполненные, напрпмер, на двухкатодных тиристорах, правляю1ние электроды которых соединены с деи1ифратора адреса, аиоды соединены с Н1пной ни3&ОЧтания, один из катодов каждого тиристора соединен с соответствующей адресной шиной, а другие катоды всех тиристоров объединены и соединены с дополнительными входами блоков записи и считывания. Блок считывания --может содержать усилитель импульсов нуля, усилитель импульсов единицы и формирователь опорного потенциала, вход которого соединен с дополнительным входом блока считывания, а выходы его соединены с соответствующими входами блока считывания и входами усилителей импульсов нуля и единицы, выходы которых соединены с выходами блока считывания.. На фиг. 1 представлена принципиальная схема предложенного ЗУ; на фиг. 2 - схема запоминающего элемента, на фиг. 3 - временная диаграмма работы устройства. Предложенное ЗУ содержит объединенные в матрицу запоминающие элементы 1, дещифратор адреса 2 со входными 3 и выходными 4 шинами, адресные щины 5, к.чючи 6, выполненные на двухкатодных тиристорах, блоки записи 7 со входами записи «О и «I соответственно 8 и 9, дополнительиым входом 10. Выходы блоков записи 7 подсоединены к разрядным входам «О и « соответственно по щинам.11 и 12. Входы блоков считывания 13 соеДинены с шинами П и 12, а вь1ходы - с выходными щинами «О и «1 соответственно 14 и 15. Блок счн тывания 13 содержит усилители импульсов нуля и единицы и формирователь опорного, потен циала. Усилители импульсов содержат выход.иой транзистор 16, шунтирующий транзистор 17 и резистор 18, выходной транзистор 19, шунтирующий транзистор 20 и резистор 21 . Формирователь опорного потенциала состоит из управляющего транзистора 22 усилительного трехэмиггериого транзистора 23, базового резистора 24 и коллекторного резистора 25 Выходы формирователя опорного потенциала соединены с разрядными шинами 11 и 12 и со входами усилителей импульсов нуля и единицы блока считывания 13. Входы формирователя опорного потенциала соединены с объединенными катодами тиристоров ключей бис дополнительными входами 10 блоков записи 7. Другие катоды тиристоров ключей б соединены с соответствующими адресными шинами 5, которые через разделительные элементы 26 соединены с источником питания. Запоминающий элемент i представляет собой полупроводниковый симметричный триггер, состоящий из двухкатодных тиристоров 27 и резисторов 28 и 29. Аноды тиристоров 27 через резистор 28 соединены с адресной шиной 5, первые катоды через резистор 29 соединены с шиной питания, а вторые катоды тиристоров 27 соединены с соответствующими разрядными шинами 11 и 12. N и Р базы тиристоров 27 соединены перекрестными связями. В ЗУ могут применяться и другие известные запоминающие элементы, например триггеры, выполненные на двухэмиттерных транзисторах. ЗУ работает следующим образом. В режиме хранения информации запоминаюш,ие элементы 1 запитываются через разделительные элементы 26. Ток, текущий через запоминающие элементы 1, имеет значительно меньшую величину, чем ток в режиме обращения. Все двухкатодные тиристоры ключей 6 выключены, напряжение на входы формирователей опорного потенциала и додолнительные входы 10 блоков записи 7 не подается, и на разрядных шинах II и 12 напряжение близко к нулю. Выходные транзисторы 16 и 19 усилителей импульсов нуля и единицы блока считывания 13 Заперты. В режиме считывания на входы 3 дешифратора 2 подаются сигналы и на одном из выходов 4 дешифратора 2 появляется высокий потенциал, который включает тиристор ключа 6. При включений тиристора на входы блоков считывания 13 подается напряжение и на разрядных шинах 11 и 12 устанавливается опорное напряжение, величина которого автоматически поддерживается такой, что выходной ток блока считывания 13, текущий через коллекторы выходных транзисторов 16 и 19 не превышает следующего значения - I rjSTi, где 11 - ток через базовый резистор 24 формирователя опорного потенциала; К - коэффициент передачи усилителя им-. пульсов блока считывания 13; ;8 - коэффициент.усиления по току управляющего транзистора 22. Ток 11 выбирают приблизительно на порядок меньше рабочего выходного тока блока считывания 13, коэффициент передачи К также приблизительно на порядок меньше jS. Поэтому ток lltix на два порядка меньше рабочего выходного тока блока считывания 13 и, следовательно, при подаче опорного потенциала на разрядные шины II, 12 выходной сигнал считывания «е возникает. Вместе с тем величина опОрносо потенциала лишь незначительно меньше ( из 50-100 мВ) напряжения на разрядных шннах И, 12 прн подаче сигнала считывания, поэтому разрушения информации при считывании не происходнт. Одновременно с установлением опорного потенциала при включении тиристора ключа 6 повышается напряжение на адресной шине 5, связанной с этим тиристором, и увеличивается ток через запоминающие элементы I, подсоединенные к адресной шине 5. При увеличении тока возрастает напряжение на катодах одного из тиристоров 27, входящего в состав запоминающего элемента I, и часть тока запоминающего элемента 1 переключается в соответствующую разрядную шину 11 или 12, производя включение усилителя импульсов блока считывания 13. По окончании режима считывания сигналы с адресных входов 3 снимаются, потенциал на выходе 4 дешифратора 2 становится ниже потенциала на катодах включенного тиристора ключа 6/ что приводит к его выключению. Все элементы ЗУ восстанавливают состояние, которое они имели в режиме хранения информации. В режиме записи информации одновремен. но с адресными сигналами подаются сигналы записи. «I или «О на входы 9 или 8. Так как на дополнительный вход 10 блока записи 7 при включении тиристора ключа 6 также пода.ется напряжение, производится включение блока записи 7 и одна из разрядных шин Пи 12 замыкается на шину минус источника питания. На другой разрядной шине 12 или 11 устанавливается опорный потенциал, и запоминающий элемент 1 переключается в состояние, при котором будет проводить ток тиристор 27, соединенный с замкиутой в данный момент разрядной шиной 11 или 12. В этом случае выходные траиэисторы 16 и 19 блока считывания 13 заперты, сигналы иа выходах 14 и 15 отсутствуют. При подаче сигналов только на входы записи 8 или 9 блрки записи 7 не включаются, так как на дополнительных входах 10 сигнал отсутствует. Таким образом, в режиме хранения информации блоки считывания, блоки записи и ключи практически не потребляют энергию. Применение в качестве ключей тиристоров обеспечивает также высокую нагрузочную способность ключей и снижает мощность, рассеиваемую дешифратором адреса. 6 326 Формула изобрет ния 1. Запоминающее устройство, содержаиичдешифратор адреса и матрицу запоминающих элементов на полупроводниковых триггерах, адресные входы которых соединены с адресными шинами, подключенными через разделительные элементы к шине питания, а разрядные входы - с выходами блоков записи и с входами блоков считывания, отличающееся тем, что, с целью уменьшения потребляемой мощности, оно содержит ключи, выполненные, например, на двухкатодных тиристорах, управляющие электроды которых соединены с выходами дешифратора адреса, аноды соединены с шиной питаиия, один из катодов каждого тиристора соединен с соответствующей адресной шиной. а другие катоды всех тиристоров объединены и соединены дополнительными входами блоИ соединены дополнительными ков записи и считывания. 2. Устройство по п. 1, отличающееся тем, что блок считывания содержит усилитель импульсов нуля, усилитель импульсов единицы и формирователь опорного потенциала, вход которого соединен с дополнительным входом блока считывания, а выходы его соединены с соответствующими входами блока считывания и входами усилителей импульсов нуля и единицы, выходы которых соединены с выходами блока считывания.

tfa. /

Г

Авторы

Даты

1978-04-25—Публикация

1975-07-09—Подача