Изобретение относится к электронной и вычисл-ительной технике и предназначено для использования, в частности, в интегральных полугюстоянных ЗУ.

Целью изобретения является уменьшение п&требляемой мощности, повышение быстродействия.

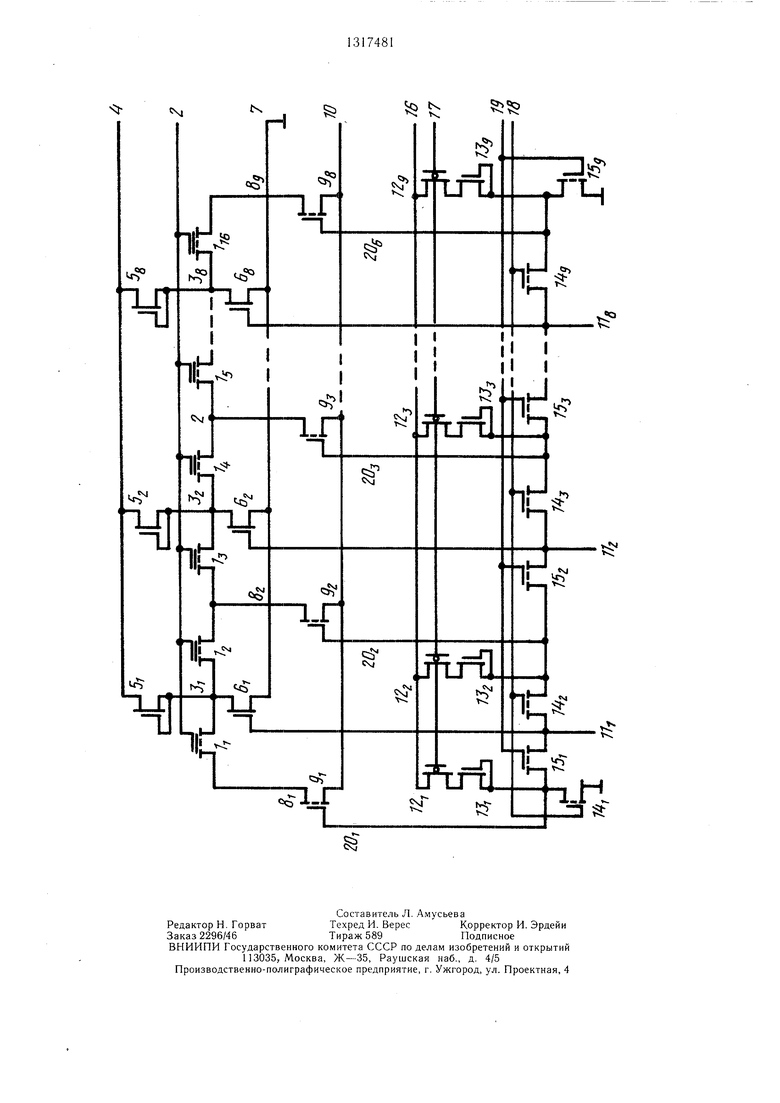

На чертеже представлена электрическая схема устройства (она включает массив накопителя и дешифрирующие схемы).

Устройство содержит накопитель, выполненный на 16 запоминающих МДП-тран- зисторах 1( -IK, с плавающим затвором, управляющие затворы которых соединены с щиной строки 2, восемь разрядных шин 3( -Зз (первой группы), подключенных к шине питания 4 через нагрузочные элементы на транзисторах 5 -Sg с встроенным каналом и через ключевые элементы на транзисторах 6,-6g к шине 7 нулевого потенциала, девять разрядных шин 8,-89 (второй группы), подключенных через элементы выборки на транзисторах 9 -9 к информационной шине 10, шины HI-П управляющих сигналов, формирователи управляющих сигналов содержат элементы блокировки на транзисторах 12, -12, зарядные транзисторы 13i-13g с встроенным каналом, первые коммутирующие транзисторы , вторые коммутирующие транзисторы , шину питания 16, шину управляющего сигнала 17, адресные шины 18 и 19, выходы формирователей управляющих сигналов.

Устройство работает в двух режимах: активном и пассивном, т. е. режиме с пониженным потребление.м мощности. В активном режиме устройство работает в режимах «Программирование и «Считывание.

Рассмотрим работу устройства в режиме «Программирование. Для реализации режима программирования, т. е. перевода запоминающего транзистора в состояние высокого уровня порогового напряжения (Vp 8 В), на информационной шине 10, на щине питания 16 и на шине управляющего сигнала 11 обеспечивается высоковольтный сигнал, равный 20 В. На щину выбранной строки 2 подается высоковольтный сигнал, равный 20 В. Если необходимо запрограммировать запоминающий транзистор U , то выборка разрядной шины За осуществляется сигналом выборки, поступающим по шине 1 1 и равным 5 В, а выборка разрядной шины 8j - высоковольтным сигналом, равным 20 В и поступающим с выхода 20j формирователя управляющих сигналов, при этом на затвор первого коммутирующего транзистора 14, подается сигнал выбора, равный 5 В, а на затвор второго ко.ммутирующего транзистора ISj - нулевой потенциал. При этом открывается транзистор 6j, обеспечивающий на истоках транзисторов 1 и 1 нулевой потенциал, и транзистор 9j, через который на сток выбранного транзистора U подается потенциал, равный 18 В. В зависимости от того, программируется запоминающий элемент или сохраняется в прежнем состоянии, на щине данных обеспечивается высоковольтный сигнал, равный 20 В, или нулевой потенциал.

При этом исключается ложное программирование транзистора 3, так как на сток этого транзистора не поступает высоковольтный сигнал, равный 18 В, благодаря тому, что транзистор 9г закрыт.

Не программируется также и запоминающий транзистор 5, так как на истоке этого транзистора (щина 3g) сохраняется напряжение, близкое к напряжению питания, благодаря тому, что транзистор 6д закрыт. В режиме «Считывания на щину 16 подается напряжение 5 В, на шину 17 - нулевой потенциал, запирающий транзисторы 76-85. Выборка шины 3,-3 осуществляется так же, как и в случае программирования. Сигнал, формируемый на выходе 20е формирователя управляющих сигналов,

имеет потенциал, равный (Vcc -VTUH ) «4,0 В, так как выход формирователя подключается через открытый коммутирующий транзистор к выбранной разрядной шине 11 - 1 Ig , потенциал которой равен 5,0 В. В режиме считывания шины данного массива через соответствующую информационную шину подключены к соответствующему усилителю считывания, который обеспечивает напряжение считывания на этой щине. Так как транзистор Ц находится в состоянии высокого уровня порогового напряжения (Vnop 8 В), то напряжение считывания, равное 4, 5 В подаваемое на шину 2, недостаточно для отпирания этого транзисто ра и щина 8j заряжается до напряжения 1,4 В, которое усилитель считывания вос

принимает как напряжение высокого уровня.

Если транзистор 1 находится в состоянии низкого уровня порогового напряжения (лор -2 В), то шина 10 через откры- тый транзистор 9з и разрядная шина 8з разряжаются через открытые транзистор 1„ и транзистор ба.

Перепад напряжения до 20 мВ (от 1,4 до 1,38 В) на входе усилителя считывания

является достаточным для считывания усилителем напряжения низкого уровня.

При этом исключается ложное считывание транзистора Ij, так как сигнал, формируемый на выходе 20j формирователя управляющих сигналов и имеющий нулевой потенциал, запирает транзистор 9 и исключает подключение транзистора Ij к усилителю считывания через информационную шину.

Не считывается также информация и с транзистора Ij, так как исток этого транзистора (разрядная шина 3g) не подключается к шине 7 благодаря закрытому транзистору баТаким образом, при таком соединении запоминающих транзисторов исключается паразитное программирование и ложное считывание.

В пассивном режиме на шину высоковольтного питания 16 подается потенциал, равный 5 В, на шину управляющего сигнала 17 - нулевой потенциал, запирающий транзисторы блокировки мощности 12i - 12j, на шины строк 2 накопителя подается нулевой потенциал с дешифратора строк.

Сигналы выбора , поступающие с дешифратора столбцов и имеющие нулевой потенциал, закрывают транзисторы переключения 6,-6j. На щину младшего адреса 18 и инверсного младшего адреса 19 поступает сигнал, равный нулевому потенциалу, который закрывает эти транзисторы. Таким образом, на всех выходах 20, -20в формируются сигналы, имеющие нулевой потенциал, который запирает транзисторы выбора 9i-9g. При таком включении запоминающие транзисторы не меняют своего состояния сколь угодно долго. В результате в пассивном режиме в данном устройстве полностью исключаются сквозные токи, что приводит к тому, что схема накопителя, организованная таким образом, практически не потребляет мощности.

Преимущества предлагаемого устройства перед известными состоят в уменьшении потребляемой мощности при использовании в ЗУ большой информационной емкости за счет значительного уменьшения количества формирователей, за счет введения элементов блокировки, которые полностью исключают сквозные протекающие токи в цепях формирователей в активном режиме при считывании и в режиме с пониженным потреблением мощности; в повышении быстродействия при использовании в ЗУ большой информационной емкости за счет объединения запоминающих транзисторов каждого разряда в отдельные массивы накопителя, подключаемые к информационной шине, вследствие чего уменьшается емкостная нагрузка на соответствующих входах

усилителей считывания информации, что в конечном итоге повышает быстродействие ЗУ.

Формула изобретения

Запоминающее устройство, содержащее накопитель, нагрузочные и ключевые элементы, выполненные на транзисторах, причем исток и затвор транзистора каждого нагрузочного элемента подключены

к соответствующей разрядной шине первой группы накопителя, а сток подключен к шине питания, сток транзистора каждого ключевого элемента подключен к соответст- вуюшей разрядной шине первой группы, а исток - к шике нулевого потенциала,

формирователи управляющих сигналов, каждый из которых состоит из зарядного транзистора, первого и второго коммутирующих транзисторов, затвор и исток зарядного транзистора соединены со стоком

первого коммутирующего транзистора, элементы выборки, выполненные на транзисторах, исток каждого из которых подключен к информационной шине, а сток - к соответствующей разрядной шине второй группы, а затвор - к истоку зарядного

транзистора, отличающееся тем, что, с целью

снижения потребляемой мошности и повышения быстродействия устройства, в нем каждый формирователь управляющих сигналов содержит элемент блокировки; выполQ ненный на транзисторе, сток которого подключен к шине питания, затвор - к шине управляющего сигнала, а исток - к стоку зарядного транзистора, исток первого коммутирующего транзистора первого формирователя управляющих сигналов подключен

5 к шине нулевого потенциала, исток первого коммутирующего транзистора каждого формирователя управляющих сигналов, кроме первого, соединен с истоком второго коммутирующего транзистора предыдущего формирователя управляющих сигналов и с затвором транзистора соответствующего ключевого элемента, причем исток второго коммутирующего транзистора последнего формирователя управляющих сигналов подключен к шине нулевого потенциала, а зат5 воры первого и второго коммутирующих транзисторов каждого формирователя управляющих сигналов подключены к соответствующим адресным щинам.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Формирователь импульсов записи | 1986 |

|

SU1381594A2 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| Формирователь записи-считывания для запоминающих устройств | 1978 |

|

SU765873A1 |

| Матричный накопитель | 1981 |

|

SU1015440A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1978 |

|

SU769628A1 |

Изобретение относитсй к электронной и вычислительной технике и предназначено для использования, в чacтнoctи, в интегральных полупостоянных ЗУ. Целью изобретения является уменьшение потребляемой мощности, повышение быстродействия. Поставленная цель достигается тем, что в формирователи управляющих сигналов введены элементы блокировки на транзисторах с соответствующими связями, что полностью исключает сквозные протекающие токи в цепях формирователей в активном режиме при считывании и в режиме с пониженным потреблением мощности и повышает быстродействие при использовании в ЗУ больщой информационной емкости за счет объеди- яения запоминающих транзисторов каждого в отдельные массивы накопителя, подключаемые к информационной шине. 1 ил. оо 4 00

| Патент США № 3988604, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Горный компас | 0 |

|

SU81A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1987-06-15—Публикация

1985-03-22—Подача