(54) УСТЮЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Генератор случайных чисел | 1990 |

|

SU1807482A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Система для контроля и управления | 1985 |

|

SU1273932A1 |

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для интерпретации выражений языков программирования | 1982 |

|

SU1078432A1 |

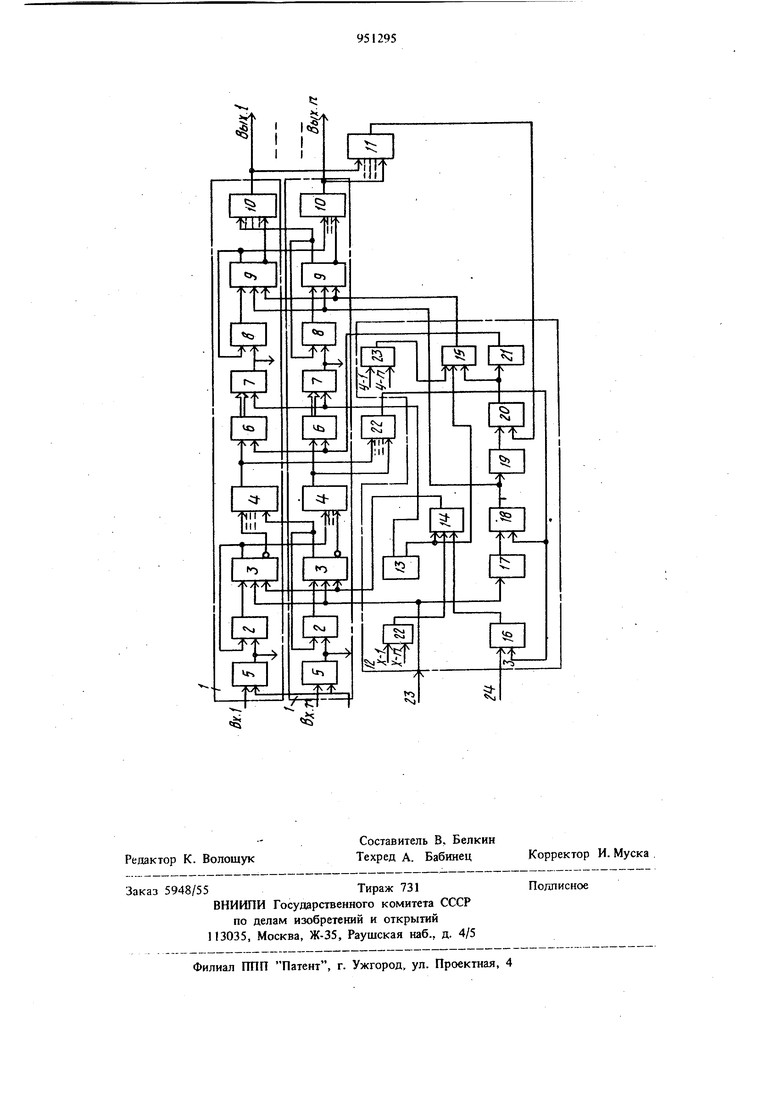

Изобретение относится к автоматике и вычислительной технике н может быть использовано также в областях техники средств связи в радиолокации с цифровой обработкой сигналов. Известно устройство для сравнения чисел, содержащее регистры элемента И, ИЛИ, НЕ 1. Недостатком этого устройства является низ кое быстродействие., Наиболее близким к предложенному техническому решению является устройство, содержащее элементы И, ИЛИ, регистрыС 2J. Это устройство позволяет выделить максимальное или минимальное число, но не позволяет определять номера канала, по которому это число прошло. Кроме того, во многих случаях при наличии помех необходимо иметь повышенную достоверность определения каналов с максимальнь1М числом. Цель изобретения - повышение достоверности определения экстремального числа. Цель достигается тем, что в устройстве для . срапнечия чисел, содержащем п узлов анализа. коммутатор, элементы ИЛИ,-причем выход результата каждого i-ro узла анализа соединен с 7-ым входом первого злемента ИЛИ, где , 2. . . п, выход которого подключен к входу блокировки коммутатора, входная шина каждого i-ro числа соединена с информационным входом i-ro узла анализ, вход начальной установки устройства соединен с первым управляющим входом KOMMyraTqpa и с. первым управляющим входом каждого узла анализа, выход предварительного разделения кгшсдого i-ro узла анализа подключен к i-ому входу второго элемента ИЛИ, выход которого соединен с вторым управляющим входом коммутатора, вход задания режима устройства подключен к второму управляющему входу каждого узла анализа, первый, второй и третий выходы синхронизации коммутатора подключены к первому, второму и третьему входам синхронизации соответственно каждого узла анализа, выходы поразрядного анализа первого и второго уровней каждого i-ro узла анализа соединены с i-ими информационными входами первой н второй групп соответственно коммутатора, выход переноса первого уровня каждого i-ro узла анализа подключен к i-ому входу переносов первой группы входов 1, 2. . ., vii-1, i+1,. . . n-rp узлов анализа, выход переноса второго уровня каждого i-ro узла анализа соединен с i-ым входом переносов второй группы входов 1,2 ..., i-1, i+1, . , . n-го узлов анализа, первый и второй выходы управления коммутатора подключены к третьему и четвертому управляющшу входам узлов анализа. Кроме того, в нем каждый узел анализа состоит из сумматора по mod 2;Деишфраторов счетчика, триггеров, злементов И, узл тации, причем информационный вход узла соединен с первым входом сумматора по mod 2, выход которого подклю 1ен к выходу поразрядного анализа узла и к первому входу первого злемента И, выход которого соединен с информационным входом первого триггера, прямой выход которого подключен ко второму входу первого элемента И и к выходу переносов первого уробня узла анализа, инверсный - к первому входу первого дешифратора, выход которого соединен с выходом предварительного разделения узла и с информационным входом счетчика, выходы которого соединены с входами узла коммутащш, выход которого подключен к выходу поразрядного анализа второго уровня узйа и первому входу второго элемента И, выход которого соединен с первым входом второго элемента И, выход которого подключен к информационному входу второго триггера, прямой выход которого соединен с вторым входом второго элемента И и с вых дом переноса второго уровня узла анализа, а инверсный - с первым входом второго дешиф ратора, выход которого подключен к выходу результата узла анализа, первый и второй вход синхронизации узла соединены с входами синхронизации первого и второго триггеров соответственно, первый управляющий вход узла анализа подключен ко входу установки в нулевое состояние первого триггера, третий вход синхронизации узла анализа соединен с управляющим входом узла коммутации, первый и второй управляющие входы узла подключены к входам установки в нулевое состояние второго триггера и счетчика соответственно. Причем, коммутатор состоит из злементов И, ИЛИ, триггеров, формирователей импульсов счетчика, при этом первый вход управления коммутатора соединен с информационным вхо дом счетчика, выход переноса которого подключен к первому входу, первого формирователя импульсов, выход которого соединен с первым управляющим выходом коммутатора и с входом второго формирователя импульсов, выход которого подключен к входу установки в единичное состояние первого триггера, пряМОЙ выход которого соединен с первым входом первого злемента И и с входом третьего формирователя, выход которого подключен к второму управляющему входу коммутатора, информационные входы первой и второй групп коммутатора соединены с входами первого и второго элементов ИЛИ соответственно, выход первого элемента ИЛИ подключен к первому входу второго элемента И, выход которого соединен ; с первым выходом синхронизации коммутатора, первый выход генератора тактовых сигналов подключен к выходу коммутатора, второй выход генератора тактовых сигналов соединен с вторым входом второго элемента И и с вторым входом первого элемента И, выход второго элемента ИЛИ подключен к третьему входу первого элемента И, ВХОД блокировки коммутатора соединен с входом установки в нулевое состояние второго триггера, второй вход управления коммутатора подключен к второму входу первого формирователя импульсов и к входу установки в нулевое состояние второго триггера, прямой выход которого соединен с третьим входом второго элемента И, выход третьего формирователя и первого элемента И подключены соответственно к первому и второму управляющим входам коммутатора. На чертеже приведена блок-схема устройства. Устройство содержит п узлов анализа 11, Ь ... (, , каждый из которых состоит из элемента И 2, триггера 3, дещифратора 4, сумматора 5 по mod 2, сче1чика 6, узла коммутации 7, элемента И 8, триггера 9, дешифратора 10, злемента ИЛИ 11, коммутатор 12, состоящий из генератора тактовых сигналов 13, элементов И 14 и 15 триггера 16, счетчика 17, формирователя импульсов 18 и 19, триггера 20, формирователя импульсов 21, элемента ИЛИ 22, вход начальной установки 23, вход опроса 24. На вход сумматора по модулю два 5 каждого узла анализа .1 поступают сравниваемые числа в последовательном коде старшими разрядами вперед и через элемент И 2 попадают на D -вход триггеров. В момент прихода на D-вход синхронизации триггера импульса из коммутатора 12 происходит запись значения этого разряда в триггер. Если данный разряд имеет значение О, то обратной связью с выхода триггера на схему совпадения запрещается дальнейщее изменение, информации на выходе этого D-триггера. По мере появления нулей в разрядах - остальных каналов информации отключается от все больщее количество триггеров 5, пока не останется один, не сработавший триггер. В дешифраторе 4 этого узла анализа вырабатывается сигнал, говорящий о наличии в этом канале максимального числа. Как только появляется такой сигнал на выход дешифратора 4, он проходит через элемент ИЛИ 22 на один из входов триггера 16 коммутатора 12. При-этом сигнал с выхода проти воположного плеча этого триггера закрывает элемент И 14 н тактовые импульсы перестают поступать на входы сишсрош1за аш -фштеров. Таким образом, состояние этх триггеров не меняется до прихода импульса к входу началь ной установки 23, который возвращает их в нулевое состояние. Когда на коммутатор 12 приходит импульс к входу опроса 24, он попадает на другой вхо триггера 16, при этом на элемент И 14 приходит отгнал разрешения, и тактовые импульо. начинают поступать на триггеры. Таким образом, повторяются циклы определения канала с экстремальным числом. В тех случаях, когда описанное устройство должно определить канал с максимальным числом, получающимся в результате фильтрации сигнала из шума, однократно принятое решени будет не достоверно. Поэтому дальше производится усредаение принятых решений за определенный промежуток времени, для чего в каждом из каналов рассматриваемого устройства после дешифраторов 4 включены счетчики которые подсчитывают количество принятых каналов. ,- Полученные за время накопления в счетчиках «шсла с помощью узлов коммутащ1И 7 поступают на вход злементов И 8 и далее на триггеры 9, за которыми включены дешифрато ры 10. Выходы этих дешифраторов через второй элемент ИЛИ 11 соединены с вторым входом триггера 16. Выходы дешифраторов 10 являются выходами устройства, по которым . определяется номер канала, содержащего максимальное число. Накопленные в счетчиках 6 числа начинают сравниваться после того, как в результате совп падения выходного сигнала .счетчика 17 .и кмпульса с выхода элемент ИЛИ 22 формироват ли 18 и 19 сформируют импульсы, которые производят установку триггеров 9 и перебрасывают триггер 20, в результате чего вьфабатывается сигнал, открывающий элемент И 15. С выхода этого элемента тактовые импульсы начинают поступать на входы синхронизации триггеров 9. Эти триггеры срабатывают по мере появления нулей в соответствующих разрядах до тех пор, пока не останется один не сработавший триггер. Прямые и ииверсиые выходы триггеров 9 соединены с дешифраторами Ю. таким образом, когда остается всего один не сработавший триггер, на соответствующем дешифраторе вырабатывается сигнал, кото рый через элемент ИЛИ 11 поступает на второй вход т шггера 20, после чего прекращается поступление импульсов на входы синхронизащш триггеров. Они сохраняют свое состояние до прихода очередного импульса. Из задйего фронта выходного импульса триггера 20 форми руется импульс, устанавливающий счетчики 5 в нулевое состояние. Одновременно выходы : дешифратора 10 являются выходами устройства, которые дают правдоподобную оценку номера канала, содержащего максимальное отношение сигнал/помеха. На вход сумматоров по модулю два пост пает команда в виде О или 1 в результате чего появляется возможность вы6 1фать или максимальное, или минимальное из поступаюцдах чисел. Если во всех сравниваемых числах в одном и том же разряде появляется ноль, в первой или во второй ступенях сравнения, то на выходе элемента ИЛИ 22 или 23, входы которых подключены к выходам полусумматоров и узлов коммутащш 7 соответственно формируется шгнал запрета, который поступает на вход элемента И 14 или 15, тго предотвращает одновременное q a6aTbiBaHKe триггеров. Описанное устройство в отличие от прототипа позволяет определить номер канала с экстремальным числом при небольшом соотношении сигнал/поме: на входе. Формула из-обретения }. Устройство для сравнения чисел, содержащее п узлов анализа, коммутатор, элементы ИЛИ, причем выход результата каждого }-го узла анализа соединен с i-м входом первого элемента ИЛИ, где i 1, 2 . . . , п, выход которого подключен к входу блокировки коммутатора, входная шина каждого i-ro числа соединена с информационным входом i-ro узла анализа, отличающееся тем, что, с целью повышения достоверности выделения экстремальных чисел, в нем вход начальной установки устройства соединен с первым управляющим входом коммутатора и с первым управляющим входом каждого узла анализа, выход предварительного разделения каждого г-го узла анализа подключен к i-му входу второго элемента ИЛИ, выход которого соединен с вторым управляющим входом коммутатора вход задания режима устройства подключен к второму управляющему входу каждого узла анализа, первый, второй и третий выходы синхронизации коммутатора подключены к первому, второму и третьему входам синхронизации соответственно каждого узла анализа, выходы поразрядного анализа первого и второго уровней каждого i-ro узла анализа соединены с i-ми информационными входами соответственно первой и второй групп коммутатора, выход переноса первого уровня каждого i-ro уапа анализа подключен к i-му входу переносо первой грзшпы входов 1, 2, ..., i-l, i+1 n-го узлов анализа, выход переноса второго уровня каждого i-ro узла анализа соединен с i-M входом переносов второй группы входов 1, 2, . . ., i-1, i+I, . . ., п-го узлов анализа, первый и второй выходы управления коммутатора подключены к третьему и четвертому управляющим входам узлов анализа. 2. Устройство по п. 1, отличающе с я тем, что в нем каждый узел анализа состоит из сумматора по mod 2, дешифраторо счетчика, триттеров, злементов И, узла комму тации, причем информационный вход узла соединен с первым входом сумматора по mod 2, выход которого подключен к выходу поразрядного анализа узла и к первому входу первого злемента И, выход которого соединен с информационным входом . первого триггера, прямой выход которого подключен к второму входу первого элемента И и к выходу переносов первого уровня узла анализа, инверсный к первому входу первого дешифратора, выход которого соединен с выходом предваритбльного разделения узла и с информационным вхо, .дом счетчика, выходы которого соединены с входами узла коммутации, выход которого подключен к выходу поразрядного анализа второго уровня узла и первому входу второго элемента И, выход которого соединен с первым входом второго элемента И, выход которого подключен к информационному входу второго триггера, прямой выход которого соединен с вторым входом второго элемента И и с выходом переноса второго уровня узла анализа, а инвесрный - с первьпи входом второго дешифратора, выход которого подключен к выходу результата узла анализа, первый и второй входьь :синхронизации узла соединены с входами синхронизации первого и второго триггеров соответственно, первый управляющий вход узла анализа подключен к входу установки в нулевое состояние первого триггера, третий вход синхронизации узла анализа соединен с управляющим входом узла коммутации, первый и второй утфавл5цощие входы узла подключены к входам установки в нулевое состояние второго триггера и счетчика соответственно. 3. Устройство по п. 1,отличающее0 я тем, что коммутатор состоит из элементов И, ИЛИ, триггеров, формирователей импульсов, счетчика, причем первый вход управления коммутатора соединен с информационным входом счетчика, выход переносов которого подключен к первому входу первого формирователя импульсов, выход которого соединен с первым управляющим выходом коммутатора и с входом второго формирователя импульсов, л.. выход которого подключен к входу установки в единичное состояние первого триггера, прямой выход которого соединен с первым входом первого элемента И И с входом третьего формирователя, выход которого подключен к второму управляю- ч щему входу коммутатора, информационные входы первой и второй групп коммутатора соединены с входами первого и второго элементов ИЛИ соответственно, выход первого элемента ИЛИ подключен к первому входу второго элемента И, выход которого соединен с первым выходом синхронизации коммутатора, первый выход генератора тактовых сигналов подключен к второму выходу коммутатора, второй выход генератора тактовых сигналов соединен с вторым входом второго элемента И и с вторым входом первого элемента И, выход второго элемента ИЛИ подключен к третьему входу первого элемента И, вход блокировки коммутатора соединен с входом установки в нулевое состояние второго триггера, второй вход управления коммутатора подключен к вторсмлу входу первого формирователя импульсов и к входу установки в нулевое состояние второго триггера, прямой выход которого соединен с третьим входом второго элемента И, выход третьего формирователя и первого элемента И подключены соответственно к первому и второму управляющим выходам коммутато15а. Источники информапяи, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 285347, кл. G 06 F 7/00, 1968. 2.Авторское свидетельство СССР N 729586, кл, G 06 F 7/04, 1978 (прототип).

Авторы

Даты

1982-08-15—Публикация

1980-10-29—Подача