(5) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1983 |

|

SU1246137A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| Запоминающее устройство | 1974 |

|

SU536524A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Микропрограммное устройство управления | 1980 |

|

SU955059A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

1

Изобретение относится к вычислительной технике и может быть использовано при конструировании оперативных запоминащих устройств ЭВМ последовательного действия.

Известно запоминающее устройство с прямой адресацией, используемое в качестве оперативных ЗУ ЭВМ на ферромагнитных элементах памяти СООбщими недостатками известного ЗУ являются необходимость восстановления информации при считывании и сложность изготовления. Магнитные запом1 1ающие устройства, изготовленные интегральным способом, имеют ограниченное быстродействие, так как увеличение амплитуды адресных токов, способствующее увеличению скорости перемагничивания, приводит к разрушению информации в соседних ячейках. По мере возрастания быстродействия резко увеличивается влияние помех, борьба с которыми приводит к усложнению аппаратуры, увеличению ее стоимости, затруднению поиска неисправностей и снижению надежности запоминающего устройства.

Наиболее близким к предлагаемому по технической сущности является запоминающее устройство с прямой адресацией на регистрах с параллельными записью и считыванием информации, имеющие более высокое быстродейст,Q ,вие по сравнению с магнитным 2.

Однако большое количество шин ограничивает быстродействие роста помех. Кроме этого применение такого ЗУ в ЭВМ последовательного ствия затруднительно.

Цель изобретения - повышение быстродействия устройства и его надежности.

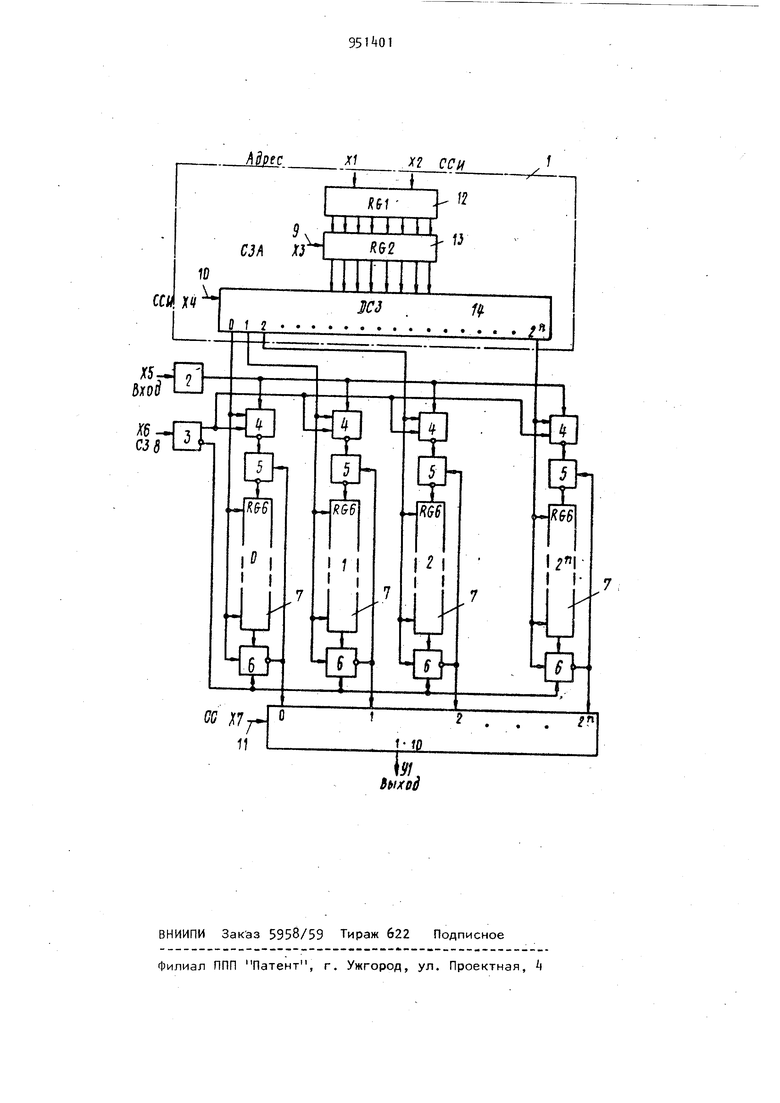

Поставленная цель достигается тем, 20 что в запоминающее устройство, содержащее адресный блок, входы которого являются адресными входами устройства, регистры хранения информации,, коммутатор и шины управления, введены первый и второй формирователи, три группы элементов И-НЕ, причем вход первого формирователя соединен с первыми входами элементо И-НЕ первой группы, вторые входы элементов И-НЕ первой группы соеди.нены с первым выходом второго форми рователя, вход которого соединен с первой шиной управления, третьи входы элементов И-НЕ первой группы соединены с соответствущими выходами адресного блока и адресными входами регистров хранения информа ции, управляющие входы адресного блока соединены соответственно со второй и третьей шиной управления, первые входы элементов И-НЕ второй группы соединены с выходами элементов И-НЕ первой группы, выходы элементов И-НЕ второй группы соединены с информационными входами регистров хранения информации, выходы которых подключены к первым входам элементов И-НЕ третьей группы, вторые вхо ды элементов И-НЕ третьей группы со динены с вторым выходом второго формирователя, вторые входы элементов И-НЕ второй группы соединены с выходами элементов И-НЕ третьей группы и с информационными входами коммутатора, третьи входы элементов И-НЕ третьей группы соединены с выходами адресного блока, выход коммутатора является выходом устройства, управля ющий вход коммутатора соединен с четвертой шиной управления, а также тем, что адресный блок содержит посл довательно соединенные первый, второй регистры и дешифратор, выходы ко торого являются выходами адресного блока, входы- первого регистра являются адресными входами адресного бло ка, управляющие входы регистров являются входами управления адресного блока. На чертеже изображена функциональ ная схема предлагаемого устройства. Оно содержит адресный блок 1, фор мирователи 2 и 3| элементы И-НЕ -6 первой, второй и третьей групп, реги стры 7 хранения информации, шины 8-11 управления. Адресный блок 1 содержит регистры 12 и 13, дешифратор Н. Предлагаемое устройство функционирует следующим образом. Адрес ячейки памяти, в которую на до записать или из которой надо считать информацию, последовательным кодом поступает в регистр 12, по сиг 14 налу приема адреса (СПА) параллельным кодом переписывается в регистр 13. Дешифратор k в соответствии с.адресом по сдвигающим синхроимпульсам (ССИ) на одном из выходов (0,1, 2,...,2 ) формирует сдвигающие синхроимпульсы, обеспечивающие прием входной информации в соответствующий адресу хранящий регистр 6 при наличии сигнала записи (СЗ ) или выдачу информации из этого регистра при наличии сигнала считывания, разрывается сигналами записи. Так как сдвигающие импульсы поступают с выхода дешифратора только на один хранящий регистр, но в остальных хранящих регистрах потери информации быть не может о Сигнал записи адреса (СЗА) должен быть импульсным, а сигнал записи (СЗ) и сигнал считывания (СС могут быть потенциальными, но по длительности должны равняться времени сдвига всех разрядов так, чтобы суммарное время приема адреса. дешифрации адреса и задержек на входе или выходе регистров 7 равнялось времени сдвига всех разрядов каждого регистра 7. Это значит, что при большей разрядности слов количество регистров 7 можно увеличить, но при этом необходимо помнить и об увеличении задержки на дешифрацию, ввод или вывод информации при увеличении количества разрядов в адресе Точное соотношение можно определить зная характеристики элементной базы. Применение предлагаемого устройства для построения оперативных запоминающих устройств ЭВМ последовательного действия позволяет сократить номенклатуру базовых элементов в ЭВМ, упростить обслуживание ЭВМ, повысить их надежность и быстродействие, так как современною регистры, выполненные по интегральной технологии, имеют высокую надежность и лучшую помехоустойчивость при частотах, как минимум, на порядок выше рабочих частот магнитных элементов памяти, а однотипность элементной базы благоприятно сказывается на всех этапах проектирования и эксплуатации ЭВМо Для построения ЗУ на шестнадцатиразрядных слов требуется не более 1500 корпусов интегральных импульсов микросхем 133 или И серий (1028 элементов К155ИР1), 37 элемен59

тов К 155ЛБ2, 176 элементов К 155ЛБ и элемента К155ЛБЗ) а быстродей ствие ЗУ полностью соответствует быстродействию ЭВМ, построенной на этой же элементной базе.

Использование однокорпусных многоразрядных последовательныхрегистров и однокорпусных импульсных дешифраторов существенно сокращает габариты, повышает надежность и технологичность ЗУ, Ремонт ячейки памяти предлагаемого ЗУ сводится к замене микросхемы, а поиск и устранение такой неисправности в процессе эксплуатации не вызывает затруднений.

Формула изобретения

16

входы адресного блока соединены соответственно с второй и третьей шинами управления, первые входы элементов И-НЕ второй группы соединены с

выходами элементов И-НЕ первой группы, выходы элементов И-НЕ второй группы соединены с информационными входами регистров хранения информации, выходы которых подключены к первым входам элементов И-НЕ третьей группы, вторые входы элементов И-НЕ третьей группы соединены с вторым выходом второго формирователя, вторые входы элементов И-НЕ второй группы соединены с выходами элементов И-НЕ третьей группы и с информационными входами коммутатора, третьи входы элементов И-НЕ третьей группы соединены с выходами адресного блока, выход коммутатора является выходом устройства, управляющий вход коммутатора соединен с четвертой шиной управления.

принятые во внимание при экспертизе

Авторы

Даты

1982-08-15—Публикация

1980-06-18—Подача