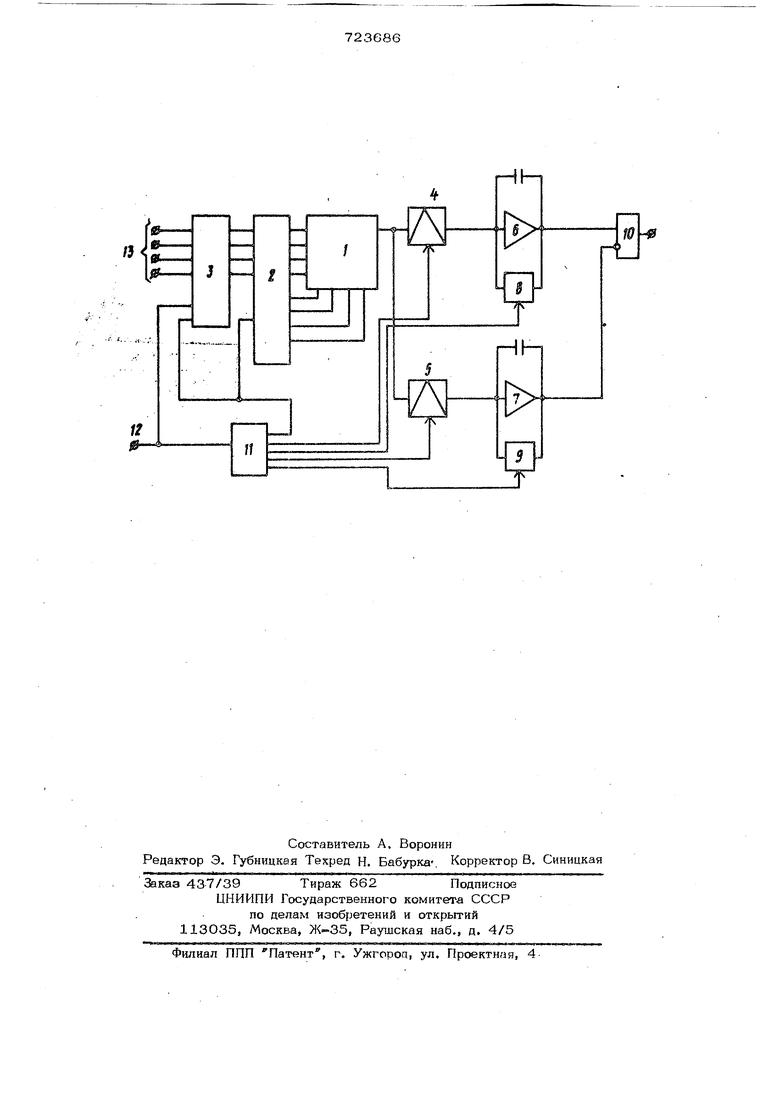

Изобретение относится к области аналоговой вычислительной техники и может быть использовано в устройствах автоматики, измерительной и вычислительной техники. Известно аналоговое запоминающее устройство, содержащее накопитель, блок выбора адреса, устройство записи, и выходное устройство, включающее в себя два интегрирующих усилителя с разрядными ключами в цепи обратной связи, фильтр нижних частот, выходной усилитель и генератор тактовых импульсов, причем вход каждого интегрирующего усилителя соединен с отдельной выходной шиной накопителя, выходы интегрирующих усилителей соединены с входом фильтра, выход фильтра соединен со входом выходного усилителя, а управляющие входы разрядных ключей соединены с выходами генератора тактовых импульсов ij . Данное устройство имеет ограниченные функциональные возможности и услож ненную конструкцию в связи с наличием двух независимых выходных шин накопителя. Известно также аналоговое запоминающее устройство, выполненное на накопителе из элементов памяти, построенных на трансфлюксорах, содержащее блок выбора адреса, устройство записи, блок поочередной выдачи адресов элементов памяти, по которым осуществляется сложение или вычитание, и выходное устройство, включающее в себя схему стробирования, фильтр нижних частот, усилитель и генератор тактовых импульсов считывания, причем один вход блока поочередной выдачи адресов соединен с выходом генератора тактовых импульсов параллельно одному входу блока выбора адреса, другой вход подключен параллельно входу управления режимами указанного вьпие генератора и является входом управления устройства, остальные входные шины предназначены для приема адресов, а выходные шины соединены с блоком выбора адреса, один выход генератора тактовых импульсов считывания присоедгнен к блоку выбора адреса, а другой к схеме стробирования 2}. Недостатком такого устройства явля ется низкое быстродействие, Целью предлагаемого изобретения является повышение быстродействия устрой ства. Поставленная цель достигается тем, что в аналоговое ;мпоминающее устройст во, содержащее накопитель, входы кото рого подключены к выходам блока вы борки адресов, блок поочередной выдачи адресов, первые входы которого соединены с информационными шинами устро ства, второй вход блока поочередной выдачи кодов адресов подключен к шине управления и входу генератора тактовых импульсов, первый выход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из вхо дов блока выборки адресов, другие входы которого соединены с выходами блока по очередной выдачи кодов адресов, первый блок стробирования, один из входов которого соединен со вторым выходом генератора тактовых импульсов, дифференциал ный усилитель, выход которого соединен с выходом устройства, в него введены интегрирующие усилители и второй блок стробировання,. один из входов которого соединен с третьим выходом генератора тактовых импульсов, другие входы блоков стробирования соединены с выходом накопителя, выходы блоков стробирования сое динены с одними из входов интегрирующих усилителей соответственно, выходы интегрирующих усилителей соединены соответственно со входами дифференциального усилителя, другие входы интегрирующих усилителей подключены к четвертому и пятому выходам генератора тактовых импульсов соответственно. Предлагаемое устройство представлено на чертеже. Устройство содержит накопитель 1, блок выборки адресов 2, блок 3 поочеред ной вьщачи кодов адреса. Элементы стробирования 4, 5 J интегрирующие усилите-ли 6 и 7, ключи 8, 9, дифференциальный усилитель 10, генератор тактовых импуль сов 11 и шину управления 12, информационные шины 13, Устройство работает следующим образом, В режиме считывания одного числа генератор тактовых импульсов 11 выдает на входы блока выбора адреса 2 и блока 3 поочередной выдачи кодов адресов, который обеспечивает выбор адреса единственного элемента в накопителе. Элемент стробирования 4 пропускает сигнал с выходной шины накопителя 1, открываясь по окончанию импульса, стробирую- щего сигнал от импульса подготовки, Эле мент стробирования S начинает пропускать входной сигнал после окончанийпроцесса интегрирования первого импульса считывания. В результате такого режима коммутации со сдвигом на выходах интегрирующих усилителей 6 и 7 образуются две последовательности импульсов, сдви нутых одна относительно другой на половину периода частоты считывания. После суммирования этих последовательностей дифференциальным усилителем 1О уже в первом рабочем такте считывания на выходе устройства ьоявляется выходной сигнал, зависящий только от величины уровня информации, хранившейся в выбранном элементе памяти. Ключи 8 и 9 замыкаются в. моменты отсутствия напряжения сигнала на интег рирующих усилителей 6 и 7 и предназначены для ликвидации дрейфа нуля интегрирующих усилителей. Следует отметить, что ддя упрощения рассмотрения работы устройства на чертеже не показано устройство записи. Режим суммирования двух считываемых чисел осуществляется путем изменения программы стробирования элементов 4 и 5 и программы выбора адреса, выдаваемой генератором тактовых импульсов 11. Одновременно с этим изменяется программа коммутации ключей 8 и 9, После интегрирования последовательностей импульсов, получаемых в результате считывания двух чисел (при этом больший по амплитуде сигнал соответствует первому числу, меньший - второму, положительная полярность соответствует сигналу от импульса считывания, отрицательная - от импульса подготовки) интегрирующими усилителями 6 и 7 и суммирования дифференциальным усилителем 10 на вь1ходе устройства уже во втором раёочем периоде считывания появляется сигнал, соответствующий сумме двух считываемых чисел. Ключи 8 и 9 замыкаются в моменты отсутствия напряжения сигнала на интегрирующих усилителей б и 7 и предназначены для ликвидации дрейфа нуля интег« рирующих усилителей. Режим вьгчитания одного числа из I другого осуществляется путем изменения

программы стробнровання элементов 4 и 5 и программы коммутации ключей 8 и 9 при помощи генератора тактовых импульсов 11. Режим процесса поочередного считывания чисел аналогичен выше приведенному в режиме сложения, В результате коммутации элементов стробирования 4 и 5 на их выходах появляются последовательности импульсов, после ин. егрирования которых интегрирующими силиями 6 и 7, и суммирования их ди4 еренциальным усилителем 10 во втором рабочем такте считывания на выходе стройства появляется сигнал, соответствующий разности двух считываемых исел. Ключи 8 и 9 сохраняют режим оммутации, аналогичный выше приведенному.

Применение при считывании интегриования выходных сигналов с накопителя 1 по сравнению с режимом усреднения, используемом в прототипе, дает возможность получить сигнал на выходе усгрой- ства, соответствующий считываемой информации, уже в первом рабочем такте считывания в режиме считывания одного числа и во втором рабочем такте считывания в режимах сложения и вычитания, что существенно повышает быстродействие аналогового запоминающего устройства, так как время считывания одного числа не превышает в этом случае длительности двух периодов частоты считывания, а время выполнения операций сложения или вычитания - длительности че- тырех периодов частоты считывания.

Таким образом, достигнуто повышение быстродействия устройства. Кроме, того, выходное напряжение устройства не зависит от частоты считывания.

Формула изобретения

Аналоговое запоминающее устройство, содержащее накопитель, входы которого

подключены к выходам блока выборки адресов, блок поочередной выдачи кодов адресов, первые входы которого соединены с информационными шинами устройства,

второй вход блока поочередной выдачи кодов адресов подключен к шине управления и входу генератору тактовых импульсов, первый выход которого соединен с третьим входом блока поочередной выда-

чи кодов адресов и одним из входов блока выборки адресов, другие вхсды которого соединены с выходами блока поочеред- ной выдачи кодов адресов, первый блок стробирования, один из входов которого соединен со вторым выходом генератора тактовых импульсов, дифференциальный у.силитель, выход которого соединен с выходом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены интегрирующие усилители и второй блок стробирования, один из входов которого соединен с третьим выходом генератора тактовых импульсов, другие входы блоков стробирования соединены с выходом накопителя; выходы блоков стробирования соединены с одними из зходов интегрирующих усилителей соответственно, выходы интегрирующих усилителей соединены соответственно со входами дифференциального усилителя, другие входы интегрирующих усилителей подключены к четвертому и пятому выходам генератора тактовых импульсов соответственно.

Источники информации, принятые во внимание при экспертизе

1.Быстродействующее устройство считывания информации для аналоговых ЗУ на транс(}в1юксорах.-Приборы и системы

.управления, № 8, 1975

2.Авторское свидетельство СССР по заявке № 2465511,

кл. G 11 С 27/00 от 22.03.77 (npoi.тотип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1977 |

|

SU684619A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU720514A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799014A1 |

| Адаптивный коммутатор телеизмерительной системы | 1990 |

|

SU1785020A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

Авторы

Даты

1980-03-25—Публикация

1977-05-12—Подача