(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО Изобретение относится к аналоговой вычислительной технике и может быть использовано в устройствах автоматики, измерительной и вычислительной техники. Известно магнитное аналоговое запоминающее устройство, содержащее накопитель из элементов памяти, построенных на трансфлюксорах, блок выбора адреса, устройство записи, блок поочередной выдачи адресов элементов памяти, по которым осуществляется сложение или вычитание, и выходное устройство, включающее в себя схему стробирования, фильтр нижних частот, усилитель и генератор тактовых импульсов считывания, причем один вход блока поочередной выдачи адресов соединен с выходом генератора тактовых импульсов параллельно одному входу блока выбора адреса, другой вход подключен параллельно входу управления режимами указанного выще генератора и является входом управления устройства, остальные входные щины предназначены для приема адресов, а выходные щины соединены с блоком выбора адреса, а один выход генератора тактовых импульсов считывания присоединен к блоку выбора адреса, а другой - к схеме стробирования 1. Недостаток устройства - низкое быстродействие. Наиболее близким из известных по технической сущности является аналоговое запоминающее устройство, содержащее накопитель, входы которого подключены к выходам блока выборки адресов, блок поочередной выдачи кодов адресов, первые в.ходы которого соединены с информационными щинами устройства, второй вход блока поочередной выдачи кодов адресов подключен к щине управления и входу генератора тактовых импульсов, первый вход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из входов блока выборки адресов, другие входы которого соединены с выходами блока поочередной выдачи кодов адресов, два блока стробирования, интегрирующие усилители и дифференциальный усилитель, причем один из входов первого блока стробирования соединен со вторым выходом генератора тактовых импульсов, один из входов второго блока- стробирования соединен с третьим выходом генератора тактовых импульсов, другие входы блоков стробирования соединены с выходом накопителя, выходы блоков

стробирования соединены с одними из входов интегрирующих усилителей соответственно, выходы интегрирующих усилителей соединены соответственно со входами дифференциального усилителя, другие входы интегрирующих усилителей подключены к четвертому и пятому выходам генератора тактовых импульсов соответственно 2.

Недостаток устройства - сложность конструкции, обусловленная наличием двух схем стробирования.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее последовательно соединенные блок управления, блок выборки адресов и накопитель, интегрирующие усилители, одни из входов которых соединены с первым и вторым выходами генератора тактовых импульсов соответственно, выходы интегрирующих усилителей соответственно подключены ко входам дифференциального усилителя, шину управления, соединенную со входом генератора тактовых импульсов и первым входом блока управления, второй вход которого соединен с третьим выходом генератора тактовых импульсов и вторым входом блока выборки адресов, информационные шины, соединенные с третьими входами блока управления, введен ключ, первый вход которого соединен с выходом дифференциального усилителя, выход ключа соединен с выходом устройства, второй вход ключа подсоединен к четвертому входу генератора тактовых импульсов, пятый выход которого соединен с третьим входом блока выборки адресов, выход накопителя подключен к другим входам интегрирующих усилителей.

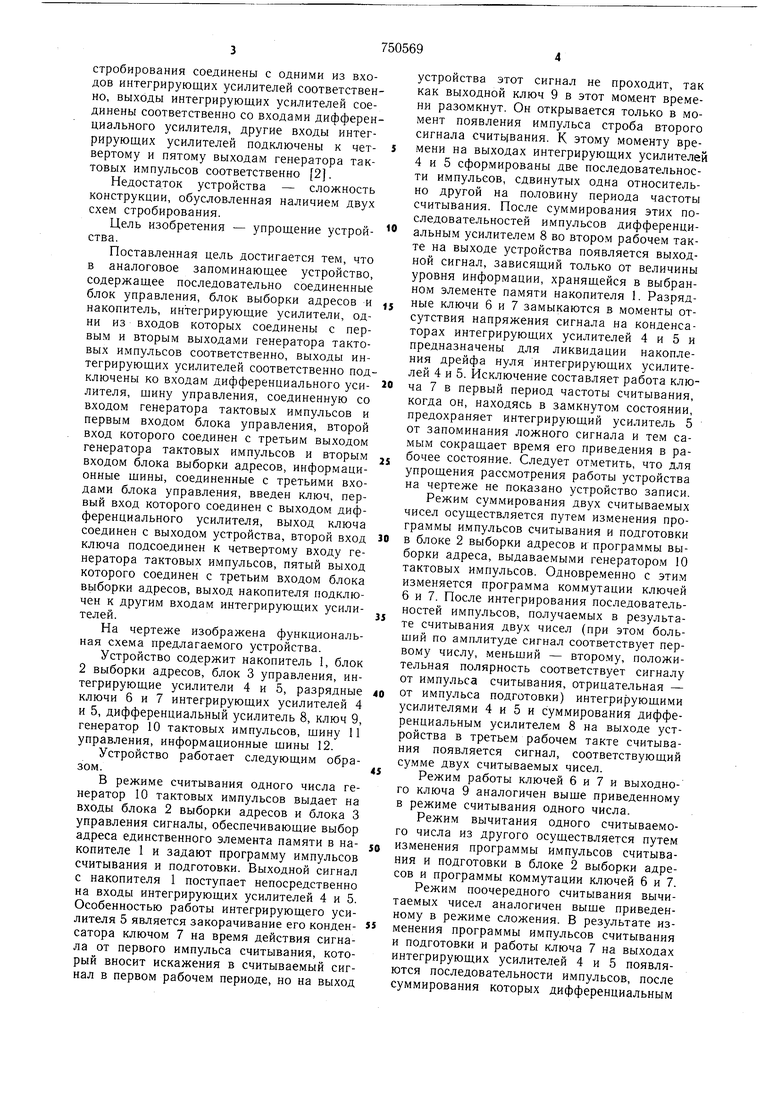

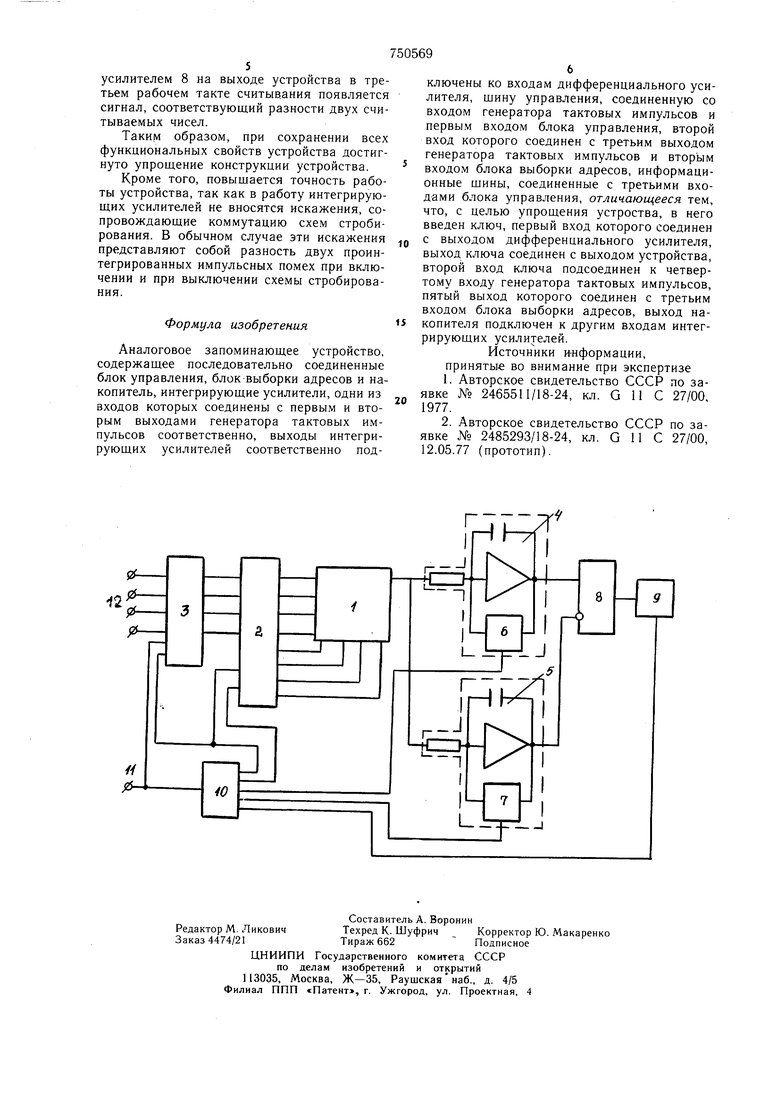

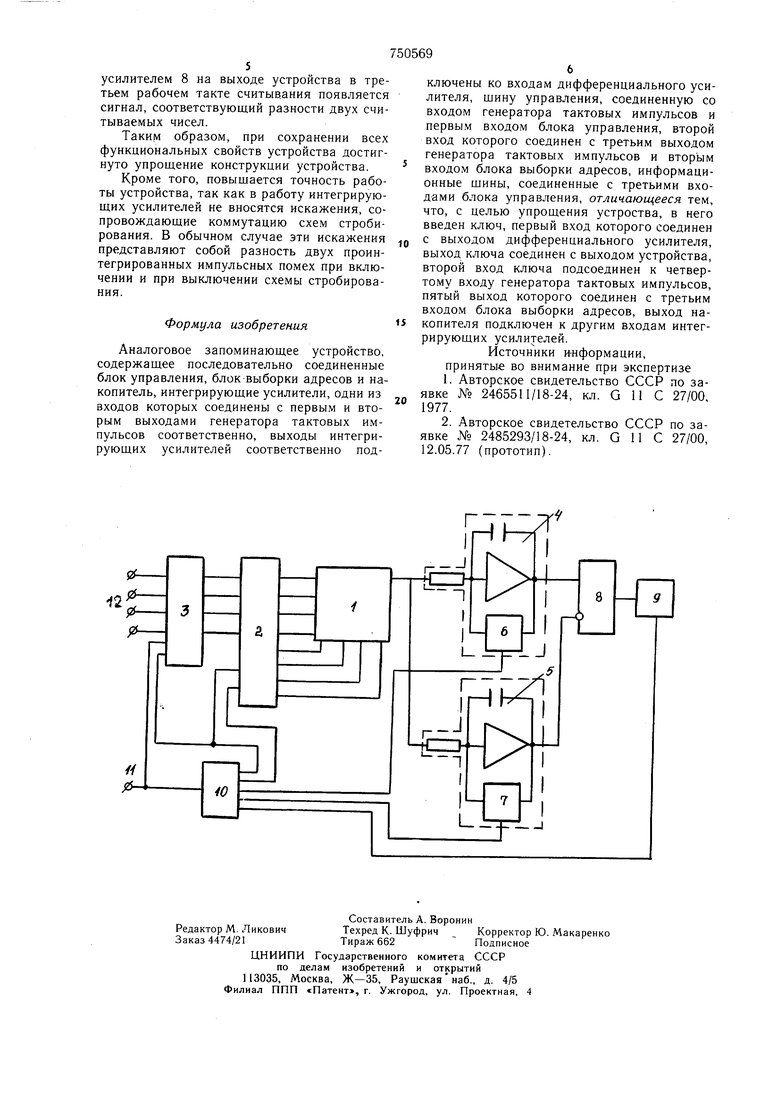

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит накопитель 1, блок 2 выборки адресов, блок 3 управления, интегрирующие усилители 4 и 5, разрядные ключи 6 и 7 интегрирующих усилителей 4 и 5, дифференциальный усилитель 8, ключ 9, генератор 10 тактовых импульсов, шину 11 управления, информационные шины 12.

Устройство работает следующим образом.

В режиме считывания одного числа генератор 10 тактовых импульсов выдает на входы блока 2 выборки адресов и блока 3 управления сигналы, обеспечивающие выбор адреса единственного элемента памяти в накопителе 1 и задают программу импульсов считывания и подготовки. Выходной сигнал с накопителя 1 поступает непосредственно на входы интегрирующих усилителей 4 и 5. Особенностью работы интегрирующего усилителя 5 является закорачивание его конденсатора ключом 7 на время действия сигнала от первого импульса считывания, который вносит искажения в считываемый сигнал в первом рабочем периоде, но на выход

устройства этот сигнал не проходит, так как выходной ключ 9 в этот момент времени разомкнут. Он открывается только в .момент появления импульса строба второго сигнала считывания. К этому моменту времени на выходах интегрирующих усилителе 4 и 5 сформированы две последовательности импульсов, сдвинутых одна относительно другой на половину периода частоты считывания. После суммирования этих последовательностей импульсов дифференциальным усилителем 8 во второ.м рабочем такте на выходе устройства появляется выходной сигнал, зависящий только от величины уровня информации, хранящейся в выбранном элементе памяти накопителя 1. Разрядные ключи 6 и 7 замыкаются в моменты отсутствия напряжения сигнала на конденсаторах интегрирующих усилителей 4 и 5 и предназначены для ликвидации накопления дрейфа нуля интегрирующих усилителей 4 и 5. Исключение составляет работа ключа 7 в первый период частоты считывания, когда он, находясь в замкнуто.м состоянии, предохраняет интегрирующий усилитель 5 от запоминания ложного сигнала и тем самым сокращает время его приведения в рабочее состояние. Следует отметить, что для упрощения рассмотрения работы устройства на чертеже не показано устройство записи.

Режим суммирования двух считываемых чисел осуществляется путем изменения программы импульсов считывания и подготовки в блоке 2 выборки адресов и программы выборки адреса, выдаваемыми генераторо.м 10 тактовых импульсов. Одновременно с этим изменяется программа коммутации ключей 6 и 7. После интегрирования последовательностей импульсов, получаемых в результате считывания двух чисел (при этом больший по амплитуде сигнал соответствует первому числу, меньший - второму, положительная полярность соответствует сигналу от импульса считывания, отрицательная - от импульса подготовки) интегрирующими усилителями 4 и 5 и суммирования дифференциальным усилителем 8 на выходе устройства в третьем рабочем такте считывания появляется сигнал, соответствующий сумме двух считываемых чисел.

Режим работы ключей 6 и 7 и выходного ключа 9 аналогичен выше приведенному в режиме считывания одного числа.

Режим вычитания одного считываемого числа из другого осуществляется путем изменения программы импульсов считывания и подготовки в блоке 2 выборки адресов и программы коммутации ключей 6 и 7.

Режим поочередного считывания вычитаемых чисел аналогичен выше приведенному в режиме сложения. В результате изменения программы импульсов считывания и подготовки и работы ключа 7 на выходах интегрирующих усилителей 4 и 5 появляются последовательности импульсов, после суммирования которых дифференциальным

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1977 |

|

SU684619A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU720514A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ ОПТИМАЛЬНЫЙ ФИЛЬТР | 1973 |

|

SU369693A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799014A1 |

| УСТРОЙСТВО СИГНАЛИЗАЦИИ МЕСТОНАХОЖДЕНИЯ ОБЪЕКТА | 1995 |

|

RU2085997C1 |

Авторы

Даты

1980-07-23—Публикация

1978-07-24—Подача