1

Изобретение относится к области электронного цифрового деления частоты следования импульсов и может быть использовано, например, для построения делителей частоты с коэффициентом деления не равным 2.

Известен цифровой делитель частоты следования .импульсов с коэффициентом деления не равным 2, содержащий триггеры и элементы И, в котором с помощью обратной связи искл1рчается часть устойчивых состояний 1.

Недостатком описанного устройства является пониженное быстродействие.

Наиболее близким по технической сущности к изобретению является делитель частоты следования импульсов, содержащий основной делитель частоты и дополнительный триггер, синхронизирующие входы которых объединены, выход основного делителя частоты соединен с I-входом дополнительного триггера, инверсный вы- .

ход которого соединен с (-входом основного делителя частоты .

Недостатками этого устройства являются снижение быстродействия при больших коэффициентах деления и ограниченный диапазон изменения коэффициента деления.

Цель изобретения - повышение быстродействия при одновременном расjg ширениИ диапазона изменения коэффициента деления.

Поставленная цель достигается тем, что в цифровой делитель частоты сле1дования импульсов, содержащий дели(5 тель частоты и триггер, синхронизирующие входы которых объединены, а выход одного из разрядов делителя частоты подключен к установочному входу триггера, введен логический

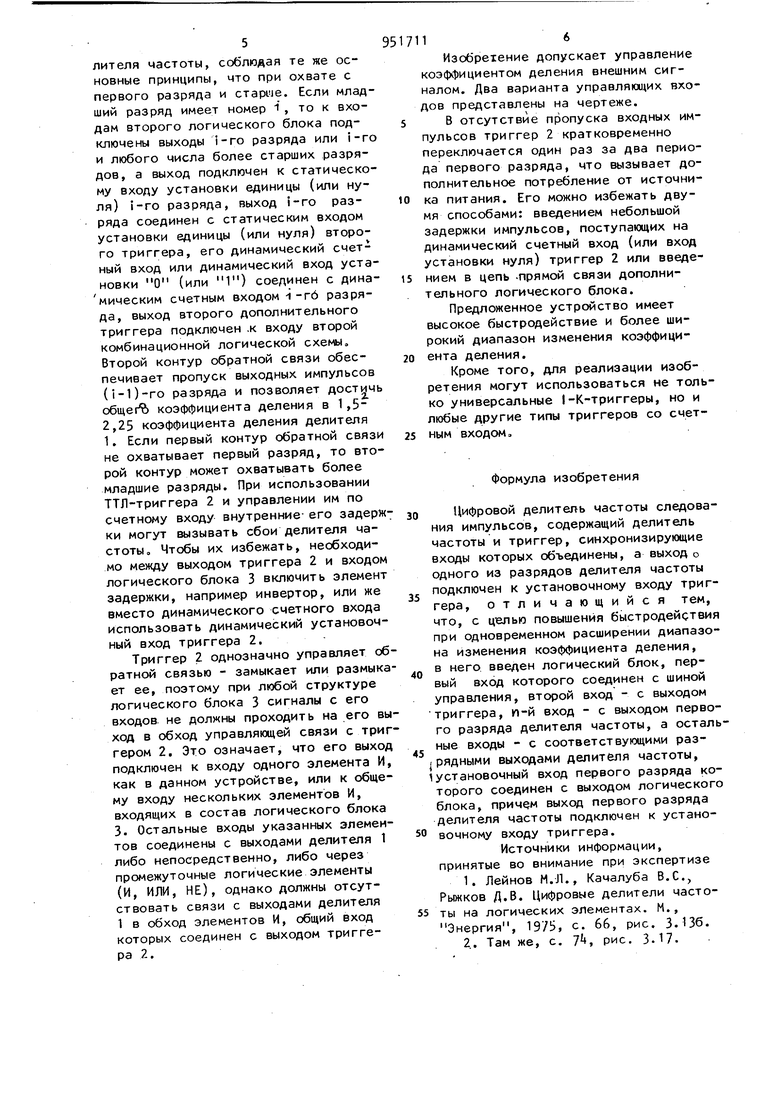

20 блок, первый вход которого соединен с шиной управления, второй вход - с выходом триггера, п-ый вход - с выходом первого разряда делителя частоты, а остальные входы - с соот39ветствующими разрядными выходами делителя частоты, установочный вход первого разряда которого соединен с выходом логического блока, причем выход первого разряда делителя частоты подключен к установочному входу триггера. На чертеже представлена структурная схема устройства Устройство содержит делитель 1 частоты, триггер 2, логический блок 3 в частном случае состоящий из элементов 4 и 5 И-НЕ„ Устройство работает следующим образом. . Когда хотя бы на одном входе элемента 5 присутствует логический ноль он не влияет на работу делителя 1. При наличии логических единиц на всех входах элемента 5 он подтверждает логическую единицу на выходе первого разряда, замыкая таким образом век-, руг делителя 1 положительную обратную связь. Оба управляющих входа должны иметь логическую единицу. В предшествующий такт работы устройства триггер 2 логическим нулем первого разряда устанавливается в состояние логической единицы и сохраняет его в такте замыкания обратной связи, потому что, ввиду задержки в пер вом разряде, его выходной логический ноль снимается после того, как установился переключающий уровень на динамическом счетном выходе ( или динамическом входе установки 0)триггера. Следующий входной импульс не изменяет состояние делителя 1, так как его первый разряд заблокирован с выхода элемента 5, но изменяет ссютояние триггера 2, который через элемент 5 снимает сигнал установки единицы первого разряда, подготавливая его и весь делитель 1 к приему последую1цих входных импульсов. Ввиду з задержки в триггере 2 и элементе 5 сигнал установки единицы первого раз ряда снимается после того, как установился переключающий уровень на его динамическом счетном входе, поэтому состояние первого разряда не изменяется. Таким образом, происходит пропуск одного входного импульса, что означает увеличение общего коэффициента деления на 1. Такое приращение коэффициента деления происходит три ды: когда на выходе разрядов делите14ля 1 от четвертого до п-го включительно одновременно присутствуют логические единицы, то логическая единица первого разряда трижды (при логическом нуле на выходах второго или/и третьего разрядов) вызывает логический нуль на выходе элемента 5 и .соответствующий пропуск следующего входного импульса. В результате устройство имеет коэффициент деления равнений 2°+3. Для общего случая логический блок 3 способен замыкать положительную обратную связь при любом выходном коде делителя 1. Каждый раз после этого происходит пропуск одного входного импульса, и соответствующий период первого разряда возрастает на один период входных импульсов (таково приращение одного полупериода), другой остается неизменным, потому что положительная обратная связь действует только по одному статическому входу установки состояния 1-го разряда. Если делитель 1. является обычным двоичным счетчиком, имеющим коэффициент деления 2 , то при пропуске входного импульса период первого разряда возрастает в 1,5 раза, максимальный коэффициент деления для общего случая блока 3 в 1,5 раза превышает коэффициент деления счетчика, так как каждый период первого разряда получает приращение. В общем случае делитель 1 может иметь любой коэффициент деления не равный 2 , и тогда максимальное относительное его приращение меньше 0,5 коэффициента деления делителя 1, если полупериод с уровнем логической 1 превышает половину периода первого разряда. Чтобы достичь относительного приращения свыше 0,5 необходим второй контур положительной обратной связи: с помощью второго логического блока и дополнительного триггера. Один ее вариант - на статический вход установки нуля первого разряда, при этом дополнительным пропускам входных импульсов, обеспечивающим дсЯэавочное. приращение коэффициента деления, соответствует удлинение такого же числа полупериодов первого разряда с уровнем логического нуля. Другой вариант положительной обратной связи: охватить ею группу более старших разрядов основного делителя частоты, соблюдая те же основные принципы, что при охвате с первого разряда и старше. Если младший разряд имеет номер 1, то к входам второго логического блока подключены выходы i-ro разряда или i-ro и любого числа более старших разрядов, а выход подключен к статическому входу установки единицы (или нуля) i-ro разряда, выход i-ro разряда соединен с статическим входом установки единицы (или нуля) второго триггера, его динамический счетный вход или динамический вход установки О (или 1) соединен с динамическим счетным входом-i-г6 разряда, выход второго дополнительного триггера подключен .к входу второй комбинационной логической схемь. Второй контур обратной связи обеспечивает пропуск выходных импульсов (i-l)-ro разряда и позволяет достичь общеЛ коэффициента деления в 1 ,52,25 коэффициента деления делителя 1, Если первый контур обратной связи не охватывает первый разряд, то второй контур может охватывать более младшие разряды. При использовании ТТЛ-триггера 2 и управлении им по счетному входу внутренние-его задержки могут вызывать сбои делителя частоты. Чтобы их избежать, необходимо между выходом триггера 2 и входом логического блока 3 включить элемент задержки, например инвертор, или же вместо динамического счетного входа использовать динамический установочный вход триггера 2.

Триггер 2 однозначно управляет обратной связью - замыкает или размыка ет ее, поэтому при любой структуре логического блока 3 сигналы с его входов не должны проходить на его вы ход в обход управляющей связи с триггером 2, Это означает, что его выход подключен к входу одного элемента И, как в данном устройстве, или к общему входу нескольких элементов И, входящих в состав логического блока 3. Остальные входы указанных элементов соединены с выходами делителя 1 либо непосредственно, либо через промежуточные логические элементы (И, ИЛИ, НЕ), однако должны отсутствовать связи с выходами делителя 1 в обход элементов И, общий вход которых соединен с выходом триггера -.

517116

Изобретение допускает управление коэффициентом деления внешним сигналом. Два варианта управляющих входов представлены на чертеже.

5В отсутствие пропуска входных импульсов триггер 2 кратковременно переключается один раз за два периода первого разряда, что вызывает дополнительное потребление от источниto ка питания. Его можно избежать двумя способами: введением небольшой задержки импульсов, поступающих на динамический счетный вход (или вход установки нуля) триггер 2 или введе15 нием в цепь -прямой связи дополнительного логического блока.

Предложенное устройство имеет высокое быстродействие и более широкий диапазон изменения коэффици20 ента деления.

Кроме того, для реализации изобретения могут использоваться не только универсальные 1-К-триггеры, но и любые другие типы триггеров со счет25 ным входом

Формула изобретения

Цифровой делитель частоты следования импульсов, содержащий делитель частоты и триггер, синхронизирующие входы которых объединены, а выход о одного из разрядов делителя частоты подключен к установочному входу триггера, отличающийся тем, что, с целью повышения быстродействия при одновременном расширении диапазона изменения коэффициента деления, в него введен логический блок, первый вход которого соединен с шиной управления, второй вход - с выходом триггера, п-й вход - с выходом первого разряда делителя частоты, а остальные входы - с соответствующими разрядными выходами делителя частоты.

установочный вход первого разряда которого соединен с выходом логического блока, причем выход первого разряда делителя частоты подключен к установочному входу триггера.

Источники информации, принятые во внимание при экспертизе

1. Лейнов М.Л., Качалуба B.C., Рыжков Д.В. Цифровые делители частоты на логических элементах. М., Энергия, 1975, с. 66, рис. 3.136. 2.. Там же, с, 7, рис. 3.17.

.Ч.У

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения электрической нагрузки | 1989 |

|

SU1698797A2 |

| Преобразователь синусоидальных сигналов перемещения в код | 1984 |

|

SU1234968A1 |

| Умножитель частоты | 1990 |

|

SU1797113A1 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Управляемый делитель частоты | 1976 |

|

SU658741A1 |

| Устройство для генерации пачек импульсов | 1984 |

|

SU1234953A1 |

| Делитель частоты импульсов | 1985 |

|

SU1298907A1 |

| Частотно-импульсное устройство для извлечения квадратного корня | 1976 |

|

SU605212A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

Авторы

Даты

1982-08-15—Публикация

1978-10-19—Подача