триггера признака записи, единичный выход триггера переключения подключен к первым входам второго и четвертого элементов И и третьему выходу блока, нулевой выход этого триггера к первым входам третьего и пятого ; элементов И и четвертому выходу блока третий вход блока соединен с вторыми входами второго и пятого элементов И, а четвертый вход блока - с вторыми входами третьего и четвертого элементов И, вход первого счетчика адреса подключен к выходам второго и третьего элементов И, а выход - к входу первого дешифратора, вход второго счетчика адреса соединен с выходами четвертого и пятого элементов И, а выход - с входом второго дешифратора, выходы первого и второго дешифраторов подключены соответственно к первому и второму выходам блока.

3. Машина по п. 1, отличающаяся тем,что блок управления сложением содержит счетчик, тактов, дешифратор тактов, регистр операций, коммутатор операций и выходной коммутатор, причем первый вход блока соединен с входом счетчика тактов, выход которого подключен к входу дешифратора тактов, второй вход блока соединен с входом регистра операций, выход которого подключен к входу коммутатора операций, первый и второй входы выходного коммутатора соединены с выходами соответственно дешифратора тактов и коммутатора операций, а выход выходного коммутатора - с вьгходом блока.

4. Машина по п. 1, отличающаяся тем, что блок управления памятью содержит счетчик адреса и. коммутатор адреса, причем вход блока соединен с входом счетчика адреса, выход которого подключен к входу коммутатора адреса, а выход коммутатора ;адреса соединен с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для формирования и обработки гистограмм | 1989 |

|

SU1755296A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

1. ВЫЧИСЛИТЕЛЬНАЯ МАШИНА, содержащая входной регистр, регистр строки, арифметическое устройство, блок управления сложением, блок памяти подпрограмм, блок оперативной памяти -и блок управления памятью, при , этом информационный вход-выход машины соединен с первым входом входного регистра, первый и второй входы блока управления сложением подключены соответственно к выходу блока памяти подпрограмм и первому выходу регистра строки, первый, второй и третий входы арифметического устройства соединены соответственно с выходом блока управления сложением и вторым и третьим выходами регистра строки, а информационный и адресный входы блока оперативной памяти подключены к выходам соответственно арифметического устройства и блока управления памятью, отличающаяся тем, что, с целью повьго1ения производительности, она содержит блок регистров команд, блок управления подготовкой команд и четыре группы элементов И, причем информационный выход блока оперативной памяти подключен к первому входу регистра строки и второму входу входного регистра, выход которого соединен с первыми входами элементов И первой и второй групп, первый и вто рой информационные входы блока регистров команд подключены к выходам элементов И соответственно первой и второй групп, а первый и второй информационные выходы - к первьм входам элементов И соответственно третьей и четвертой групп, выходы которых соединены с входами блока управления памятью и вторым входом регистра строки, первый и второй адресные входы блока регистров команд подключены соответственно к первому и второму выходам блока управления подготовок команд, третий вход которого i соединен с вторьп и входами элементов И первой и четвертой групп, четвертый (Л выход - с вторыми входами элементов И второй и третьей групп первый и второй входы конца массива, вход конца вычислений и синхронизирующий вход машины подключены соответственно к первому, второму, третьему и четверто со ел му входам блока управления подготовкой команд. 2. Машина по п. 1, отличающаяся тем, что блок управления со подготовкой команд содержит два счетсо чика адреса, два дешифратора, пять элементов И, триггер переключения, триггер признака записи и линию адержки, причем первый вход блока соединен с первым входом тр иггера приз нака записи, выход которого подключен к первому входу первого элемента И, второй вход блока соединен с вторым входом первого элемента И, выход которого подключен к входам триггера переключения и линии задержки, выход которой соединен с вторым входом

I

Изобретение относится к вычислительной технике.

Известны устройства обработки информации с применением магнитных Kap

Известна также вычислительная машина, которая содержит входной регистр, регистр строки, арифметическое устройство, блок управления сложением, блок памяти подпрограмм, бло оперативной памяти и блок управления памятью, при этом информационный вход-выход мапшны соединен с первым входом входного регистра, первый и второй входы блока управления еложением подключены соответственно к выходу блока памяти подпрограмм и первому выходу регистра строки, первый, второй и третий входы арифметического устройства соединены соответственно с выходом блока управления сложением и вторым и третьим выходами регистра строки, а информационный и адресный входы блока оперативной памяти подключены к выходам соответственно арифметического устройства и блока управления памятью.

К информационному входу - выходу машины может быть подключено устройство для ввода информации с магнитных карт и вывода информации на магнитные карты.

Недостатком известных вычислительных машин является значительное снижение их производительности за счет неполного использования производительности арифметического устройства при выполнении коротких операций.

Машина работает в асинхронном режиме, поэтому любая арифметическая операция выполняется за одинаковый промежуток времени, определяемый частотой поступления с магнитной карты информации одной рабочей ячейки, необходимой для выполнения одной вычислительной или логической операции

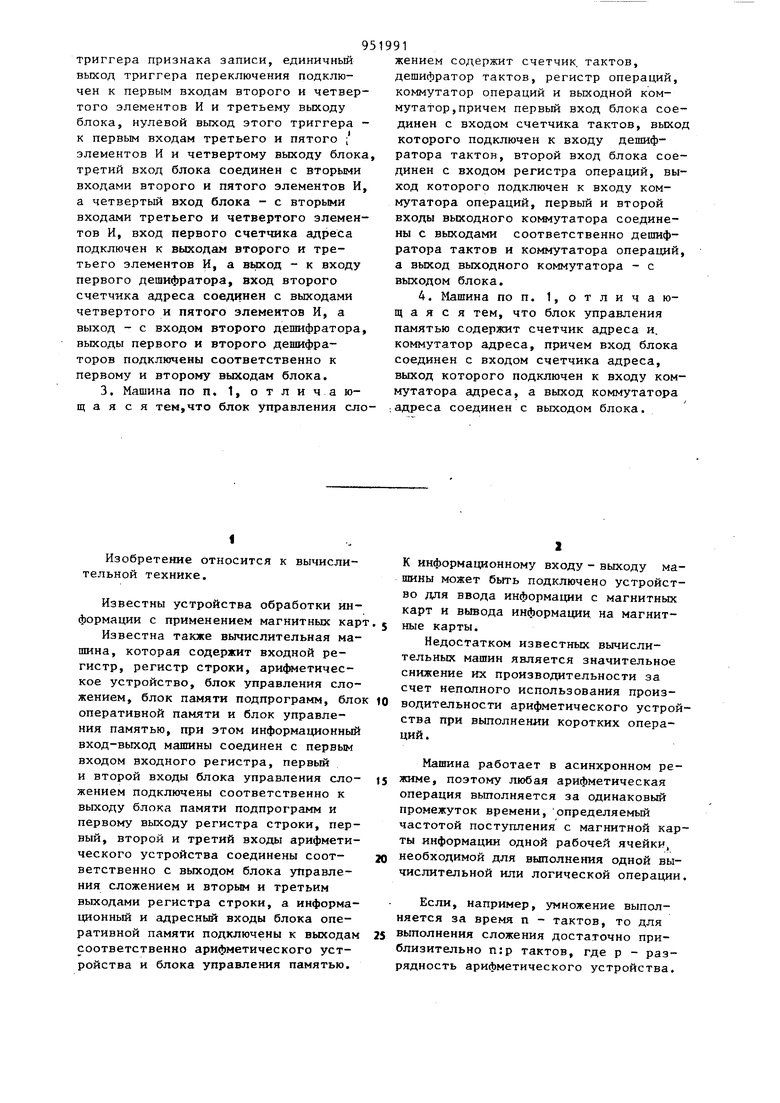

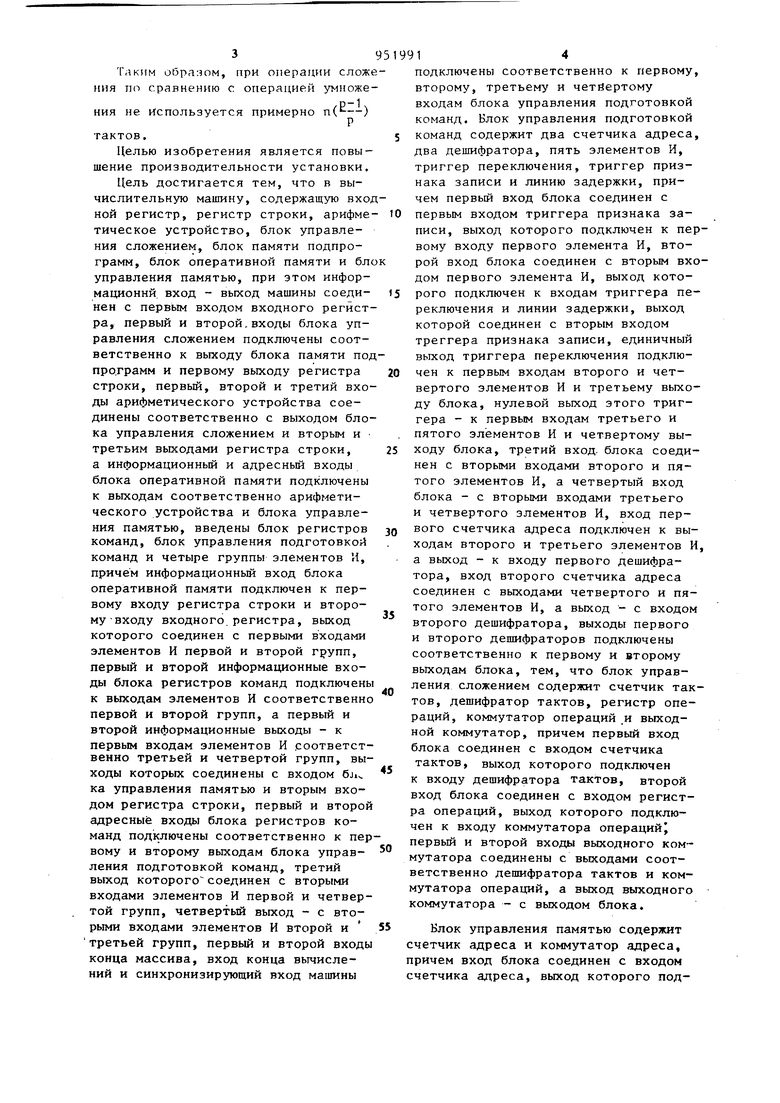

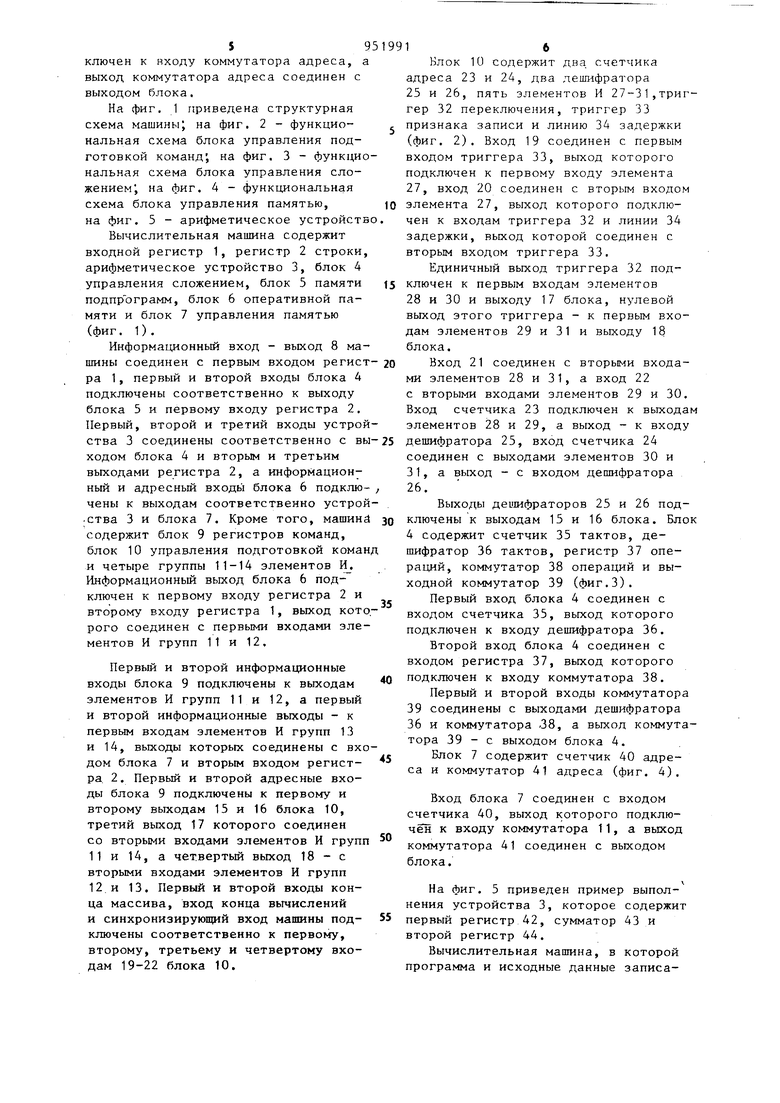

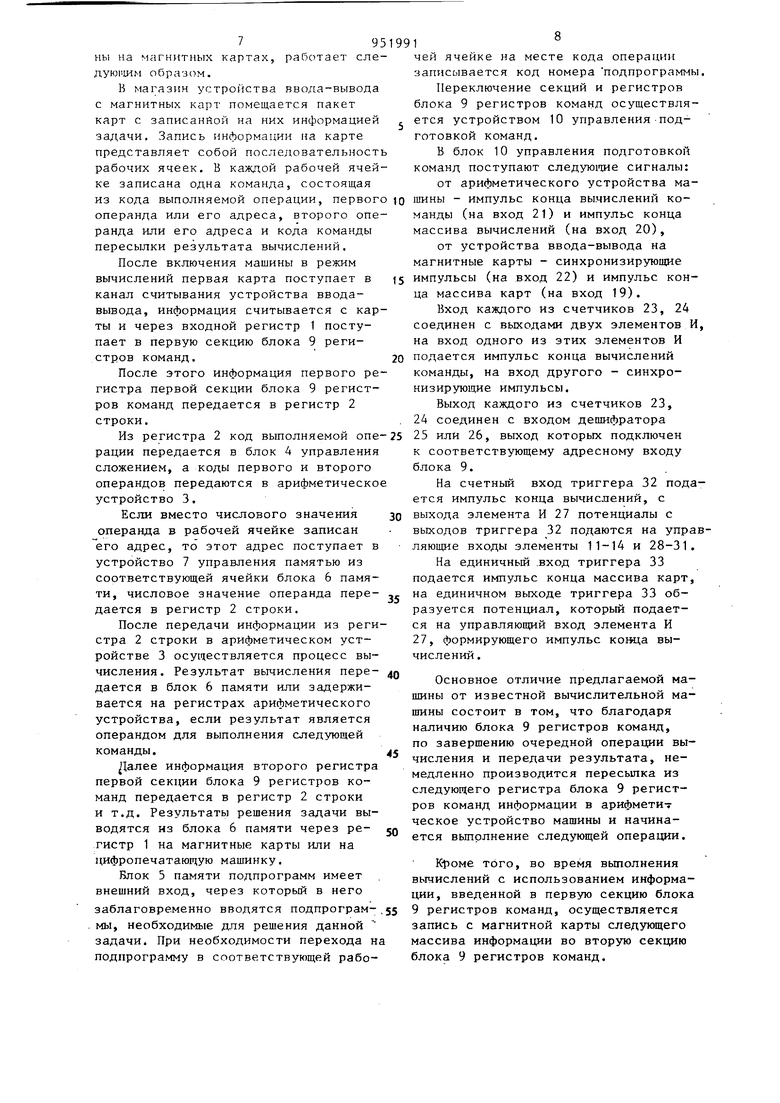

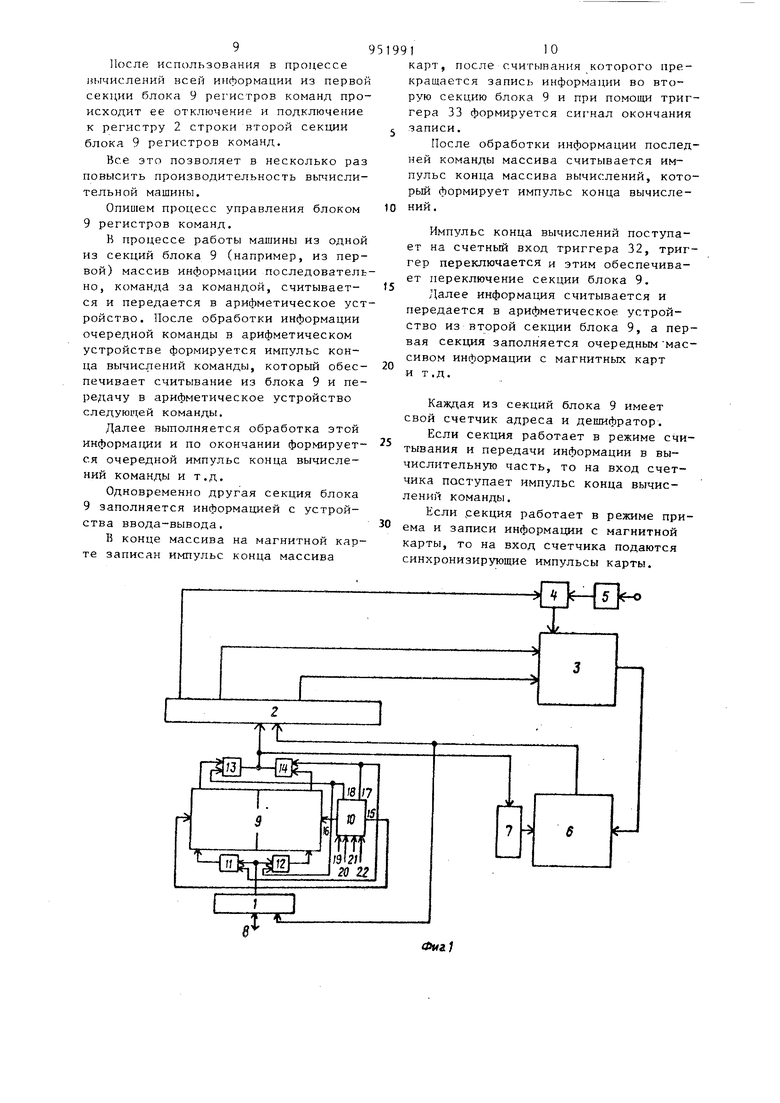

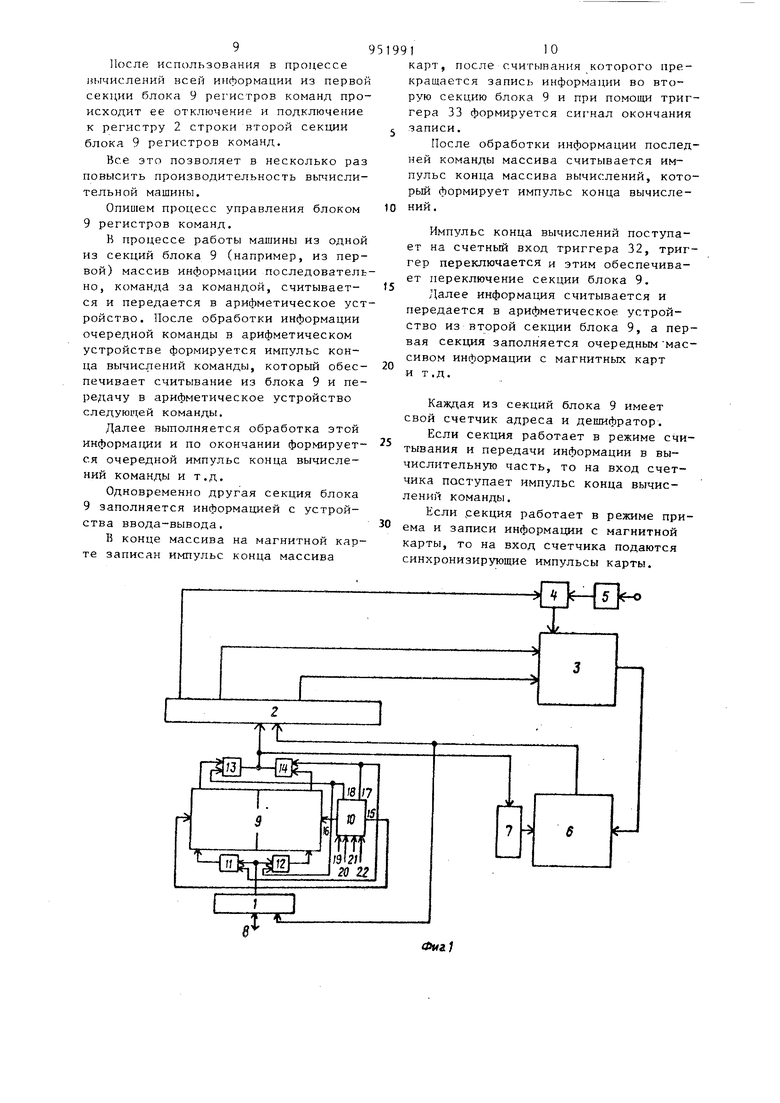

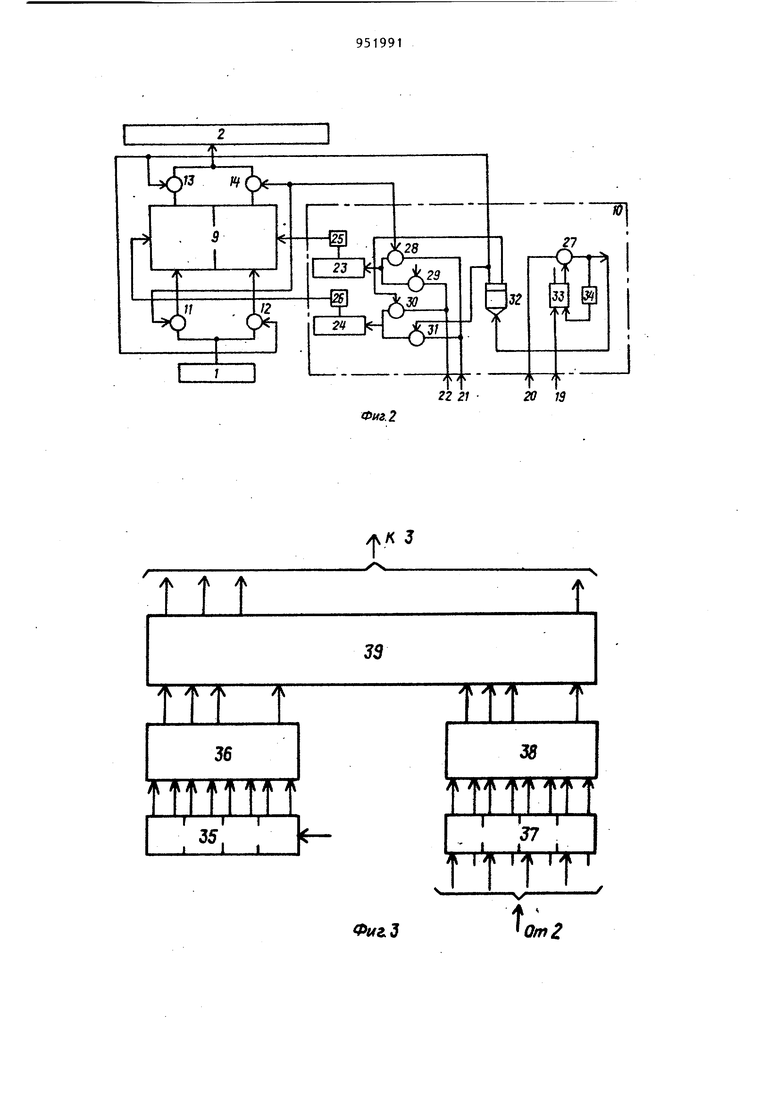

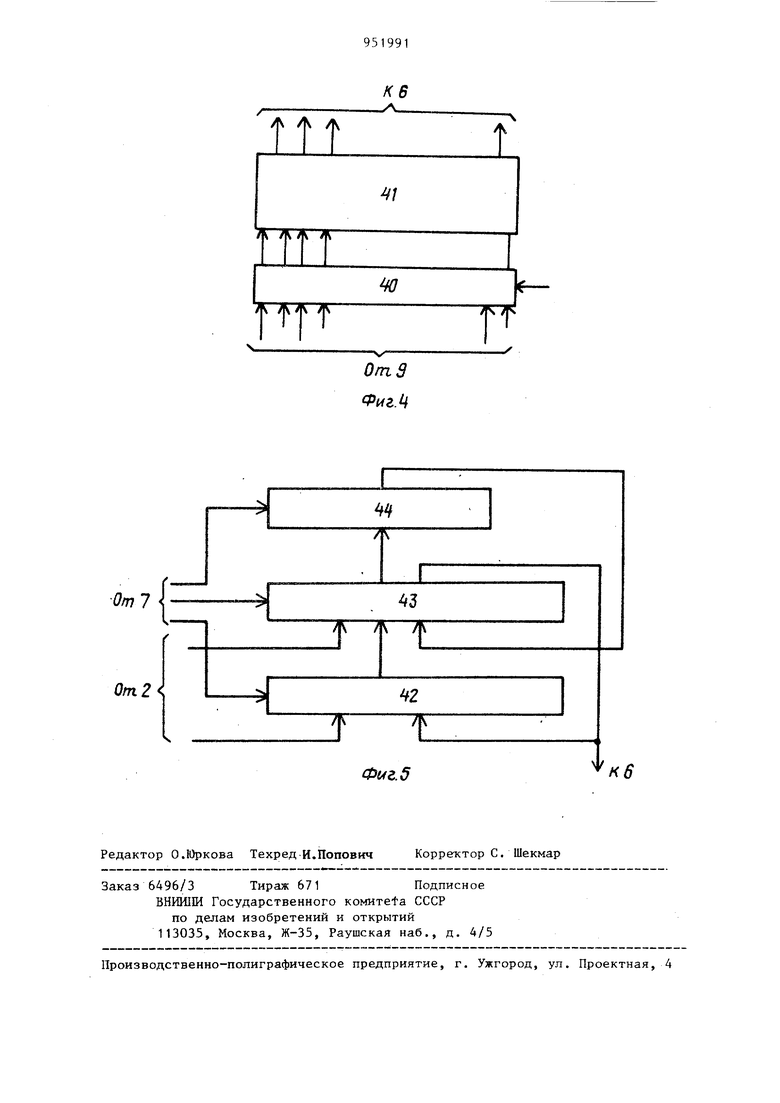

Если, например, умножение выполняется за время п - тактов, то для выполнения сложения достаточно приблизительно п:р тактов, где р - разрядность арифметического устройства. TriKHM обрл:эом, при операции слож ния по сравнению с операцией умноже ния не используется примерно ) тактов. Целью изобретения является повышение производительности установки. Цель достигается тем, что в вычислительную машину, содержащую вхо ной регистр, регистр строки, арифме тическое устройство, блок управления сложением, блок памяти подпрограмм, блок оперативной памяти и бл управления памятью, при этом информационнй. вход - выход машины соединен с первым входом входного регист ра, первый и второй.входы блока управления сложением подключены соответственно к выходу блока памяти под программ и первому выходу регистра строки, первый, второй и третий вхо ды арифметического устройства соединены соответственно с выходом бло ка управления сложением и вторым и третьим выходами регистра строки, а информационный и адресный входы блока оперативной памяти подключены к выходам соответственно арифметического устройства и блока управления памятью, введены блок регистров команд, блок управления подготовкой команд и четыре группы элементов И, причем информационный вход блока оперативной памяти подключен к первому входу регистра строки и второму-входу входного.регистра, выход которого соединен с первыми входами элементов И первой и второй , первый и второй информационные входы блока регистров команд подключены к выходам элементов И соответственно первой и второй групп, а первый и второй информационные выходы - к первым входам элементов И .соответственно третьей и четвертой групп, выходы которых соединены с входом 6ji,. ка управления памятью и вторым входом регистра строки, первый и второй адресные входы блока регистров команд подключены соответственно к пер вому и второму выходам блока управления подготовкой команд, третий выход которого соединен с вторыми входами элементов И первой и четвертой групп, четвертый выход - с вторыми входами элементов И второй и третьей групп, первый и второй входы конца массива, вход конца вычислений и синхронизирующий вход машины подключены соответственно к первому, второму, третьему и четвертому входам блока управления подготовкой команд. Блок управления подготовкой команд содержит два счетчика адреса, два дешифратора, пять элементов И, триггер переключения, триггер признака записи и линию задержки, причем первый вход блока соединен с первым входом триггера признака записи, выход которого подключен к первому входу первого элемента И, второй вход блока соединен с вторым входом первого элемента И, выход которого подключен к входам триггера переключения и линии задержки, выход которой соединен с вторым входом треггера признака записи, единичный выход триггера переключения подключен к первым входам второго и четвертого элементов И и третьему выходу блока, нулевой выход этого триггера - к первым входам третьего и пятого элементов И и четвертому выходу блока, третий вход, блока соединен с вторыми входами второго и пятого элементов И, а четвертый вход блока - с вторьми входами третьего и четвертого элементов И, вход первого счетчика адреса подключен к выходам второго и третьего элементов И, а выход - к входу первого дешифратора, вход второго счетчика адреса соединен с выходами четвертого и пятого элементов И, а выход - с входом второго дешифратора, выходы первого и второго дешифраторов подключены соответственно к первому и второму выходам блока, тем, что блок управления сложением содержит счетчик тактов, дешифратор тактов, регистр операций, коммутатор операций .и выходной коммутатор, причем первый вход блока соединен с входом счетчика тактов, выход которого подключен к входу дешифратора тактов, второй вход блока соединен с входом регистра операций, выход которого подключен к входу коммутатора операцийJ первый и второй входы выходного коммутатора соединены с выходами соответственно дешифратора тактов и коммутатора операций, а выход выходного коммутатора - с выходом блока. Блок управления памятью содержит четчик адреса и коммутатор адреса, ричем вход блока соединен с входом четчика адреса, выход которого подSключей к входу коммутатора адреса, выход коммутатора адреса соединен с выходом блока. На фиг. 1 приведена структурная схема машиныJ на фиг. 2 - функциональная схема блока управления подготовкой команд; на фиг. 3 - функци нальная схема блока управления сложением, на фиг. 4 - функциональная схема блока управления памятью, на фиг. 5 - арифметическое устройст Вычислительная машина содержит входной регистр 1, регистр 2 строки арифметическое устройство 3, блок 4 управления сложением, блок 5 памяти подпрограмм, блок 6 оперативной памяти и блок 7 управления памятью (фиг. 1). Информационный вход - выход 8 ма шины соединен с первым входом регис ра 1, первый и второй входы блока 4 подключены соответственно к выходу блока 5 и первому входу регистра 2. Первый, второй и третий входы устро ства 3 соединены соответственно с в ходом блока 4 и вторым и третьим выходами регистра 2, а информационный и адресный входы блока 6 подклю чены к выходам соответственно устро ства 3 и блока 7. Кроме того, машин содержит блок 9 регистров команд, блок 10 управления подготовкой кома и четыре группы 11-14 элементов И, Информационный выход блока 6 подключен к первому входу регистра 2 и второму входу регистра 1, выход кот рого соединен с первыми входами эле ментов И групп 11 и 12. Первый и второй информационные входы блока 9 подключены к выходам элементов И групп 11 и 12, а первый и второй информационные выходы - к первым входам элементов И групп 13 и 14, выходы которых соединены с вх дом блока 7 и вторым входом регистра 2. Первый и второй адресные входы блока 9 подключены к первому и второму выходам 15 и 16 блока 10, третий выход 17 которого соединен со вторыми входами элементов И груп 11и 14, а четвертый выход 18 - с вторыми входами элементов И групп 12и 13. Первый и второй входы конца массива, вход конца вычислений и синхронизирующий вход машины подключены соответственно к первому, второму, третьему и четвертому входам 19-22 блока 10. 16 Блок 10 содержит два счетчика адреса 23 и 24, два дешифратора 25 и 26, пять элементов И 27-31,триггер 32 переключения, триггер 33 признака записи и линию 34 задержки (фиг. 2). Вход 19 соединен с первым входом триггера 33, выход которого подключен к первому входу элемента 27, вход 20 соединен с вторым входом элемента 27, выход которого подключен к входам триггера 32 и линии 34 задержки, выход которой соединен с вторым входом триггера 33. Единичный выход триггера 32 подключен к первым входам элементов 28 и 30 и выходу 17 блока, нулевой выход этого триггера - к первым входам элементов 29 и 31 и выходу 18 блока. Вход 21 соединен с вторыми входами элементов 28 и 31, а вход 22 с вторыми входами элементов 29 и 30. Вход счетчика 23 подключен к выходам элементов 28 и 29, а выход - к входу дешифратора 25, вход счетчика 24 соединен с выходами элементов 30 и 31, а выход - с входом дешифратора 26. Выходы деишфраторов 25 и 26 подключены к выходам 15 и 16 блока. Блок 4 содержит счетчик 35 тактов, дешифратор 36 тактов, регистр 37 операций, коммутатор 38 операций и выходной коммутатор 39 (фиг.З). Первый вход блока 4 соединен с входом счетчика 35, выход которого подключен к входу дешифратора 36. Второй вход блока 4 соединен с входом регистра 37, выход которого подключен к входу коммутатора 38. Первый и второй входы коммутатора 39 соединены с выходами дешифратора 36 и коммутатора 38, а выход коммутатора 39 - с выходом блока 4. Блок 7 содержит счетчик 40 адреса и коммутатор 41 адреса (фиг. 4). Вход блока 7 соединен с входом счетчика 40, выход которого подключен к входу коммутатора 11, а выход коммутатора 41 соединен с выходом блока. На фиг. 5 приведен пример выполнения устройства 3, которое содержит первый регистр 42, сумматор 43 и второй регистр 44. Вычислительная машина, в которой программа и исходные данные эаписаработает елены на магнитных картах, дуюршм образом. В магазин устройства ввода-вывода с магнитных карт помещается пакет карт с записанйон на них информацией задачи. Запись информации на карте представляет собой последовательность рабочих ячеек. В каждой рабочей ячейке записана одна команда, состоящая из кода выполняемой операции, первого операнда или его адреса, второго операнда или его адреса и кода команды пересылки результата вычислений. После включения машины в режим вычислений первая карта поступает в канал считывания устройства вводавывода, информация считывается с карты и через входной регистр 1 поступает в первую секцию блока 9 регистров команд. После этого информация первого регистра первой секции блока 9 регистров команд передается в регистр 2 строки. Из регистра 2 код выполняемой one-25 25 или рации передается в блок 4 управлени сложением, а коды первого и второго операндов передаются в арифметическо устройство 3. Если вместо числового значения операнда в рабочей ячейке записан его адрес, то этот адрес поступает в устройство 7 управления памятью из соответствующей ячейки блока 6 памяти, числовое значение операнда передается в регистр 2 строки. После передачи информации из реги стра 2 строки в арифметическом устройстве 3 осуществляется процесс вычисления. Результат вычисления передается в блок 6 памяти или задерживается на регистрах арифметического устройства, если результат является операндом для выполнения следующей команды. 1алее информация второго регистра первой секции блока 9 регистров команд передается в регистр 2 строки и т.д. Результаты решения задачи выводятся из блока 6 памяти через регистр 1 на магнитные карты или на цифропечатающую мащинку. Блок 5 памяти подпрограмм имеет внешний вход, через который в него заблаговременно вводятся подпрограммы, необходимые для решения данной задачи. При необходимости перехода н подпрограмму в соответствующей рабо951° чей ячейке на месте кода операции записывается код номера подпрограммы. Переключение секций и регистров блока 9 регистров команд осуществляется устройством 10 управления-подготовкой команд. В блок 10 управления подготовкой команд поступают следукище сигналы: от арифметического устройства машины - импульс конца вычислений команды (на вход 21) и импульс конца массива вычислений (на вход 20), от устройства ввода-вывода на магнитные карты - синхронизирующие импульсы (на вход 22) и импульс конца массива карт (на вход 19). Вход каждого из счетчиков 23, 24 соединен с выходами двух элементов И, на вход одного из этих элементов И подается импульс конца вычислений команды, на вход другого - синхронизирующие импульсы. Выход каждого из счетчиков 23, 24 соединен с входом дешифратора 26, выход которых подключен к соответствующему адресному входу блока 9. На счетный вход триггера 32 подается импульс конца вычислений, с выхода элемента И 27 потенциалы с выходов триггера 32 подаются на управляющие входы элементы 11-14 и 28-31. На единичный .вход триггера 33 подается импульс конца массива карт, на единичном выходе триггера 33 образуется потенциал, который подается на управляющий вход элемента И 27, формирующего импульс ко1ща вычислений. Основное отличие предлагаемой машины от известной вычислительной машины состоит в том, что благодаря наличию блока 9 регистров команд, по завершению очередной операции вычисления и передачи результата, немедленно производится пересылка из следующего регистра блока 9 регистров команд информации в арифметическое устройство машины и начинается вьтрлнение следующей операции. Кроме того, во время вьтолнения вычислений с использованием информации, введенной в первую секцию блока 9 регистров команд, осуществляется запись с магнитной карты следующего массива информации во вторую секцию блока 9 регистров команд.

99

После использования в процессе иычнслений всей информации из первой секции блока 9 регистров команд происходит ее отключение и подключение к регистру 2 строки второй секции блока 9 регистров команд.

Все это позволяет в несколько раз повысить производительность вычислительной машины.

Опишем процесс управления блоком 9 регистров команд.

К процессе работы машины из одной из секций блока 9 (например, из первой) массив информации последовательно, командй за командой, считывается и передается в арифметическое устройство. После обработки информации очередной команды в арифметическом устройстве формируется импульс конца вычислений команды, который обеспечивает считывание из блока 9 и передачу в арифметическое устройство следующей команды.

Далее выполняется обработка этой информагщи и по окончании формируется очередной импульс конца вычислений команды и т.д.

Одновременно другая секция блока 9 заполняется информацией с устройства ввода-вывода.

В конце массива на магнитной карте записан импульс конца массива

110

карт, после считывания которого прекращается запись информации во вторую секцию блока 9 и при помо1ци триггера 33 формируется сигнал окончания записи.

После обработки информации последней команды массива считывается импульс конца массива вычислений, который формирует импульс конца вычислений.

Импульс конца вычислений поступает на счетный вход триггера 32, триггер переключается и этим обеспечивает переключение секции блока 9.

Далее информация считывается и передается в арифметическое устройство из второй секции блока 9, а первая секция заполняется очередным массивом информации с магнитных карт и т.д.

Каждая из секций блока 9 имеет свой счетчик адреса и дешифратор.

Если секция работает в режиме считывания и передачи информации в вычислительную часть, то на вход счетчика поступает импульс конца вычислений команды.

Если рекция работает в режиме приема и записи информации с магнитной карты, то на вход счетчика подаются синхронизирующие импульсы карты.

±1 t

/ /

56

Г1 Т Ф 1 т Т Т

г I Г

. 22 2120 13

и 3

И

3

А

J7

II

I Л I

V J

I

От2

ФигЗ

Om.2 ,

Кб

Ф(г.

Авторы

Даты

1986-11-23—Публикация

1980-11-24—Подача