(5Л) УСТРОЙСТВО для ПОРОГОВОГО ВЫДЕЛЕНИЯ КОДА m ИЗ п

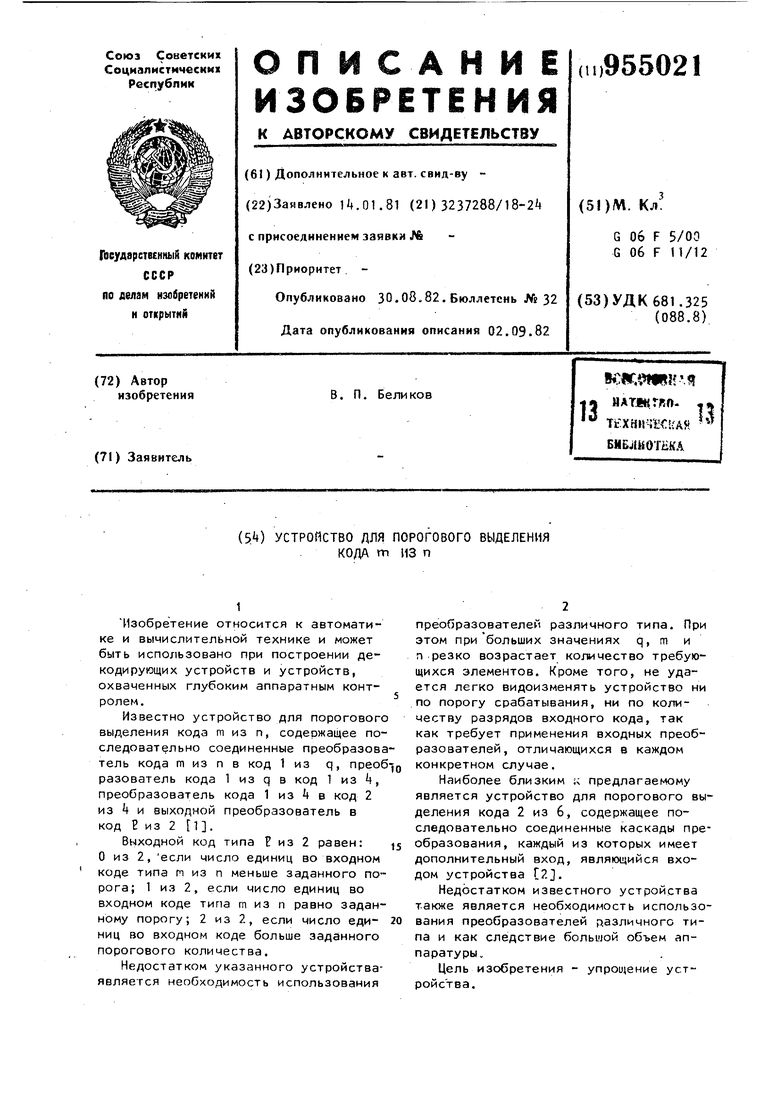

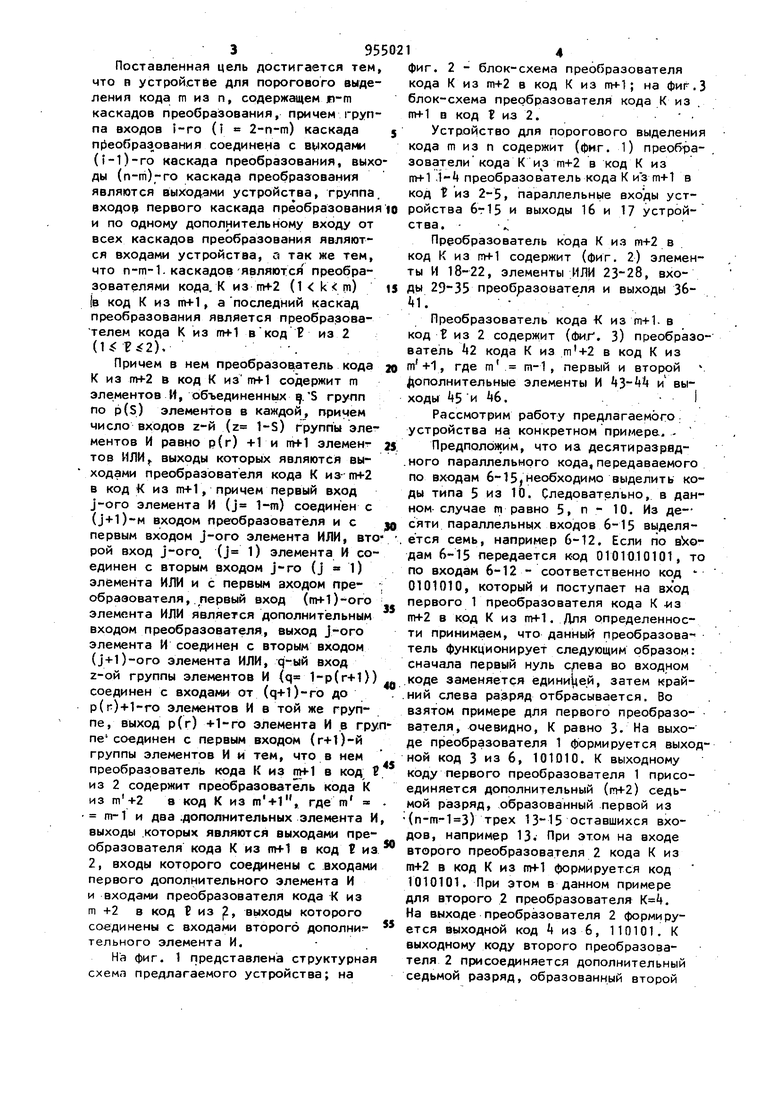

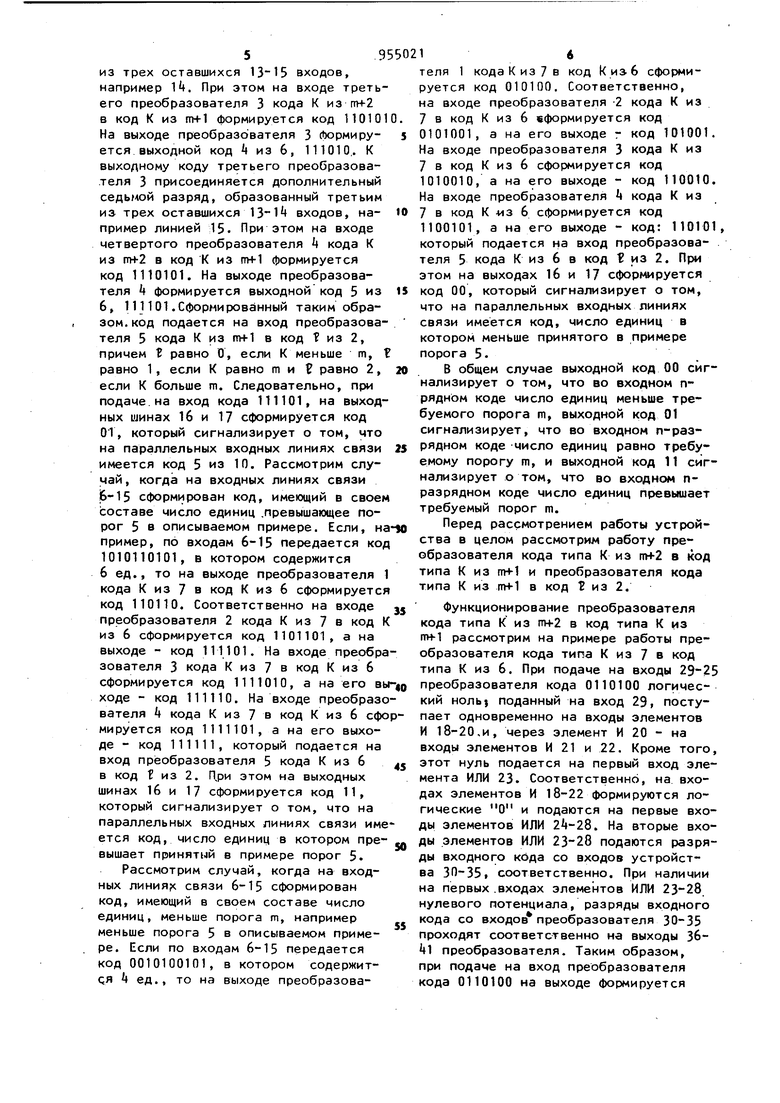

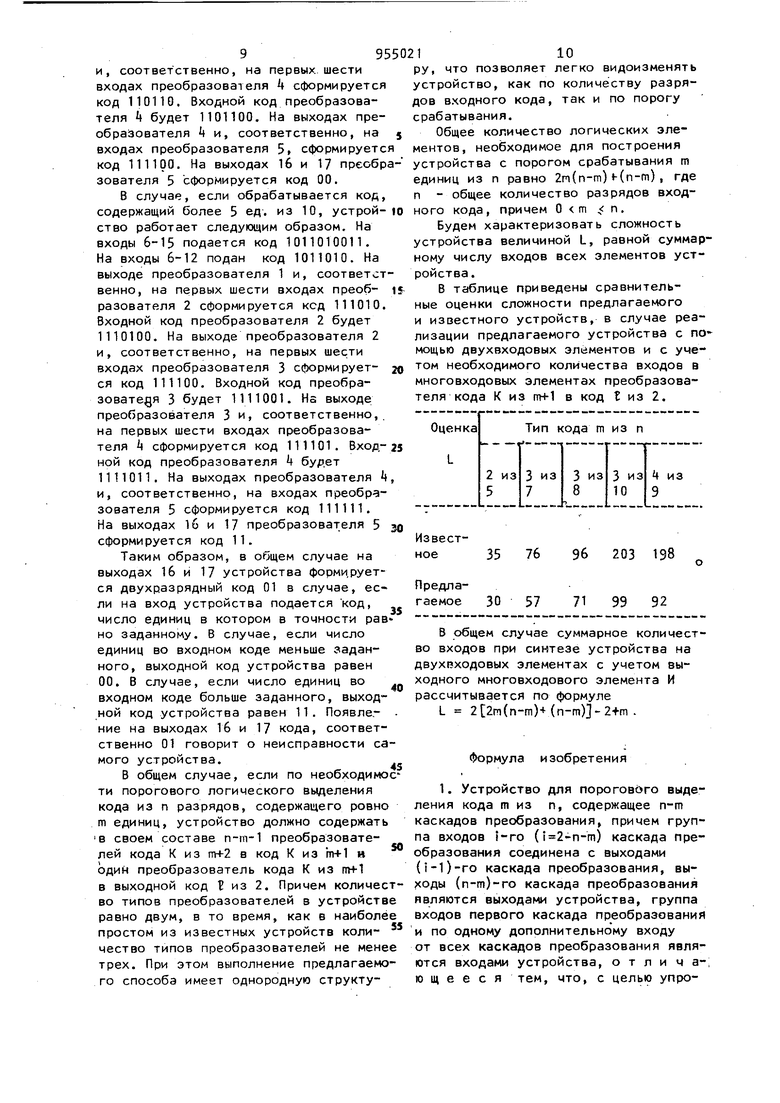

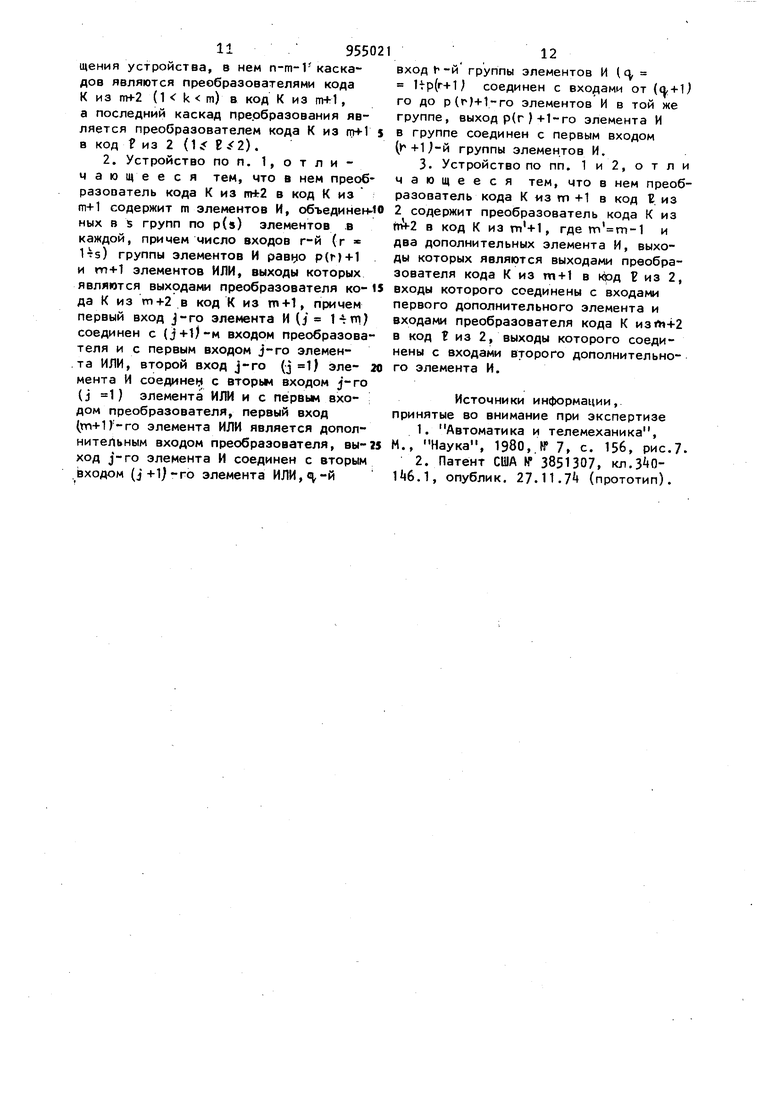

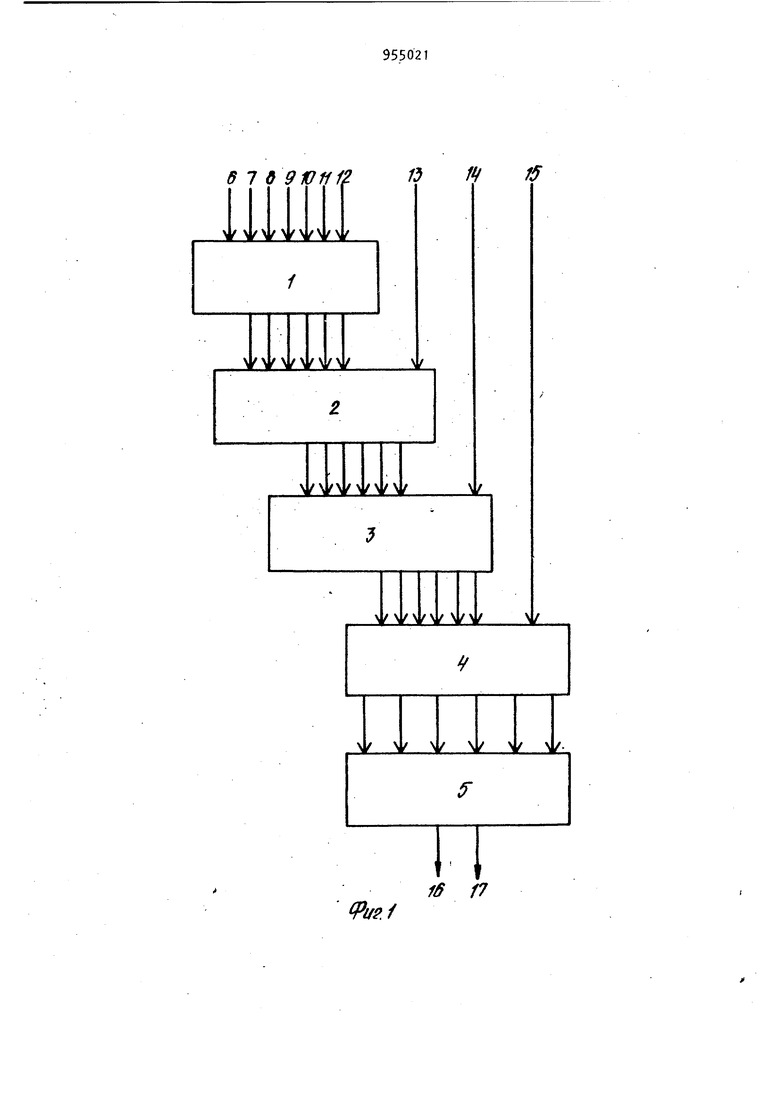

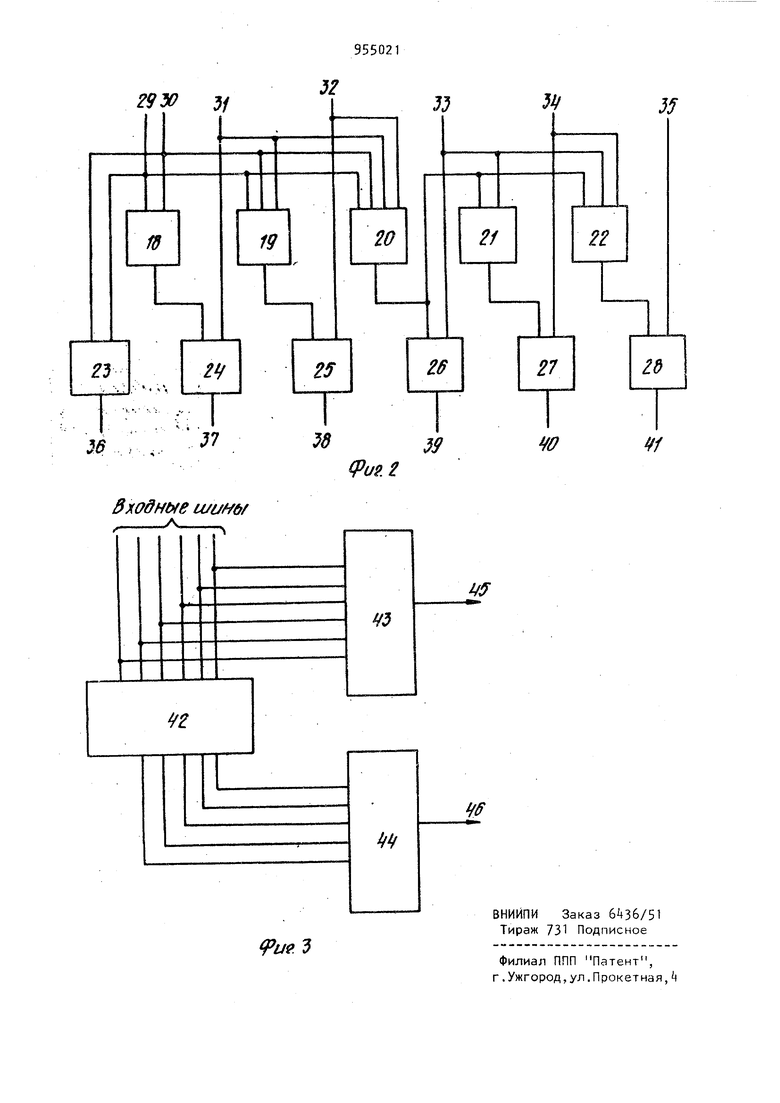

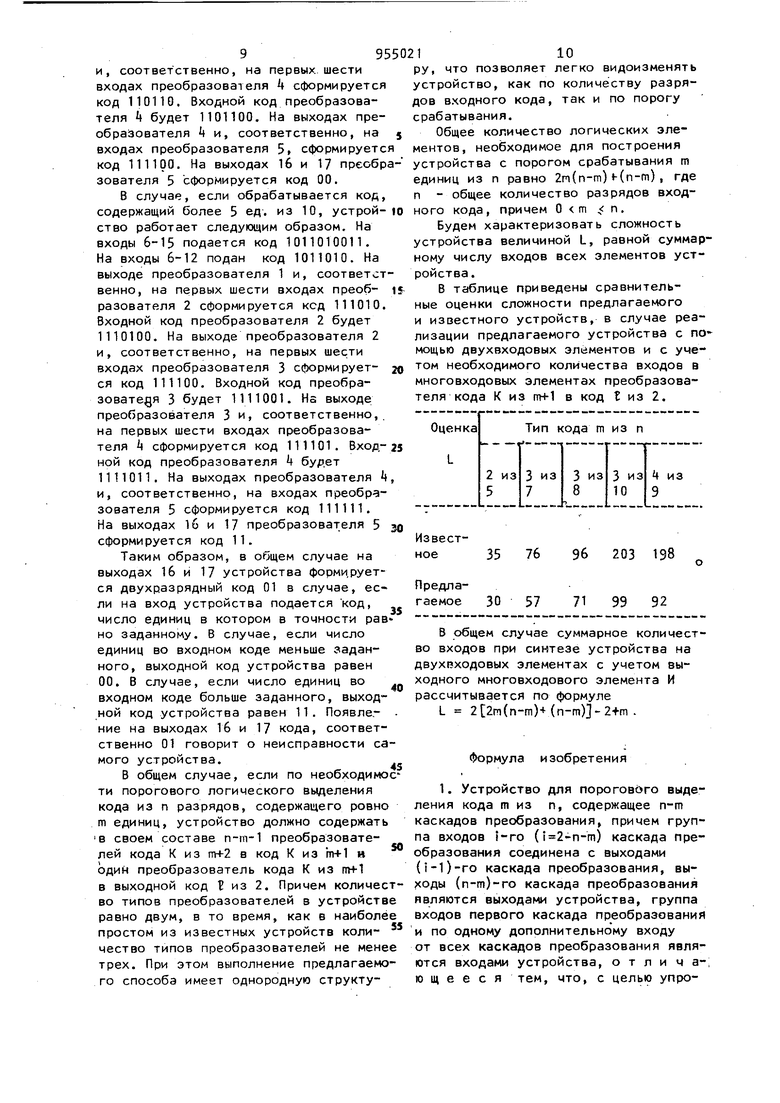

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении декодирующих устройств и устройств, охваченных глубоким аппаратным контролем. Известно устройство для порогового выделения кода m из п, содержащее последовательно соединенные преобразова тель кода m из п в код 1 из q, преоб разователь кода 1 из q в код 1 из 4, преобразователь кода 1 из Ц в код 2 из и выходной преобразователь в код В из 2 1. Выходной код типа Е из 2 равен: О из 2, если число единиц во входном коде типа гл из п меньше заданного порога; 1 из 2, если число единиц во входном коде типа m из п равно заданному порогу; 2 из 2, если число единиц во входном коде больше заданного порогового количества. Недостатком указанного устройстваявляется необходимость использования преобразователей различного типа. При этом прибольших значениях q, m и п резко возрастает количество требующихся элементов. Кроме того, не удается легко видоизменять устройство ни по порогу срабатывания, ни по количеству разрядов входного кода, так как требует применения входных преобразователей, отличающихся в каждом конкретном случае. Наиболее близким к предлагаемому является устройство для порогового выделения кода 2 из 6, содержащее последовательно соединенные каскады преобразования, каждый из которых имеет дополнительный вход, являющийся входом устройства .. Недостатком известного устройства также является необходимость использования преобразователей различного типа и как следствие большой объем аппаратуры. Цель изобретения - упрощение устройства. что R устройстве для порогового выделения кода m из п, содержащем я-m каскадов преобразования, причем группа входов i-ro (i 2-n-m) каскада преобразования соединена с вмходами (1-1)-го каскада преобразования, выхо ды (п-т)-го каскада преобразования являются выходами устройства, группа ВХОД09 первого каскада преобразования и по одному дополнительному входу от всех каскадов преобразования являются входами устройства, а так же тем, что n-m-1. каскадов Являются преобразователями кода. К из rrrt-2 () IB код К из т+1, а последний каскад преобразования является преобразователем кода К из т+1 вкод Е из 2 ( ).. Причем в нем преобразователь кода К из т+2 в код К из гтН-1 содержит m элементов И, объединенных g.S групп по p(S) элементов в каждой, причем число входов z-й (z- 1-S) группы элементов И равно р(г) +1 и т+1 элемен тов ИЛИ;,, выходы которых являются выходами преобразователя кода К из- т+2 в код К из т+1, причем первый вход j-oro элемента И (j l-m) соединен с (j+l)-M входом преобразователя и с первым входом J-oro элемента ИЛИ, вто рой вход j-oro. (j 1) элемента И соединен с вторым входом j-ro (j 1) элемента ИЛИ и с первым аходом преобразователя ,. первый вход (т+1)-ого элемента ИЛИ является дополнительным входом преобразователя, выход j-oro элемента И соединен с вторым входом (j+l)-oro элемента ИЛИ, q-ый вход 2-ой группы элементов И (q 1-р(г+1)) соединен с входами от (q+l)-ro до р(г)+1-го элементов И в той же группе, выход р(г) +1-ГО элемента И в гру пе соединен с первым входом (г+1)-й группы элементов И и тем, что в нем преобразователь кода К из гп+1 в код из 2 содержит преобразователь кода К из т+2 в код К из m+l, где m т-1 и два .дополнительных элемента И выходы .которых являются выходами преобразователя кода К из т+1 в код f из 2, входы которого соединены с входами первого дополнительного элемента И и входами преобразователя кода К из т+2 в код f из , выходы которого соединены с входами второго дополни тельного элемента И. На фиг. 1 представлена структурная схема предлагаемого устройства; на кода К из т+2 в код К из пн-1; на фиг. 3 блок-схема преобразователя кода К из im-1 в код из 2. Устройство для порогового выделения кода m из п содержит (фиг. 1) преобразователи кода К т+2 в код К из т+1 ,1- преобразователь кода К из m+l в код t из 2-5, параллельные входы устройства 6т15 и выходы 16 и 17 устройства, Преобразователь кода К из т+2 в код К из т+1 содержит (фиг, 2) элементы И 18-22, элементы ИЛИ 23-28, входы преобразователя и выходы . . Преобразователь кода -К из т+1. в код t из 2 содержит (фи.Г. 3) преобразователь 2 кода К из гп+2 в код К из т+1, где т . т-1, первый и второй дополнительные элементы И k} и выходы 45 и 6.-1 Рассмотрим работу предлагаемого устройства на конкретном примере. Предположим, что иа десятиразрядного параллельного кода,передаваемого по входам 6-15Jнеобходимо выделить коды типа 5 из 10. Следовательно, в данном случае m равно 5, п - 10. Из десяти параллельных входов 6-15 вь1деляется семь, например 6-12. Если по вводам 6-15 передается код 0101010101, то по входам 6-12 - соответственно код 0101010, который и поступает на вход первого 1 преобразователя кода К +13 т+2 в код К из т+1. Для определенности принимаем, что данный преобразователь функционирует следующим образом: сначала первый нуль во входном коде заменяется единицей, затем крайний слева разряд отбрасывается. Во взятом примере для первого преобразователя, очевидно, К равно 3. На выходе преобразователя 1 формируется выходной код 3 из 6, 101010. К выходному коду первого преобразователя 1 присоединяется дополнительный (т+2) седьмой разряд, образованный первой из (п-т-1 3) трех 13-15 оставшихся входов, например 13. При этом на входе второго преобразователя 2 кода К из т+2 в код К из пн-1 формируется код 1010101. При этом в данном примере для второго 2 преобразователя . На выходе преобразователя 2 форми руется выходной код k из 6, 110101. К выходному коду второго преобразователя 2 присоединяется дополнительный седьмой разряд, образованный второй 5.9 из трех оставшихся входов, например Т. При этом на входе треть его преобразователя 3 кода К из пн-2 в код К из пн-1 формируется код 11010 На выходе преобразователя 3 Лормируется выходной код из 6, 111010,. К выходному коду третьего преобразователя 3 присоединяется дополнительный седьмой разряд, образованный третьим из трех оставшихся 13 I входов, например линией 15. При этом на входе четвертого преобразователя Ц кода К из пн-2 в код К из гтн-1 формируется код 1110101. На выходе преобразователя Ц формируется выходной код 5 из 6, 111101.Сформированный таким образом, код подается на вход преобразова теля 5 кода К из т+1 в код f из 2, причем t равно О, если К меньше т, равно 1, если К равно m и равно 2, если К больше т. Следовательно, при подаче.на вход кода 111101, на выход ных шинах 16 и 17 сформируется код ОТ, который сигнализирует о том, что на параллельных входных линиях связи имеется код 5 из 10. Рассмотрим случай, когда на входных линиях связи iS-IS сформирован код, имеющий в свое составе число единиц .превышающее порог 5 в описываемом примере. Если, н пример, по входам 6-15 передается ко 1010110101, в котором содержится 6 ед., то на выходе преобразователя кода К из 7 в код К из 6 сформируетс код 110110. Соответственно на входе преобразователя 2 кода К из 7 в код из 6 сформируется код 1101101, а на выходе - код 111101. На входе преобр зователя 3 кода К из 7 в код К из 6 сформируется код 1111010, а на его в ходе - код 111110. На входе преобраз вателя Ц кода К из 7 в код К из 6 сф мируется код 1111101, а на его выходе - код 111111, который подается на вход преобразователя 5 кода К из 6 в код f из 2. При этом на выходных шинах 16 и 17 сформируется код 11, который сигнализирует о том, что на параллельных входных линиях связи им ется код, число единиц в котором пре вышает принятый в примере порог 5. Рассмотрим случай, когда на входных линия( связи 6-15 сформирован код, имеющий в своем составе число единиц, меньше порога т, например меньше порога 5 в описываемом примере. Если по входам 6-15 передается код 0010100101, в котором содержится i ед., то на выходе преобразова16теля 1 кода К из 7 в код К из. 6 сформируется код 010100. Соответственно, на входе преобразователя -2 кода К из 7 в код К из 6 «формируется код 0101001, а на его выходе г код 101001. На входе преобразователя 3 кода К из 7 в код К из 6 сформируется код 1010010, а на его выходе - код 110010. На входе преобразователя кода К из 7 в код К +13 6 сформируется код 1100101, а на его выходе - код: 110101, который подается на вход преобразователя 5 кода К из 6 в код f из 2. При этом на выходах 16 и 17 сформируется код 00, который сигнализирует о том, что на параллельных входных линиях связи имеется код, число единиц в котором меньше принятого в примере порога 5. В общем случае выходной код 00 сигнализирует о том, что во входном прядном коде число единиц меньше требуемого порога Р1, выходной код 01 сигнализирует, что во входном п-разрядном коде число единиц равно требуемому порогу т, и выходной код 11 си|- нализирует о том, что во входном празрядном коде число единиц превышает требуемый порог п. Перед рассмотрением работы устройства в целом рассмотрим работу преобразователя кода типа К из гтн-2 в код типа К из пН-1 и преобразователя кода типа К из ггН-1 в код 2 из 2. Функционирование преобразователя кода типа К из пн-2 в код типа К из гтн-1 рассмотрим на примере работы преобразователя кода типа К из 7 в код типа К из 6. При подаче на входы 29-25 преобразователя кода 0110100 логический НОЛЬ} поданный на вход 29, поступает одновременно на входы элементов И 18-20,и, через элемент И 20 - на входы элементов И 21 и 22. Кроме того, этот нуль подается на первый вход элемента ИЛИ 23. Соответственно, на входах элементов И 18-22 формируются логические О и подаются на первые входы элементов ИЛИ . На вторые входы элементов ИЛИ 23-28 подаются разряды входного кода со входов устройства 30-351 соответственно. При наличии на первых .входах элементов ИЛИ 23-28 нулевого потенциала, разряды входного кода со входов преобразователя 30-35 проходят соответственно на выходы 3641 преобразователя. Таким образом, при подаче на вход преобразователя кода 0110100 на выходе формируется код 110100. При подаче на входы 29-35 преобразователя, соответственно, кода 1110100, логический нуль, поданный на вход 32, поступает на вход элемента И 20 и через этот элемент на входы элементов И 21 и 22. Соответствегнно, на выходах элементов И 20-22 формируются логические О и подаются на первые входы элементов ИЛИ 2б-2й. При этом на первых входах элементов ИЛИ 2323 сформированы логические 1. При этом разряды входного кода со входов преобразователя 33-35 проходят соответственно на выходы . На выходах Зб-38, соответственно, сформированы логические 1, Таким образом при подаче на входы кода 1110100, на выходах , соответственно формируется код 111100, В общем случае число разрядов выходного кода на единицу меньше числа разрядов входного кода, а число единиц в выход ном коде равно числу единиц во входном коде, при условии, что количество единиц во входном коде меньше количества разрядов входного кода. В случае j. если все разряды входного кода содержат единицы, то число разрядов выходного кода на единицу меньше числа разрядов входного кода и все разряды выходного кода также содержат единицу. Функц онирование преобразователя кода типа К изт+1 в код из 2 рассмотрим на примере работы преЬбразова теля кода типа из 6 в код из 2. При подаче на входы кода 111111 на выходе блока-преобразователя 2 сформируется код 11111 . Соответственно на выходе элемента И 43 сформируется логическая 1. На выходе элемента И также сформируется логическая 1. Соответственно, на выходах k и сформируется двухразрядный код 2 из 2, а именно 11. При подаче на вхо ды кода 101111 на выходе блока-преобразователя 2 сформируется код 11111. Соответственно на выходе элемента И 3 сфогкиируется логический О.На выходе элемента И k сформируется логическая 1.На выходах 5 и 46 сформируется,соот ветственно,код типа 1 из 2,а именно, 01 При подаче на выходы кода 101011 на выходах 45 и 46 сформируется, соответственно, код О из 2, а именно 00. В общем случае при подаче на входные шины Преобразователя кода типа К из т+ в код Е из. 2 входного кода, содержащего количество единиц, превышающее порог m на выходных шинах сформируется код 2 из 2, т.е. 11, при подаче входного кода, содержащего точно m единиц сформируется код 1 из 2, а именно 01 , при подаче входного кода, содержащего количество единиц, меньшее порога т,сформируется код О из 2, т.е. 00. Код 10, соответственно, на выходах 45 и 46 сформируется только в результате отказа преобразователя, что облегчает контроль правильности его функционирования. На фиг. 1 дана структурная схема предлагаемого устройства, имеющего порог срабатывания 5 ед. из 10. Работу предлагаемого устройства рассмотрим на примере обработки кодов, содержащих ровно 5 ед. из 10, менее 5 ед. из 10 и более 5 ед. из 10. В случае, если отрабатывается код, содержащий точно 5 ед. из 10, устройство работает следующим образом. На входы 6-15 соответственно, подается, например код 0010010111. На входах 6-12, являющихся одновременно входами преобразователя 1 подан, соответственно, код 0010010. На выходе преобразователя 1 и, соответственно, первых шести входах преобразователя 2 .сформируется код 010010. Входной код преобразователя 2 будет 0100101. На выходе преобразователя 2 и на первых шести входах преобразователя 3 сформируется код 100101. Входной код преобразователя 3 будет 100111. На выходе преобразователя З-и,- соответственно, на первых шести входах преобразователя 4 сформируется код 101011. Входной код преобразователя 4 будет 1010111. На выходах преобразователя 4 и, соответственно, на входах преобразователя 5, сформируется код 110111. На выходах 16 и 17 преобразователя 5 сформируется код 01. В случае если обрабатывается код, Содержащий менее 5 единиц из 10, ycTf ройство работает следующим образом. На входы 6-15 соответственно, подается код 0100101100. На входы 6-12 подан код 0100101. На выходе преобразователя 1 и, соответственно, на первых шести входах преобразователя 2 сформируется код 100101. Входной код преобразователя 2 будет 1001011. На выходе преобразователя 2 и, соответственно, на первых шести входах преобразователя 3 сформируется код 101011. Входной код преобразователя 3 будет 1010110. На выходе преобразователя 3 и, соответственно, на первых, шести входах преобразователя 4 сформируется код 110110. Входной код преобразователя j будет 1101100. На выходах преобра;зователя Ц и, соответственно, на входах преобразователя 5 сформируетс код 111100. На выходах 1б и 17 преобр зователя 5 сформируется код 00. В случае, если обрабатывается код, содержащий более 5 ед. из 10, устройство работает следующим образом. На входы 6-15 подается код 1011010011. На входы 6-12 подан код 1011010. На выходе преобразователя 1 и, соответст венно, на первых шести входах преобразователя 2 сформируется кед 111010. Входной код преобразователя 2 будет 1110100. На выходе преобразователя 2 и, соответственно, на первых шести входах преобразователя 3 сформируется код 111100. Входной код преобразовате я 3 будет 1111001. Нз выходе преобразователя 3 и, соответственно,, на первых шести входах преобразователя k сформируется код 111101. Входной код преобразователя будет 1111011. На выходах преобразователя Ц и, соответственно, на входах преобразователя 5 сформируется код 111111. На выходах 1б и 17 преобразователя 5 сформируется код 11. Таким образом, в общем случае на выходах 16 ki 17 устройства форми.руется двухразрядный код 01 в случае, если на вход устройства подается код, число единиц в котором в точности рав но заданному. В случае, если число единиц во входном коде меньше заданного, выходной код устройства равен 00. В случае, если число единиц во входном коде больше заданного, выходной код устройства равен 11. Появле,ние на выходах 16 и 17 кода, соответственно 01 говорит о неисправности са мого устройства. В общем случае, если по необходимо ти порогового логического выделения кода из п разрядов, содержащего ровно m единиц, устройство должно содержать В своем составе п-ш-1 преобразователей кода К из гтн-2 в код К из пН-1 и один преобразователь кода К из nrfl в выходной код из 2. Причем количес во типов преобразователей в устройств равно двум, в то время, как в наиболе простом из известных устройств количество типов преобразователей не мене трех. При этом выполнение предлагаемо го способа имеет однородную структуру, что позволяет легко видоизменять устройство, как по количеству разрядов входного кода, так и по порогу срабатывания. Общее количество логических элементов, необходимое для построения устройства с порогом срабатывания m единиц из п равно 2rn(n-m) f(n-m) , где п - общее количество разрядов входного кода, причем О m п. Будем характеризовать сложность устройства величиной L, равной суммарному числу входов всех элементов устройства. В таблице приведены сравнительные оценки сложности предлагаемого и известного устройств, в случае реализации предлагаемого устройства с по мощью двухвходовых элементов и с учетом необходимого количества входов в многовходовых элементах преобразователя кода К из пН-1 в код t из 2. Известное 35 76 96 203 198 Предлагаемое 30 57 71 99 92 В общем случае суммарное количество входов при синтезе устройства на двухвходовых элементах с учетом выходного многовходового элемента И рассчитывается по формуле L (n-m)- (n-m)-2-fm . Формула изобретения 1. Устройство для порогового выделения кода m из п, содержащее n-m каскадов преобразования, примем группа входов 1-го (i 2-n-m) каскада преобразования соединена с выходами {i-1)-ro каскада преобразования, выходы (п-т)-го каскада преобразования являются выходами устройства, группа входов первого каскада преобразования и по одному дополнительному входу от всех каскадов преобразования являются входами устройства, о т л и ч а-; ю щ е е с я тем, что, с целью упро11955021

щения устройства, в нем n-m-V каскадов являются преобразователями кода К из nrt-2 (1 k m) в код К из пН-1, а последний каскад преобразования является преобразователем кода К из пт+Г s в код из 2 (1 ).

12

вход -и группы элементов И (с Hp(r+1j соединен с входами от ( + ) го до p( элементов И в той же группе, выход р(г ) 4-1-го элемента И в группе соединен с первым входом ( группы элементов И.

Источники информации, принятые во внимание при экспертизе

д1д9ЮИ121 f

(

(

.

(.

И

16 /7

1/2. f

J7

djy

J .

Входные u/L/ff6f

W

1

fPu.Z

Авторы

Даты

1982-08-30—Публикация

1981-01-14—Подача