(54) УСТРОЙСТВО ПРИОРИТЕТНОГО ПРЕРЫВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство приоритетного прерывания для микро-ЭВМ | 1982 |

|

SU1113803A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1984 |

|

SU1226479A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

1

Изобретение относится к вычислительной технике и может бь1ть использовано для реализации систем прерывания цифровых вычислительных машин (ЦВМ).

Известен блок приоритетного прерывания (БПП), содержащий регистр прерывания, регистр маски и элементы И 1.

Недостаток блока - большие аппаратурные затраты.

Наиболее близким к предлагаемому яв: ляется устройство, содержащее два модуля приоритетного прерывания 2.

Недостатком известного устройства являются большие аппаратурные затраты, связанные с тем, что вместо одного из ЭМПП используется многорежимный буферный регистр.

Цель изобретения - сокращение аппаратурных затрат за счет уменьшения числа используемых ЭМПП и организации новых связей внутри блока приоритетного прерывания.

Поставленная цель достигается тем, что в устройство приоритетного прерывания, содержащее первый и второй модули приоритетного прерывания, причем входы синхронизации, разрешения записи текущего

состояния, разрешения прерывания, разрешения считывания, выходы сигнала прерывания устройства соединены соответственно со входами синхронизации, разрешения записи текущего состояния, разрешения

прерывания, разрешения считывания и выходами сигналов прерывания первого и второго модулей приоритетного прерывания, введены дешифратор, первая и вторая группы и п элементов ИЛИ (где п - число запросов) и группа из п блоков элементов И, причем группа входов дешифратора соединена с группой выходов кода адреса устройства и с группой выходов первого модуля приоритетного прерывания, выходы элементов ИЛИ первой группы соединены с группой

15 входов первого модуля приоритетного прерывания, выходы блоков элементов И группы соединены со входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с группой входов второго

20 модуля приоритетного прерывания, группа выходов дещифратора соединена с первыми группами входов блоков элементов И группы, группы входов запросов прерывания устройства соединены со вторыми группами входов соответствующих блоков элементов И группы и группами входов соответствующих элементов ИЛИ первой группы, вход выборки приоритета устройства соединен со входом выборки приоритета первого модуля приоритетного преры вания, первая и вторая группы входов текущего состояния устройства соединены с группами входов текущего состояния первого и второго модулей приоритетного прерывания, вход дешифратора соединен с выходами сигнала прерывания первого модуля приоритетного прерывания и устройства.

Модуль приоритетного прерывания содержит регистр запросов, регистр текущего состояния, триггер блокировки, триггер прерывания, узел приоритета, группу элементов И и элементы И и ИЛИ, причем группа входов запросов прерывания модуля соединена с группой входов регистра запросов, вход которого соединен со входом триггера блокировки и первым входом первого элемента И, второй и третий входы которого соединены соответственно со входом разрещения прерывания модуля и выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами узла приоритета и регистра текущего состояния, группа входов и группа выходов которого соединены соответственно с группой входов текущего состояния модуля и первой группой входов узла приоритета, вторая группа входов которого соединена с группой выходов регистра запросов и первыми входами элементов И группы, вторые входы и выходы которых соединены соответственно с выходом второго элемента И и группой выходов модуля, первый вход второго элемента И соединен со входом разрешения считывания модуля, второй вход второго элемента И соединен с выходом регистра запросов и четвертым входом первого элемента И, выход которого соединен с первым входом триггера прерывания, второй вход которого соединен со входом синхронизации модуля, выход триггера прерывания соединен с выходом сигнала прерывания модуля и первым входом триггера блокировки, второй вход которого соединен с первым входом регистра текущего состояния и входом разрешения записи модуля, второй вход регистра текущего состояния, соединен со входом выборки приоритета модуля.

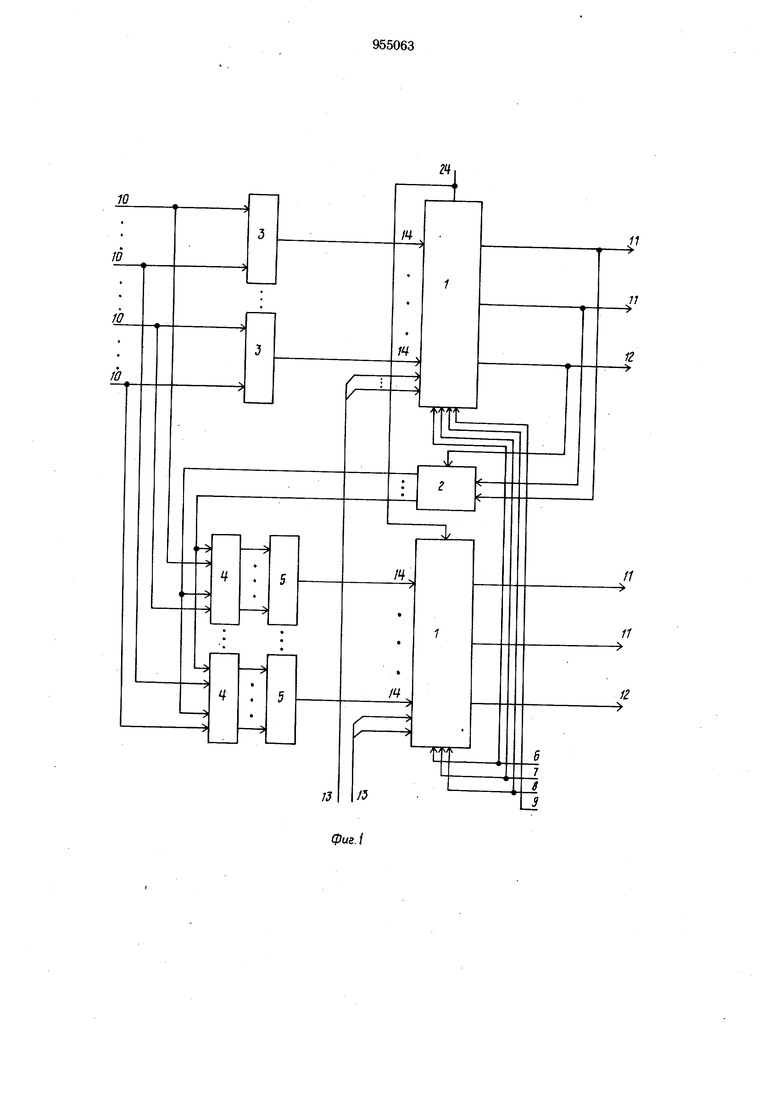

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема модуля приоритетного прерывания; на фиг. 3 - блок-схема узла приоритетного прерывания.

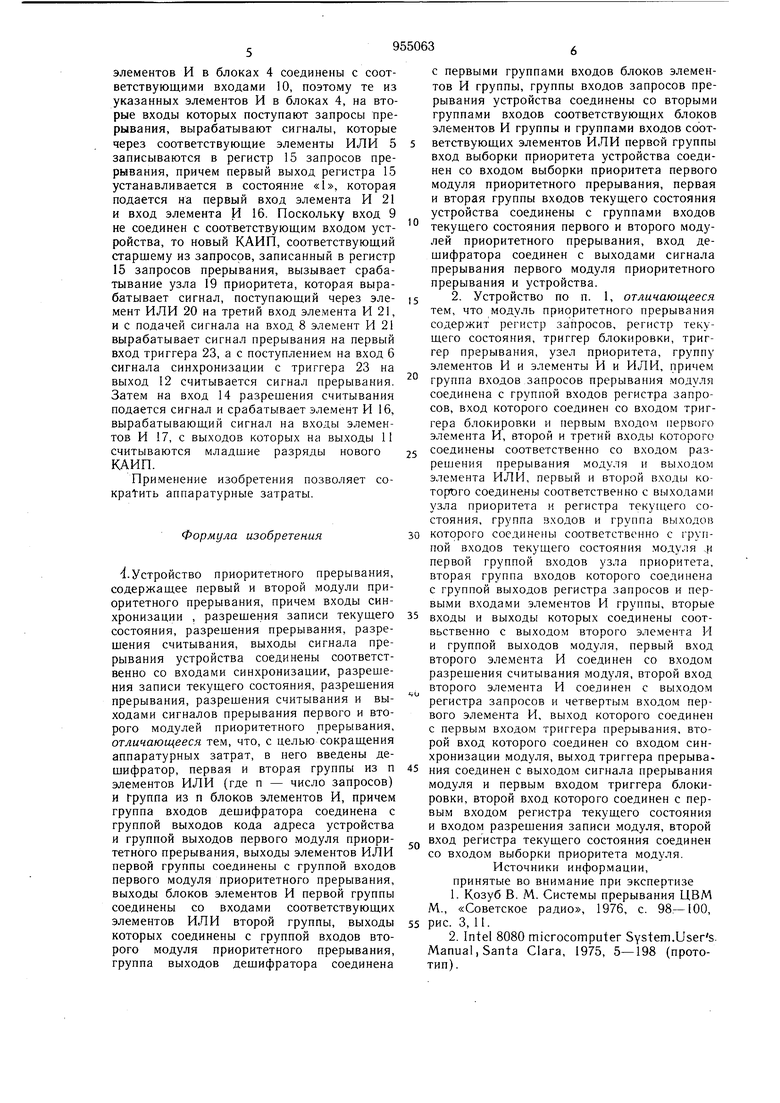

Устройство (фиг. 1) содержит модуль 1 приоритетного прерывания, дешифратор 2, группу элементов ИЛИ 3, блоки элементов И 4, группу элементов ИЛИ 5, вход 6 синхронизации устройства, вход 7 разрешения записи устройства, вход 8 разрешения прерывания устройства, вход 9 выборки приоритета устройства, группы входов 10 запросов прерывания устройства, группа

выходов 11 кода адреса устройства, выход 12 прерывания устройства, группы входов 13 текущего состояния устройства и вход 14 разрешения считывания устройства.

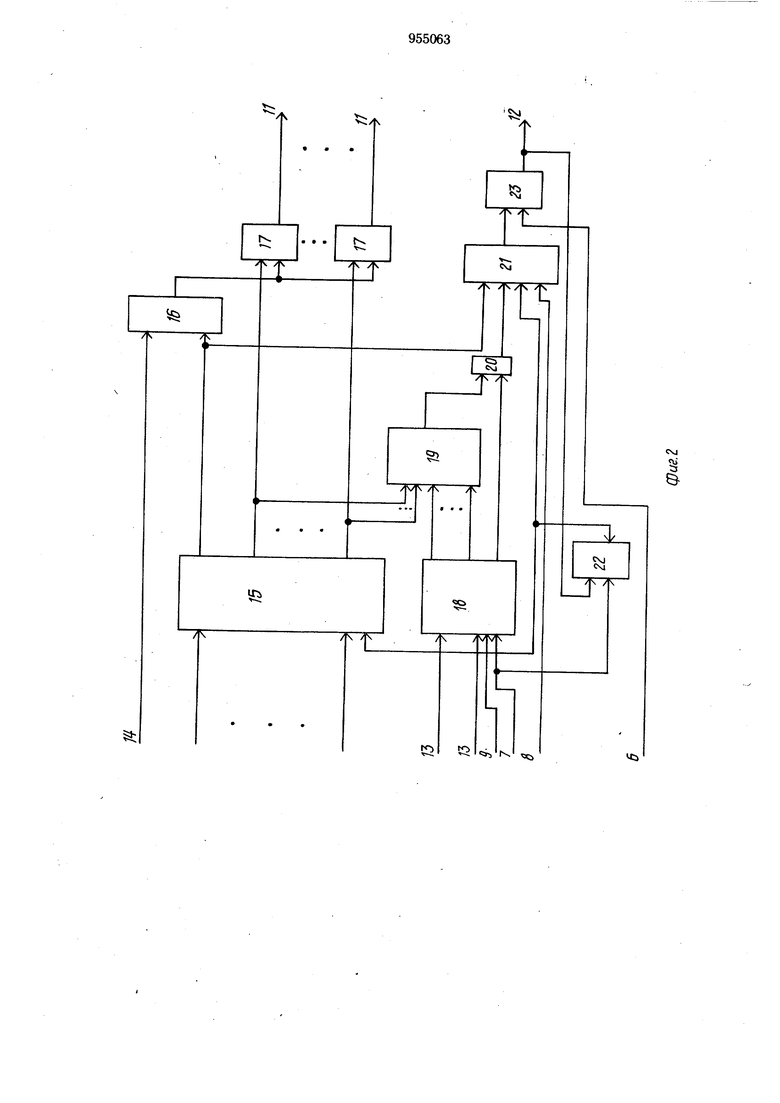

Модуль приоритетного прерывания

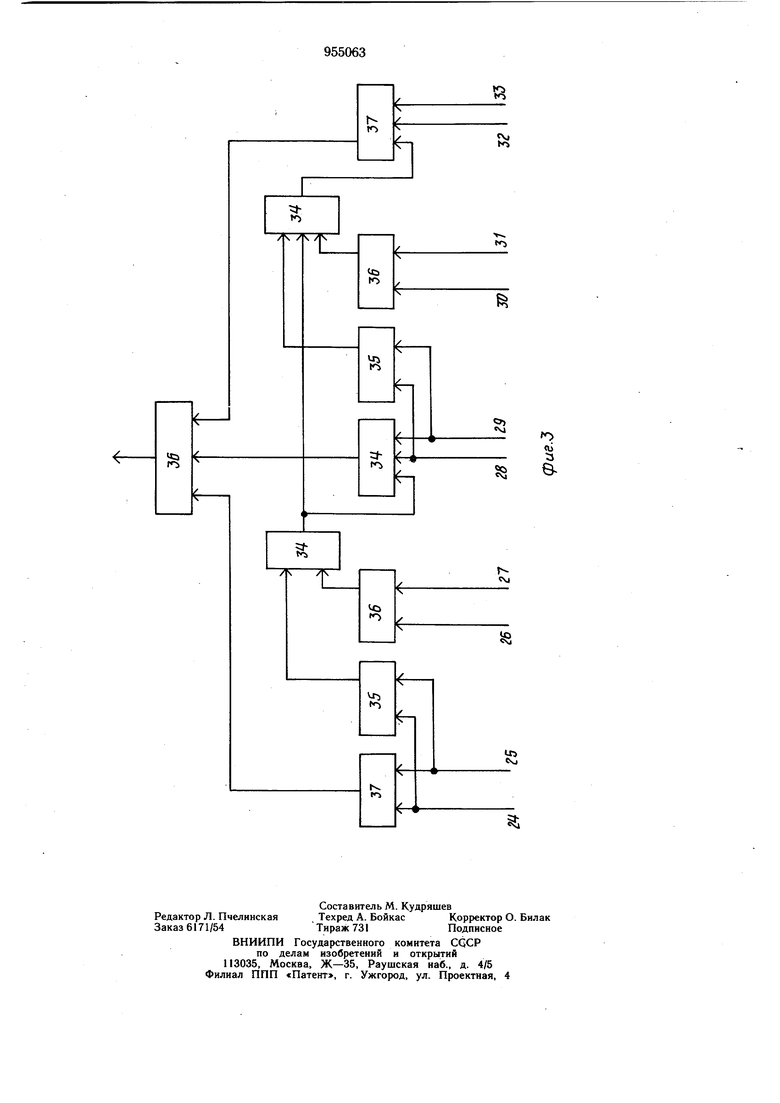

(фиг. 2) содержит регистр 15 запросов, элемент И 16, группу элементов И 17, регистр 18 текущего состояния, узел 19 приоритета, элемент ИЛИ 20, элемент И 21, триггер 22 блокировки прерывания, триггер 23 прерывания. Узел приоритета (фиг. 3) содержит входы 24-33, элементы И 34, элементы ИЛИ 35, элементы И 36 и 37.

Предлагаемое устройство работает следующим образом.

По сигналу, подаваемому на вход модуля 1, в триггеры 22 записываются «1, которые далее считываются на вторые входы элементов И 21, а также на соответствующие входы регистров 15, блокируя в них возможные записи новых запросов прерываний. При этом по входам 13 в регистры 18 состояния осуществляется запись соответственно старших и младших разрядов кода адреса источника прерывания (КАИП), запрос которого обрабатывается в текущий момент, и сигнал разрешения записи теку5 ш,его состояния со входа 7 снимается.

Сигналы от источников прерывания, если они имеют место, поступают по входам 10 на входы элементов ИЛИ 3, объединяясь в которых они поступают далее по соответствующим входам в регистр 15, причем

° первый выход регистра 15 устанавливается в состояние «1, которая подается на первый вход элемента И 21 и второй вход элемента И 16. Со вторых выходов регистра 15 считываются старшие разряды КАИП, которые соответствуют коду адреса старшего из поступивших в регистр 15 запросов прерывания, и поступают на первые входы узла 19, на вторые входы которого поступают из регистра 18 хранящиеся в нем старшие разряды текущего КАИП. По входу 9 постоянно

0 подается сигнал выборки приоритета, поэтому узел 19 вырабатывает сигнал, если новый КАИП больше текущего КАИП, который через элемент ИЛИ 20 поступает на третий вход элемента И 21, и с подачей сигнала на вход 8 элемент И 21 вырабатывает сигнал прерывания на первый вход триггера 23, а с поступлением на вход 6 сигнала синхронизации с триггера 23 считывается сигнал прерывания. Затем на вход 14 подается сигнал и срабатывает элемент И 16,

0 вырабатывающий сигнал на входы элементов И 17, с выходов которых на входы 11 считываются старщие разряды нового КАИП, которые вместе с сигналом прерывания поступают также на входы дешифратора 2, который срабатывает и открывает первые

5 входы тех элементов И в блоках 4, номера которых соответствуют номеру старшей группы запросов прерывания, содержащей хотя бы один запрос. Вторые входы указанных элементов И в блоках 4 соединены с соответствующими входами 10, поэтому те из указанных элементов И в блоках 4, на вторые входы которых поступают запросы прерывания, вырабатывают сигналы, которые через соответствующие элементы ИЛИ 5 записываются в регистр 15 запросов прерывания, причем первый выход регистра 15 устанавливается в состояние «1, которая подается на первый вход элемента И 21 и вход элемента И 16. Поскольку вход 9 не соединен с соответствующим входом устройства, то новый КАИП, соответствующий старщему из запросов, записанный в регистр 15 запросов прерывания, вызывает срабатывание узла 19 приоритета, которая вырабатывает сигнал, поступающий через элемент ИЛИ 20 на третий вход элемента И 21, и с подачей сигнала на вход 8 элемент И 21 вырабатывает сигнал прерывания на первый вход триггера 23, а с поступлением на вход 6 сигнала синхронизации с триггера 23 на выход 12 считывается сигнал прерывания. Затем на вход 14 разрешения считывания подается сигнал и срабатывает элемент И 16, вырабатывающий сигнал на входы элементов И 17, с выходов которых на выходы 11 считываются младшие разряды нового КАИП. Применение изобретения позволяет соKpatHTb аппаратурные затраты. Формула изобретения .Устройство приоритетного прерывания, содержащее первый и второй модули приоритетного прерывания, причем входы синхронизации , разрешения записи текущего состояния, разрешения прерывания, разрешения считывания, выходы сигнала прерывания устройства соединены соответственно со входами синхронизации, разрешения записи текущего состояния, разрешения прерывания, разрешения считывания и выходами сигналов прерывания первого и второго модулей приоритетного прерывания, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены дещифратор, первая и вторая группы из п элементов ИЛИ (где п - число запросов) и Группа из п блоков элементов И, причем группа входов дешифратора соединена с группой выходов кода адреса устройства и группой выходов первого модуля приоритетного прерывания, выходы элементов ИЛИ первой группы соединены с группой входов первого модуля приоритетного прерывания, выходы блоков элементов И первой группы соединены со входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с группой входов второго модуля приоритетного прерывания, группа выходов дешифратора соединена с первыми группами входов блоков элементов И группы, группы входов запросов прерывания устройства соединены со вторыми группами входов соответствующих блоков элементов И группы и группами входов соответствующих элементов ИЛИ первой группы вход выборки приоритета устройства соединен со входом выборки приоритета первого модуля приоритетного прерывания, первая и вторая группы входов текущего состояния устройства соединены с группами входов текущего состояния первого и второго модулей приоритетного прерывания, вход дещифратора соединен с выходами сигнала прерывания первого модуля приоритетного прерывания и устройства. 2. Устройство по п. 1, отличающееся тем, что модуль приоритетного прерывания содержит регистр запросов, регистр текущего состояния, триггер блокировки, триггер прерывания, узел приоритета, группу элементов И и элементы И и ИЛИ, причем группа входов запросов прерывания модуля соединена с группой входов регистра запросов, вход которого соединен со входом триггера блокировки и первым входом первого элемента И, второй и третий входы которого соединены соответственно со входом разрешения прерывания модуля и выходом элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами узла приоритета и регистра текущего состояния, группа входов и группа выходов которого соединены соответственно с группой входов текущего состояния модуля м первой группой входов узла приоритета, вторая группа входов которого соединена с группой выходов регистра запросов и первыми входами элементов И группы, вторые входы и выходы которых соединены соотвьственно с выходом второго элемента И и группой выходов модуля, первый вход второго элемента И соединен со входом разрешения считывания модуля, второй вход второго элемента И соединен с выходом регистра запросов и четвертым входом первого элемента И, выход которого соединен с первым входом триггера прерывания, второй вход которого соединен со входом синхронизации модуля, выход триггера прерывания соединен с выходом сигнала прерывания модуля и первым входом триггера блокировки, второй вход которого соединен с первым входом регистра текущего состояния и входом разрешения записи модуля, второй вход регистра текущего состояния соединен со входом выборки приоритета модуля. Источники информации, принятые во внимание при экспертизе 1. Козуб В. М. Системы прерывания ЦВМ М., «Советское радио, 1976, с. 98.-100, рис. 3,11. 2. Intel 8080 microcomputer System.Users. Manual, Santa Clara, 1975, 5-198 (прототип).

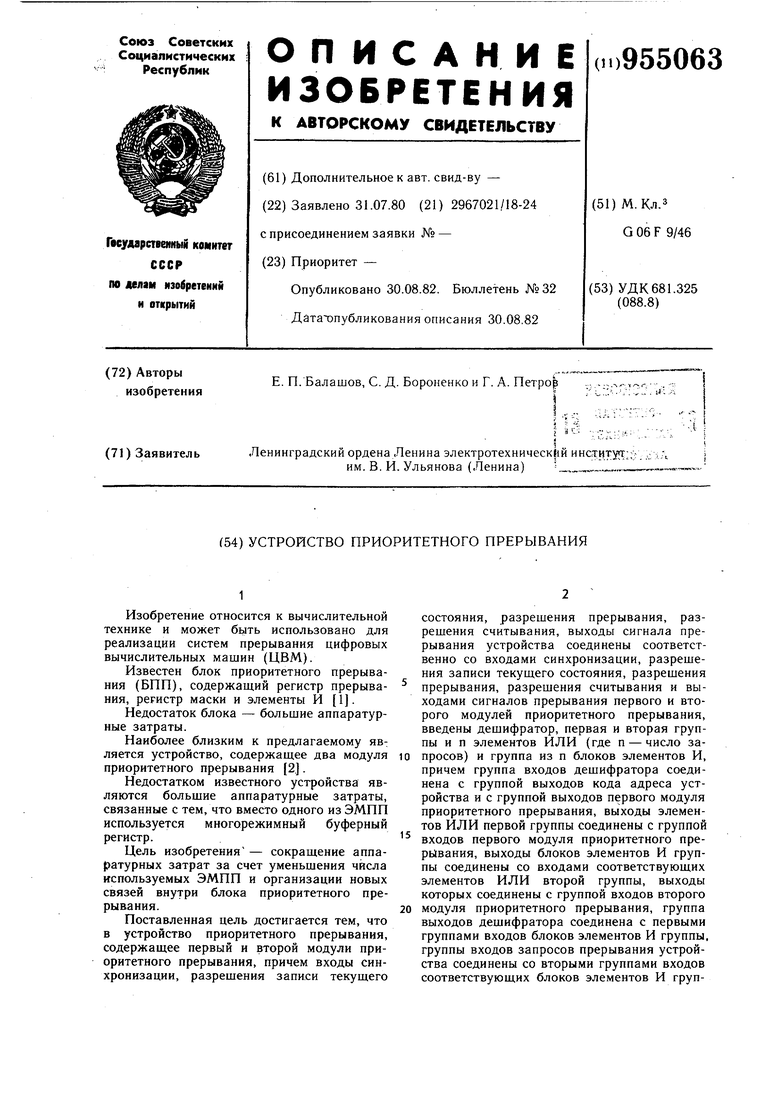

Составитель М. Кудряшев

Редактор Л. Пчелинская

Техред А. БойкасКорректор О. Билак Заказ 6171/54

Тираж 731Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

fO «li Ъ

е

Авторы

Даты

1982-08-30—Публикация

1980-07-31—Подача