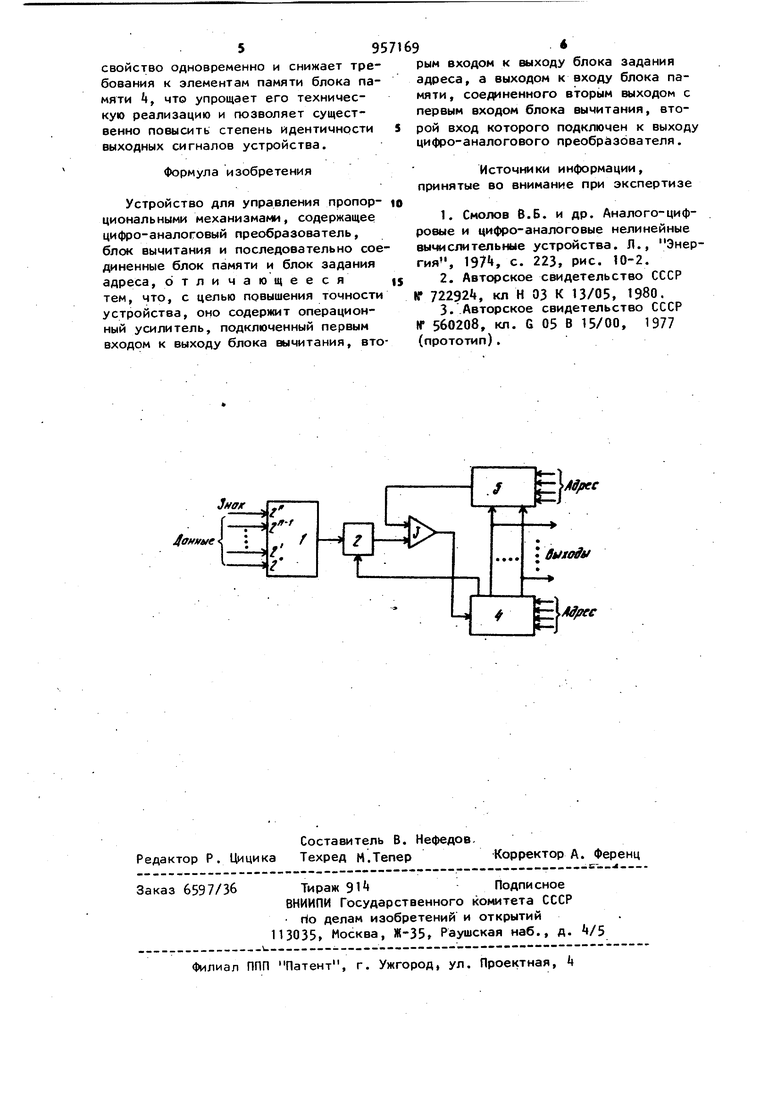

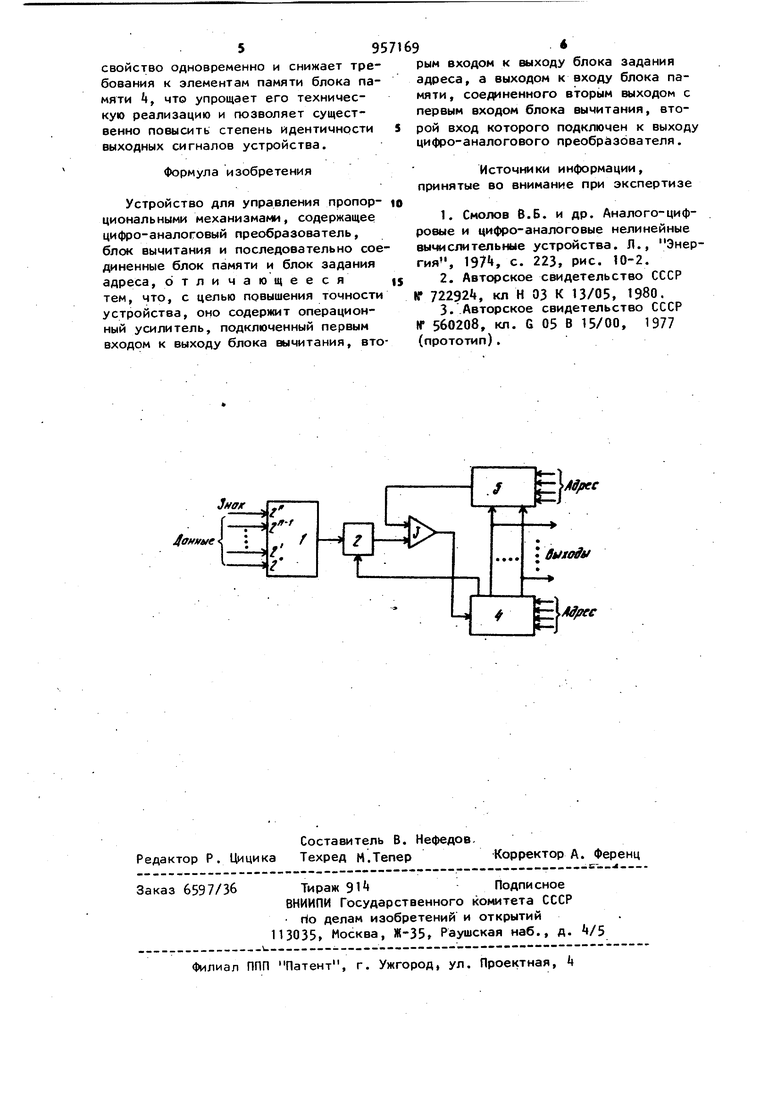

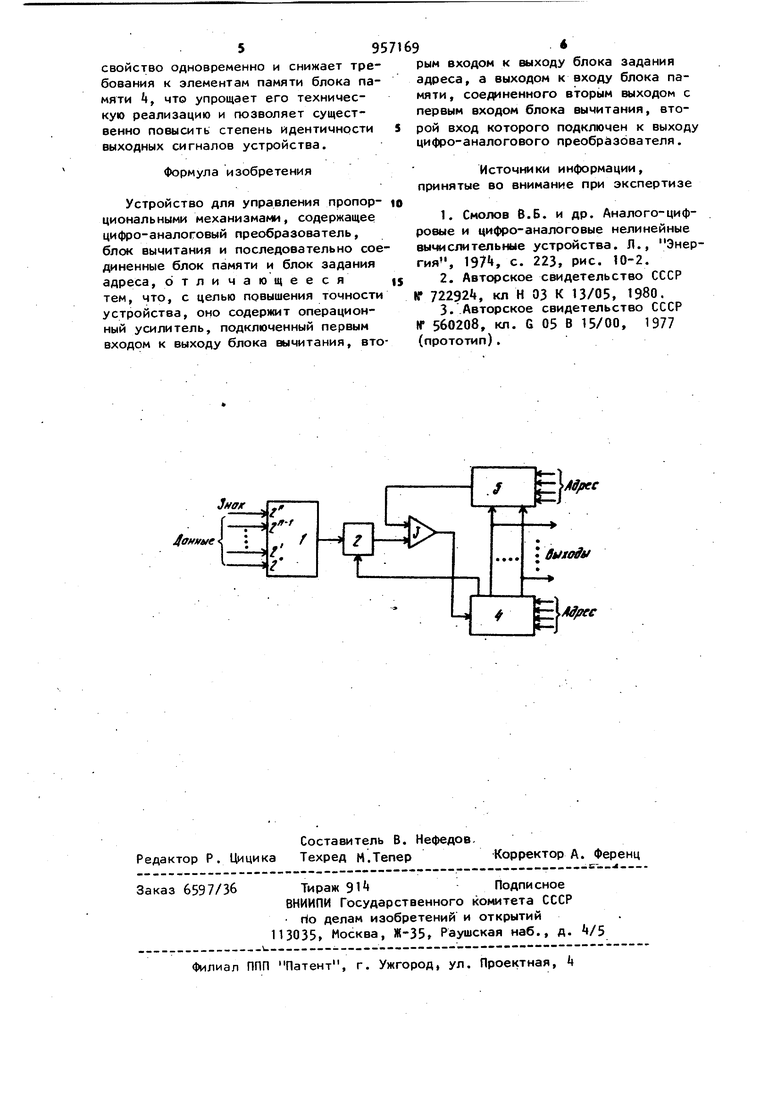

Изобретение относится к технике преобразования цифровых сигналов в аналоговые и может быть использовано в частности в устройствах управления многомерными объектами, например, металлорежущими станками, роботами. Известно устройство управления про порциональными механизмами, содержащее цифро-аналоговый преобразователь блок адреса и блок памяти, шины данных подсоединены к цифровым входам цифро-аналогового преобразователя, а его выход - к входу блока адреса, выходы которого подключены к соответствующим входам блока памяти l . Недостаток этого технического решения заключается в малой динамической точности, обусловленной интегрирующим характером нагрузки в блоке памяти. Известен также преобразователь код-аналог, содержащий источник опор ного напряжения, весовые сопротивления, управляемый кодом коммутатор весовых сопротивлений, ключевые элементы, схему управления ключевыми элементами, операционный усилитель, один вход которого подключен к допслиительному источнику опорного напряжения, второй вхбд - к выходу коммутатора весовых сопротивлений, а выход через развязывающие диоды - к управляемым выводам соответствующих ключевых элементов 2 , Недостатки этого технического решения заключаются в сложности технической реализации, требующей дополнительного источника опорного напряжения, в малой динамической точности, обусловленной интегрирующим характером нагрузки . Наиболее близким техническим решением к изобретению.является устройство для управления пропорциональными механизмами, содержащее цифроаналоговый преобразователь, блок вычитания и последовательно соединенные блок памяти и блок задания адреса з. Недостатком известного является неудовлетворительная точность устройства. Цель изобретения - повышение точ ности устройства. Поставленная цель достигается те что устройство для управления пропорциональйыми механизмами содержит операционный усилитель, подключенны первым входом к выходу блока вычитания, вторым входом к выходу блока задания адреса, а выходом к входу блока памяти, соединенного вторым выходом с первым входом блока вычитания , второй вход которогу подключен к выходу цифро-аналогового преобразователя. На чертеже изображена блок-схема устройства. Схема содержит цифро-аналоговый преобразователь 1, блок вычитания 2 операционный усилитель 3, блок памяти 4 и блок задания адреса 5. Устройство работает следующим об разом. На вход устройства по шинам данных поступает кодовый эквивалент требуемого выходного сигнала управления пропорциональным механизмом, при этом число разрядов кода данны равно (п-1) + 1, а п-й разряд предста лен сигналом знака. Кодовая комбинация сигналов на входе цифро-аналогового преобразова теля 1 формирует на его выходе напр жение ,, . где ди - масштабный коэффициент, соответствующий единице младшего, разряда кода да ных; а - значение i-ro разряда ко данных, равное 1 или 0; 2 - основание системы счисле ния; {п+1) - число разрядов преобразо При а 1 ,ар,а ,... ,af| О значени сигнала UQ соответствует половине м симально возможного напряжения U, Поэтому при единичном уровне сигнал знака выходные сигналы преобразователя больше или равны Ug, а при нул вом - меньше UQ. Использование этог свойства, а также представление данных в дополнительном коде при нулевом уровне сигнала знака позволяют сформировать относительно U симметрично изменяющееся напряжение. В первом такте на вход цифро-аналогового преобразователя 1 подается сигнал знака а, 1 и нулевое значение кода данных, сигналом адреса в блоке памяти 4 подключается вход элемента памяти, соответствующий второму выходу блока памяти t, а в блоке задания адреса 5 на выходе формируется нулевой уровень. Такое включение приводит к установлению на первом входе блока вычитания 2 сигнала, равного Ул. 6 каждом из последующих тактов на выходе блока вычитания 2 выдается сигнал разности между сигналами U и UQ , полярность которого задается сигналом знака. Синхронно с формированием этого сигнала сигнал адреса порождает коммутацию соответствующего выхода блока памяти k через блок задания адреса 5 на второй вход операционного усилителя 3. Незначительное несовпадение уровней на его первом и втором входах формирует на выходе операционного усилителя 5 в К раз большее напряжение (к - коэффициент усиления усилителя 5)) которое вызывает интенсивное изменение напряжения на соответствующем выходе блока памяти k (выходе устройства); .на выходе операционного усилителя 3 устанавливается напряжение, поддерживающее требуемое значение выходного сигнала устройства. За счет формирования на выходе операционного усилителя 3 в первый момент напряжения, значительно превышающего разность сигналов текущего И предыдущего тактов, время установления необходимого выходного сигнала устройства резко сокращается,что повышает его динамическую точность.Статическая точность также повышается, так как .цепи первого и второго входов операционного усилителя 3 практически не нагружают источники сигналов, поэтому коммутирующие элементы в блоке задания адреса 5 не искажают выходной сигнал - передают его с коэффициентом, равным единице; кроме того, отклонения в масштабе передачи в нагруженных цепях блока памяти компенсируютсявыходным напряжением операционного усилителя 3. Это

свойство одновременно и снижает требования к элементам памяти блока памяти Ц, что упрощает его техническую реализацию и позволяет существенно повысить степень идентичности выходных сигналов устройства.

Формула изобретения

Устройство для управления пропор- ю циональными механизмами, содержащее цифро-аналоговый преобразователь, блок вычитания и последовательно соединенные блок памяти и блок задания адреса, отличающееся|5

тем, что, с целью повышения точности устройства, оно содержит операционный усилитель, подключенный первым входом к выходу блока вычитания, вторым входом к выходу блока задания адреса, а выходом к входу блока памяти, соединенного вторым выходом с первым входом блока вычитания, второй вход которого подключен к выходу цифро-аналогового преобразователя.

Источники информации, принятые во внимание при экспертизе

1.Смолов В.Б. и др. Аналого-цифровые и цифро-аналоговые нелинейные вычислительные устройства. Л., Энергия, 197, с. 223, рис. 10-2.

2.Авторское свидетельство СССР

ГГ 72292, кл Н 03 К 13/05, 1980.

3.-Авторское свидетельство СССР 1Г 560208, кл. G 05 В 15/00, 1977 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД | 1972 |

|

SU433634A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Функциональный преобразователь | 1983 |

|

SU1166147A1 |

| Калибратор фазы | 1982 |

|

SU1048424A1 |

| Цифро-аналоговый функциональный преобразователь | 1980 |

|

SU895973A1 |

| Устройство для синусно-косинусного цифроаналогового преобразования | 1983 |

|

SU1278897A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Многоканальное устройство управления | 1986 |

|

SU1409973A1 |

| Устройство для измерения температуры | 1985 |

|

SU1315831A1 |

| Функциональный генератор | 1986 |

|

SU1310854A1 |

Авторы

Даты

1982-09-07—Публикация

1981-01-16—Подача