1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля функционирования систем передачи данных, в состав которых входят ЭВМ, а также для анализа причин возникновения неисправностей и анализа последствий, к которым приводит возникновение неисправности.

Известно устройство для фиксации сбоев, содержащее регистр памяти, элементы ИЛИ, группу элементов И, дешифратор, счетчик, выходной регистр, реле времени, элемент НЕ, генератор импульсов и формирователь tl

Недостатком устройства является то, что фиксация неисправности происходит только в момент возникновения сбоя, не фиксируются сигналы, предшествующие сбою, что затрудняет анализ причин, приводящих к сбою, п также не фиксируется работа ЭВМ или З11ачительной системы после возникновения сбоя, так как некоторые виды сбоев или неисправностей исзтраваяются 1ти корректируются.

Наиболее близким к предлагаемому является устройство для анализа причин , неисправности ЭВМ, содержащее последовательные сдвиговые регистры, для записи поступающих с определенной частотой управляющих сигналов, параллельные сдвиговые регистры для залнсн с определенной частотой выждных сигналов регистров, сшсфонизирукшше переключатели, с помощью которых устанавливает10ся режим залнсн ниформадни в регистры либо режнм вывода информации на регистра, н устройство для визуальтай индикации содержимого регистров С2.

Недостаток устройства состоит в том,

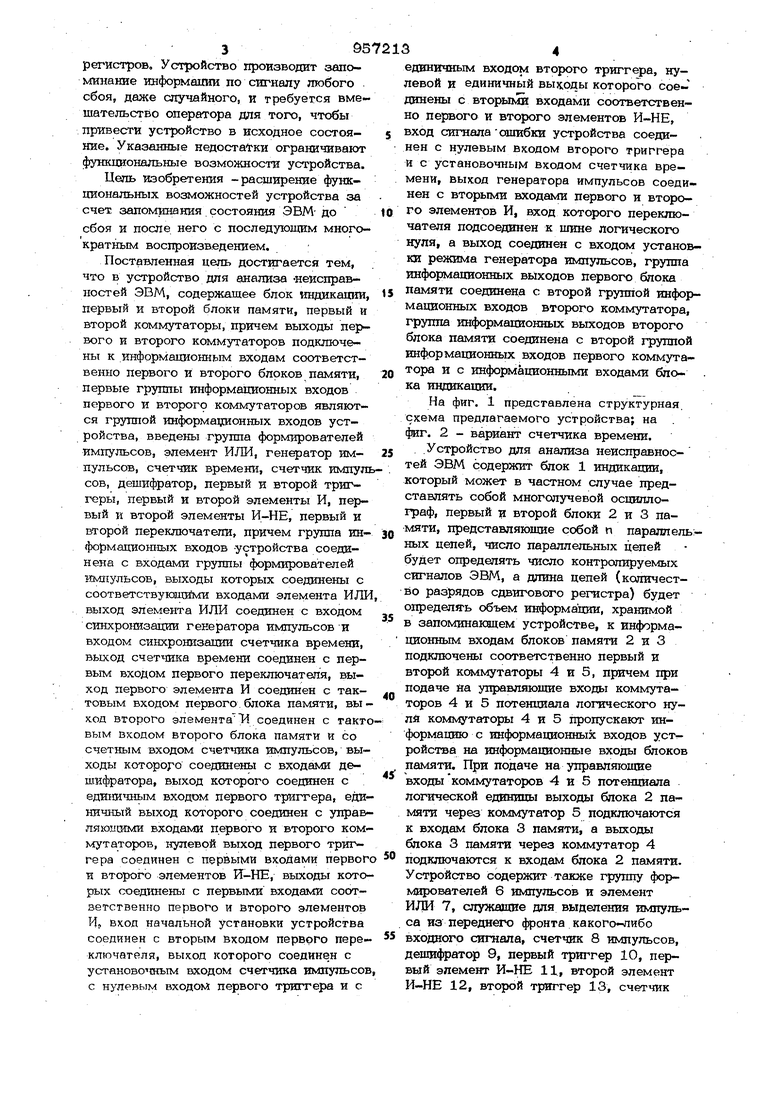

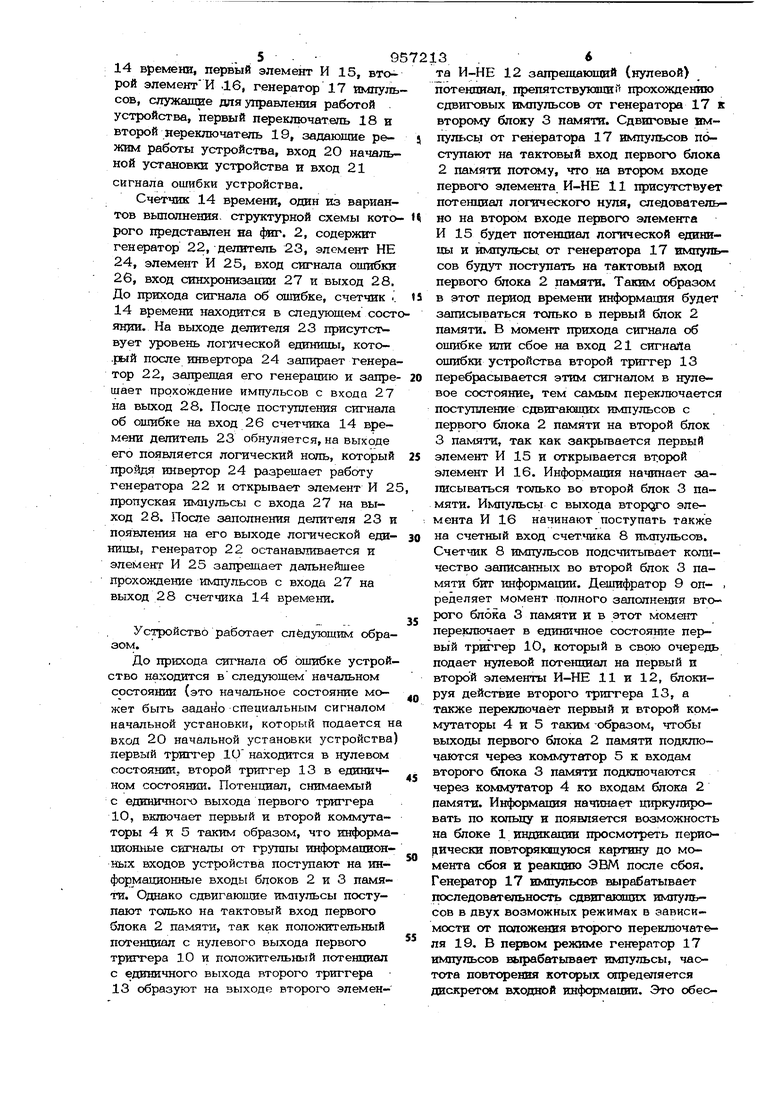

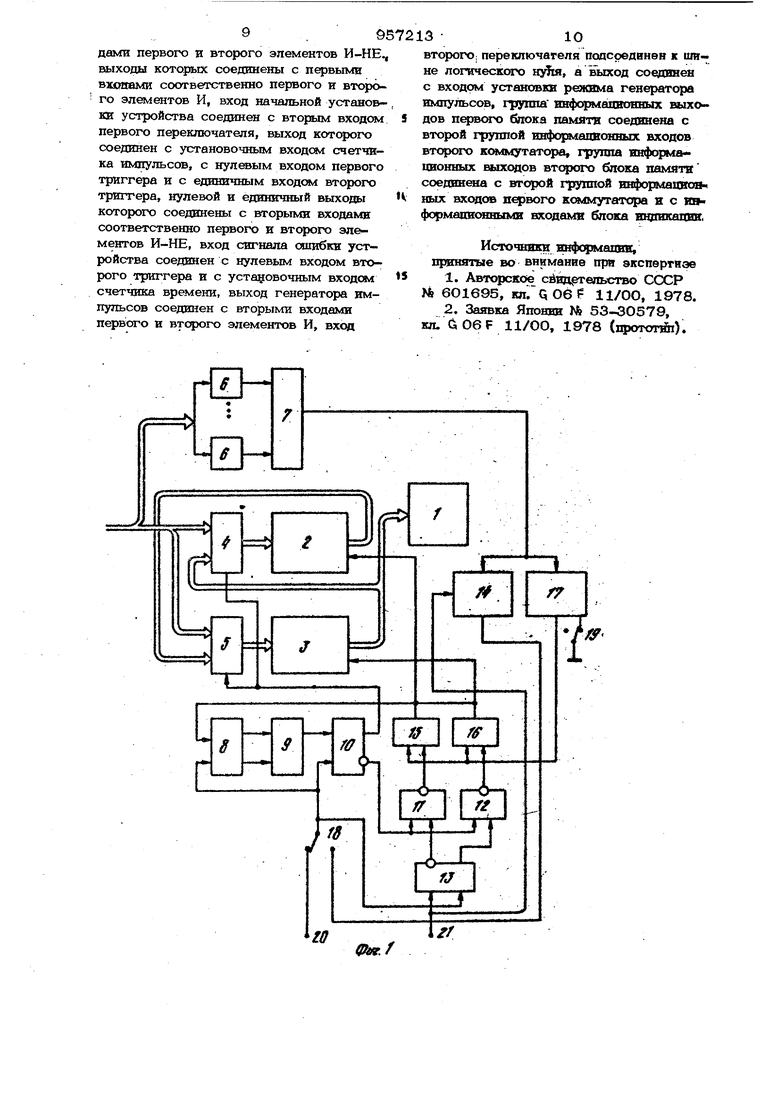

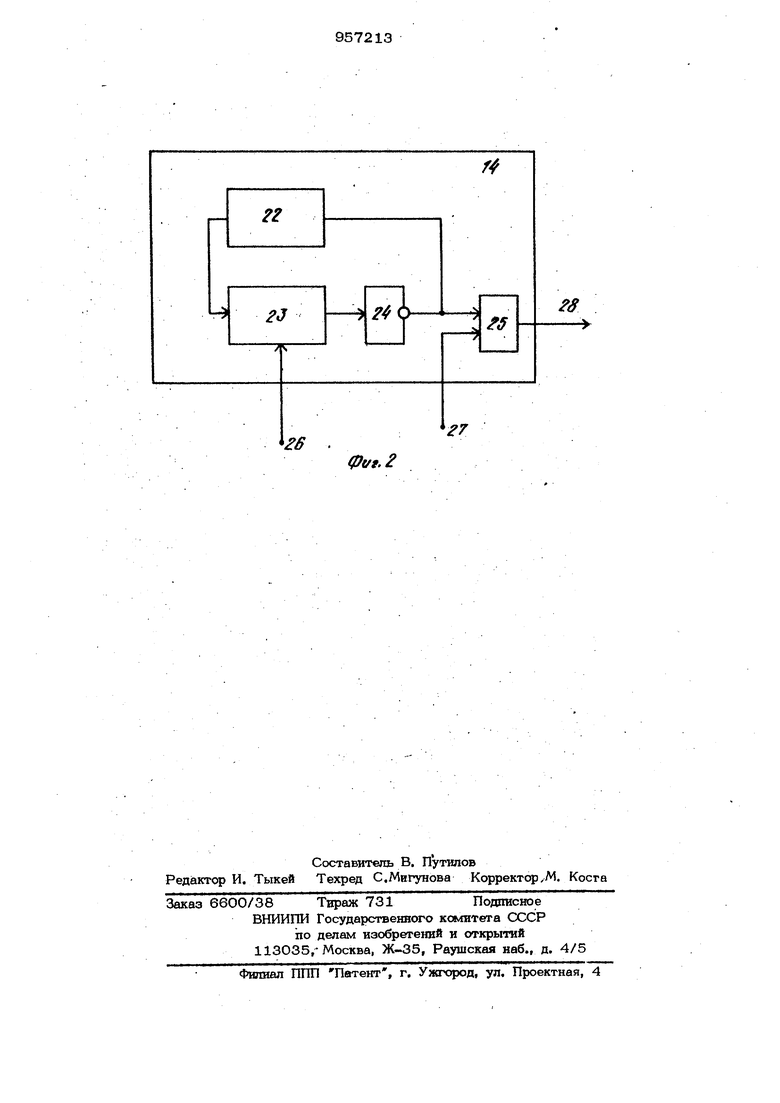

5 что запись информации происходит только до появлення сигнала о сбое, в то время как некоторые виды сбоев или неисправностей исправляются нпн корректируются контрольной аппаратурой. За20пнсь нвформаини пронсходит только с определенной частотой (днскр етной), что не позволяет наиболее полно использовать информалнонный объем сдвиговых 3957 регистров. Устройство производит запоминание информашш по сигналу любого . сбоя, даже случайного, и требуется вмешательство оператора для того, чтобы привести устройство в исходное состояние. Указанные недостатки ограничивают функциональные возможности устройства. Цель изобретения -расширение функциональных возможностей устройства за счете запоминания .состояния ЭВМ-до сбоя и после него с последующим многократным воспроизведением,; Поставленная цель достигается тем, что в устройство для анализа -неисправностей ЭВМ, содержащее блок индикации, первы и второй блоки памяти, первый и второй коммутаторы, причем выходы первого и второго коммутаторов подключены к информшшош ым входам соответственно первого и второго блоков памяти, первые группы информационных входов первого и второго коммутаторов япвляют- ся группой информационных входов устройства, введены группа формирователей импульсов, элемент ИЛИ, генератор импульсов, счетчик времени, счетчик импуль сов, дешифратор, первый и второй триггеры, первый и второй элементы И, первый и второй элементы И.-НЕ, первый и вгорой переключатели, причем группа информационных входов устройства соедииена с входами группы формирователей импульсов, выходы которых соединены с соответствующими входами элемента ИЛИ выход элемента ИЛИ соединен с входом синхронизации генератора импульсов и входом синхронизации счетчика времени, выход счетчика времени соединен с первым входом первого переключателя, выход первого элемента И соединен с тактовым входом первого блока памяти, вы ход второго элементаТ соединен с такто вым входом второго блока памяти и со счетным входом счетчика импульсов, выходы которого соединень с входами дешифратора, выход которого соединен с единичньгм входом первого триггера, единичный выход которого соединен с управляюцоЕМИ входами п.ервого и второго коммутаторов, нулевой выход первого триггера соединен с первыми входами первого и второго элементов И-НЕ, выходы которых соединены с первыми входами соотзетственно первого и второго элементов И, вход начальной установки устройства соединен с вторым входом первого переключателя, выход которого соединен с установогкым входом счетчика импульсов с нулевым входом первого триггера и с единичным входом второго триггера, нуевой и единичный вызсоды которого соеинены с вторы входами соответственно первого и второго элементов И-НЕ, ход сигнала ошибки устройства соединен с нулевым входом второго триггера и с установочным входом счетчика времени, выход генератора импульсов соединен с вторыми входами первого и второГО элементов И, вход которого переключателя подсоединен к шине логического нуля, а выход соединен с входом установки режима генератора импульсов, группа информационных выходов первого блока памяти соединена с второй группой информационных входов второго коммутатора, группа информационных выходов второго ° памяти соединена с второй группой информационных входов первого коммута Р « с информационными входами бло- . ка ищщкации. На фиг. 1 представлена структурная, схема предлагаемого устройства; на . фиг, 2 - вариант счетчика времени. . .Устройство для анализа неисправное одержит блок 1 индикации, который может в частном случае представлять собой многолучевой осцилло « первый и второй блоки 2 и 3 представляющие собой п параллель: ° параллельных цепей буДет определять число контролируемых сигналов ЭВМ, а длина цепей (количество разрядов сдвигового регистра) будет определять объем информации, хранимой в запоминающем устройстве, к ин(}у5рмационным входам блоков памяти 2 и 3 подключены соответственно первый и второй коммутаторы 4 и 5, причем при подаче на управляющие входы коммутаторов 4 и 5 потенциала логического нули коммутаторы 4 и 5 пропускают информацию с информационных входов устройства на информационные входы блоков памяти. При подаче на управляющие входыкоммутаторов 4 и 5 потенциала логической единицы выходы блока 2 памяти через коммутатор 5 подключаются к входам блока 3 памяти, а выходы блока 3 памяти через коммутатор 4 подключаются к входам блока 2 памяти. Устройство содержит также группу формирователей 6 импульсов и элемент ИДИ 7, служащие для выделения импуль. са из переднего фронта какого- ибо входного сигнала, счетчик 8 иг шульсов, дешифратор 9, первый триггер 10, первый элемент И-НЕ 11., второй элемент И-НЕ 12, второй триггер 13, счетчик . 5 . -9 14 времени, первый элемент И 15, второй элементИ ,16, генератор 17 импуль сов, служащие датя управления работой устройства, первый переключатель 18 и второй переключатель 19, задающие режим работы устройства, вход 2О начальной установки устройства и вход 21 сигнала ошибки устройства. Счетчик 14 времени, один из вариантов вьшолнения, структурной схемы кото рого представлен на фиг. 2, содержит генератор 22, делитель 23, элемент НЕ 24, элемент И 25, вход сигнала ошибки 26, вход синхронизашш 27 и выход 28. До прихода сигнала об ошибке, счетчик .. 14 времени находится в следующем сост янки. На выходе делителя 23 присутст вует уровень логической единицы, кото.рый после инвертора 24 запирает генератор 22, запрещая его генерацию и запрешает прохождение импульсов с входа 27 на выход 28. После поступления сигнала об ошибке на вход 26 счетчика 14 времени делитель 23 обнуляется,на выходе его появляется логический ноль, который пройдя инвертор 24 разрешает работу генератора 22 и открывает элемент И 25 пропуская импульсы с входа 27 на выход 28. После заполнения делителя 23 и появления на его выходе логической еди- ницы, генератор 22 останавливается и элемент И 25 аахфежает дальнейшее прохождение импульсов с входа 27 на выход 28 счетчика 14 времени. Устройство работает следующим образом. До прихода сигнала об ошибке устройство находится вследующем начальном состоянии (это начальное состояние может быть задано специальным сигналом начальной установки, который подается н вход 20 начальной установки устройства) первый триггер 1О находится в нулевом состоянии, второй триггер 13 в единичном состоянии. Потенциал, cни Iaeмый с едшшчно1Ю выхода первого триггера 10, включает первый и второй коммутаторы 4 к 5 таким образом, что информационные сигналы от группы информационных входов устройства поступают на информационные входы блоков 2 и 3 памяти. Однако сдвигаюшие импульсы поступают только на тактовый вход первого блока 2 памяти, так как положительный потенциал с нулевого выхода первого триггера 10 и положительный потенциал с единичного выхода второго триггера 13 образуют на выходе второго элемен3 .4 та И-НЕ 12 запрещающий (нулевой) потенциал, препятствующий прохождению сдвиговых импульсов от генератора 17 к второму блоку 3 памяти. Сдвиговые импульсы от генератора 17 импульсов поступают на тактовый вход первого блока 2памяти потому, что на втором входе первого элемента И-НЕ 11 присутствует потенциал логического нуля, следовательно на втором входе первого элемента И 15 будет потенциал логической единицы и импульсы, от генератора 17 импульсов будут поступать на тактовый вход первого блока 2 памяти. Таким образом в этот период времени информация будет записываться только в первый блок 2 памяти. В момент прихода сигнала об ошибке или сбое на вход 21 сигнала ошибки устройства второй триггер 13 перебрасывается этим сигналом в нулевое состояние, тем самым переключается поступление сдвигакшщх импульсов с первого блока 2 памяти на второй блок 3памяти, так как закрьгаается первый элемент И 15 и открывается второй элемент И 16. Информация начинает записываться только во второй блок 3 памяти. Импульсы с выхода второго элемента И 16 начинают поступать также на счетный вход счет.чика 8 импульсов. Счетчик 8 импульсов подсчитывает количество записанных во второй блок 3 памяти бит информации. Дешифратор 9 оп- . ределяет момент полного заполнения второго блока 3 памяти и в этот момент переключает в единичное состояние перьвьгй триггер 10, который в свою очередь подает нулевой потенциал на первый и второй элементы И-НЕ 11 и 12, блокируя действие второго триггера 13, а также переключает первый и второй коммутаторы 4 и 5 таким -образом, чтобы выходы первого блока 2 памяти подключаются через коммутатор 5 к входам второго блока 3 памяти подключаются через коммутатор 4 ко входам блока 2 памяти. Информация начинает циркулировать по кольцу и появляется возможность на блоке 1 индикации просмотреть периодически пoвтqpяю8цyюcя картину до момента сбоя и реакцию ЭВМ после сбоя. Генератор 17 шлпульсов вырабатывает последовательность сдвигающих импульсов в двух возможных режимах в зависимости от попоженЕя второго переключателя 19, В первом режиме генератор 17 импульсов вырабатывает импульсы, частота повторения которых определяется дискрете входной информации. Это обеспечивается следующим образом. Фермирователи 6 импульсов вырабатывают импульсы из передних фронтов входных сигналов. Выходы фйрмирователей 6 импульсов объединены элементом ИЛИ 7. Сиг. нал с выхода э емента ИЛИ 7 поступает на Вход синхронизации генератора 17 импульсов, синхронизируя его по фазе и подстраивая по частоте. Если например на информационных входах устройства будет постоянно присутствовать логический нуль или логическая единица, то генератор 17 импульсов будет генерировать частоту, установленную предыдуншм периодом входного сигнала. При появиеНИИ сигналов на информацио1шых входах устройства генератор снова подстроится по фазе и частоте под период входного сигнала. Вторым режимом работы генератора 17 импульсов является режим умножения частоты входного сигнала. Вторым режимом работы генератора 17 импульсов является режим умножения частоты входного сигнала. Таким образом устройство при первом режиме работы 17 генератора позволяет записывать дискрет входной информации в соответствукшшй разряд сдвиговых регис ров на которых построены блоки 2 и 3 памяти. Этим режимом максимально используете объем памяти. При втором режиме рабо ты генератора 17 импульсов каждый дискрет входной информапкн записьгааетс в несколько разрядов сдвигового репастра. Число этих разрядов будет совпадать с коэффициентом умножения частоты генератора 17 импульсов. При этом режиме работы в блоках 2 и 3 памяти запоминается меньшее количество информации, но появляется возможность для- анализа во времени различных сигналов, т.е. можно будет провести динамический анализ ситуаций, предшествутощих сбойно ситуации и реакции ЭВМ на сбойную ситуацию. При помощи первого переключателя 18 можно установить два воэмож Ных режима начальной установки. При первом режиме начальной установки сигнал начальной установки, определянзвщий момент начала записи, подается извне и поступает на вход 2О начальной установки устройства. Переход из режима непрерьганой записи входных сигналов в режим юздикации происходит при поступлешш сигнала об ошибке на вход 21 сигнала омгбки устройства. Во режиме начальной установки сигнал-о начальной установке будет поступать с выхода счетчика времени. Таким образом, применение предда;aeMoro устройства позволяет расширить функциональные возможности в частя анализа причин возникновения неисправности ЭВМ, позволяет записывать информацию о состоянии ЭВМ как до появления сбоя, так и -после него. Устройство позволяет запис тать логические уровни входных и выходных сигналов от ЭВМ в режиме внешней синхронизации, а также оценивать временные характеристики входных сигналов в режиме умножения частоты. Формула изобретения Устройство для анализа неисправностей ЭВМ, содержащее блок индикации, первый и второй блоки памяти, первый и второй коммутаторы, причем выходы первого и второго коммутаторов подключены к информационным входам соответственно первого и второго блоков памяти, первые группы информационных входов первого и второго коммутаторов 5ШЛ5ПОТ- ся группой информационных входов устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет запоминания состояния ЭВМ до сбоя и после него с последующим многократным воспроизведением, в устройство введены rpyima формирователей импульсов, элемент ИЛИ, генератор импульсов, счетчик времени, счетчик импульсов, дешифратор, первый и второй триггеры, первый и второй элементы И, первый и второй элементы И-НЕ, первый и второй переключатели, причем группа информационных входов устройства соединена с входами группы формирователей импульсов, выходы которых соединены с соответствующими входами элемента. ИЛИ, выход элемента ИЛИ соединен с входом синхронизации генератора импульсов и входом синхронизации счетчика времени, выход счетчика времени соединен с первьпд входом пфвого переключателя, выход первого элемента И соединен с тактовым входом первого блока памяти, выход второго элемента И соединен с тактовым входом второго блока памяти и со счетным входом счетчика импульсов, выходы которого соединены с входами дешифратора, выход которого соединен с единичным входом первого триггера, единичный выход которого соедтш н с управляющими входами первого и вторюго коммутаторов, нулевой вькод первого триггера соединен с первыкга вхо90дами первого и второго элементов И-НЕ выходы которых соединены с первыми вхоиало соответственно первого и второго элементов И, вход начальной установки устройства соединен с вторым входом первого переключателя, выход которого соединен с установочным входом счетчика импульсов, с нулевым входом первого триггера и с единичным входсж второго триггера, нулевой и единичный выходы которого соедзаснены с вторыми входами соответственно первого и второго элементов И-НЕ, вход сигнала ошибки устройства соединен с нулевым входом второго триггера и с установочным входом счетчика времени, выход генератора импульсов соединен с вторыми входами первого и второго элементов И, вход 3 второго: перекпючагеля поасредвнен к шине логического «yha, а соединен с входом установки режима генератора импульсов, группа внфорлацвонных выходов блока памяти соедииена с второй группой инфо1вла1Шонных входов второго кс 1мзгтатора, группа информационных выходов втсфого блока памяти соедииена с второй группой информацвоа ных входов первого к А мутатора в с и формапи жными входами блока шщшсацни. Источники внфqf IaIШH, пршштые во внимание при экспертизе 1.Авторское сйидргеяьство СССР Nf 601695, кпГаОбР 11/00, 1978. 2,Заявка Японии № 53-30579, кл. Ui Об F 11/ОО, 1978 (прототт).

2В .

г7

0vt.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для сопряжения внешнего устройства с магистралью ввода/вывода | 1981 |

|

SU968799A1 |

| Устройство для фиксации сбоев | 1979 |

|

SU860074A1 |

| Устройство для захвата магистрали ЭВМ | 1982 |

|

SU1075247A1 |

| Устройство для контроля внешних абонентов вычислительных комплексов | 1982 |

|

SU1062710A1 |

| Устройство для сопряжения ЭВМ с абонентом по последовательному каналу связи | 1987 |

|

SU1442997A1 |

| Устройство для сопряжения ЭВМ с датчиками | 1987 |

|

SU1427375A1 |

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Устройство для сопряжения ЭВМ с внешней памятью | 1987 |

|

SU1515166A1 |

Авторы

Даты

1982-09-07—Публикация

1981-01-15—Подача