(54) МНОГОКАНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ

1

Изобретение относится к запоминающим устройствам и может быть применено для задач аппаратной поддержки средств математического обеспечения ЭВМ.

Известно многоканальное запоминающее устройство, содержащее накопитель, адресную диодную матрицу, регистр каналов регистр групп каналов, коммутирующие ключи, формирователи адресных сигналов и регистры сдвига 1.

Недостатком этого устройства является ограниченность области его применения.

Наиболее близким к предлагаемому является многоканальное запоминающее устройство стекового типа, содержащее регистр для хранения адреса последней занятой ячейки, регистр для хранения адреса текущей свободной ячейки, блок памяти и выходной регистр, предназначенное для использования по независимым каналам на основе принципа «первым в память - последним из памяти 2.

Недостатком указанного устройства является невысокое быстродействие, поскольку оно не обеспечивает режим работы, основанный на принципе «первым в память - перУСТРОЙСТВО

вым из памяти, за счет чего ограничивается область его применения.

Цель изобретения - повь1щение быстродействия устройства, а также расщирение области его применения за счет обеспечения 5 режима работы по принципу «первым в память - первым из памяти.

Поставленная цель достигается тем, что в многоканальное запоминающее устройство, содержащее блок памяти, регистр числа, регистр адреса последней занятой ячейки памяти и регистр адреса текущей свободной ячейки памяти, первый выход которого подключен к первому входу блока памяти, а первый вход и второй выход соединены соответственно с первыми выходом и входом ре15гистра адреса последней занятой ячейки памяти, вторые вход и выход которого подключены к первому выходу и первому входу регистра числа, вторые вход и вь1ход которого соединены с первым выходом и вторым входом блока памяти, введены буферный регистр адреса и регистр адреса первой занятой ячейки памяти, первые выход и вход которого соединены соответственно с вторым входом и третьим выходом регистра адреса текущей свободной ячейки памяти, вторые выход и вход регистра адреса первой занятой ячейки памяти подключены соответственно к третьему входу блока памяти и первому выходу буферного регистра адреса, первый вход и второй выход которого соединены соответственно с четвертым выходом и третьим входом регистра адреса текущей свободной ячейки памяти, пятый выход которого подключен к третьему входу регистра числа, третий выход которого соединен с вторым входом буферного регистра адреса, третий выход регистра адреса последней занятой ячейки памяти подключен к четвертому входу блока памяти.

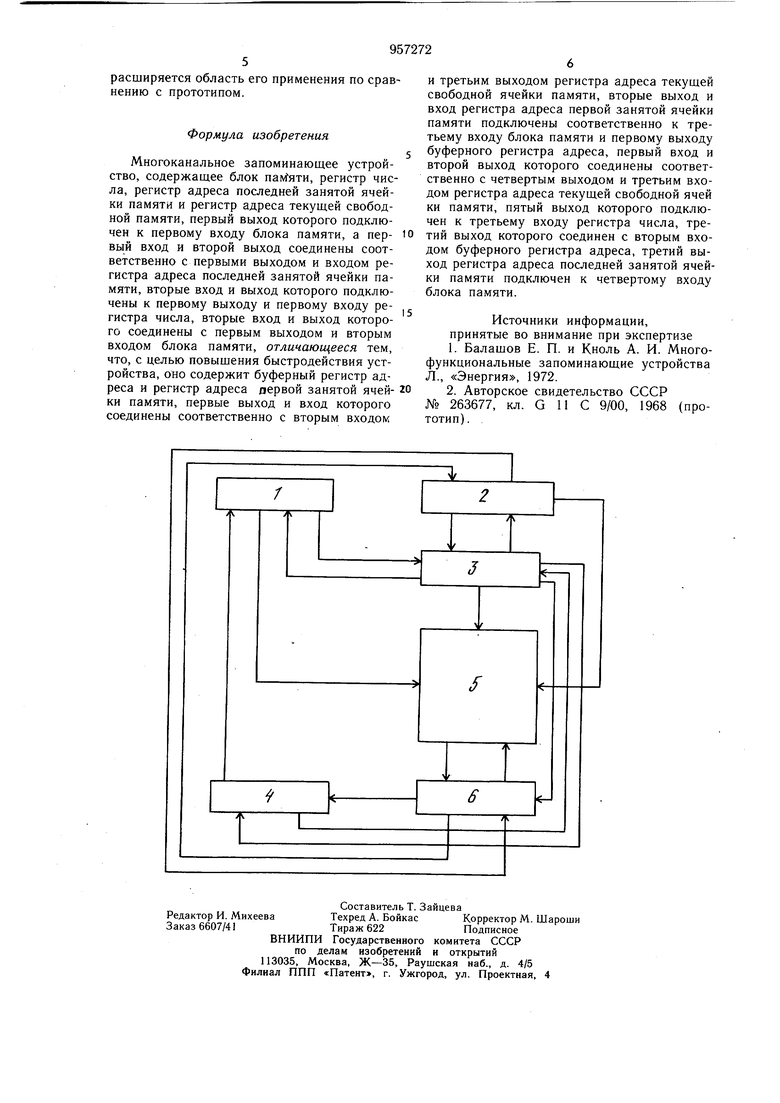

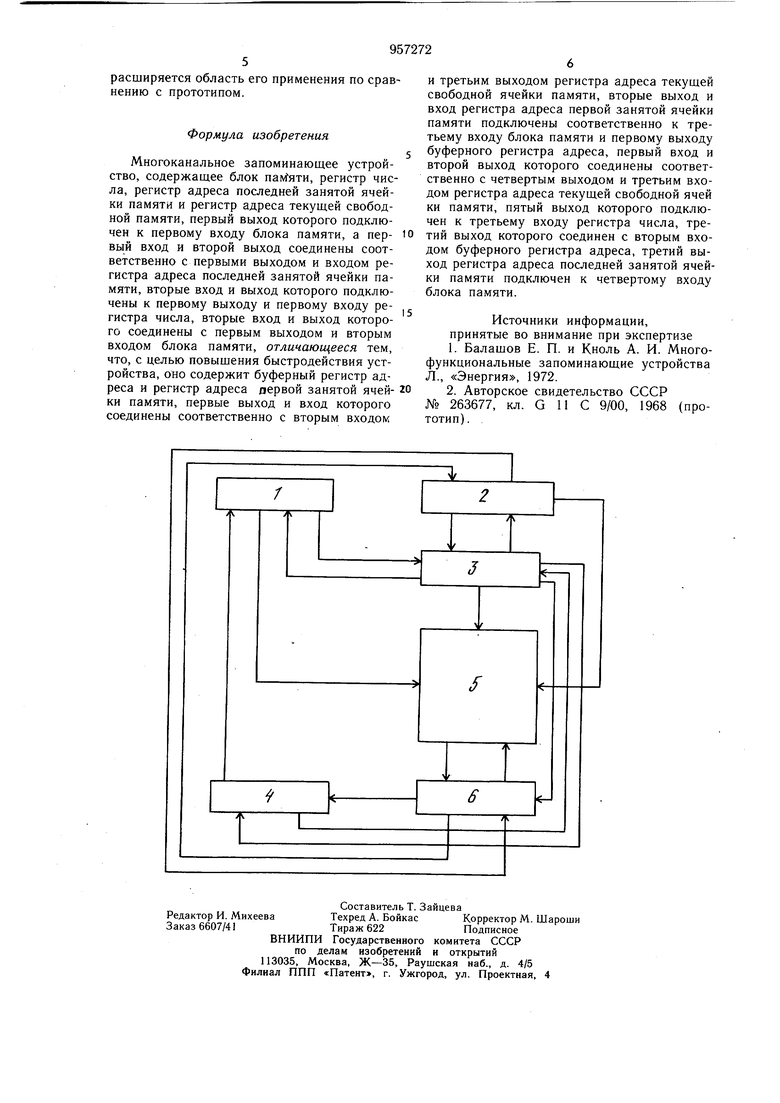

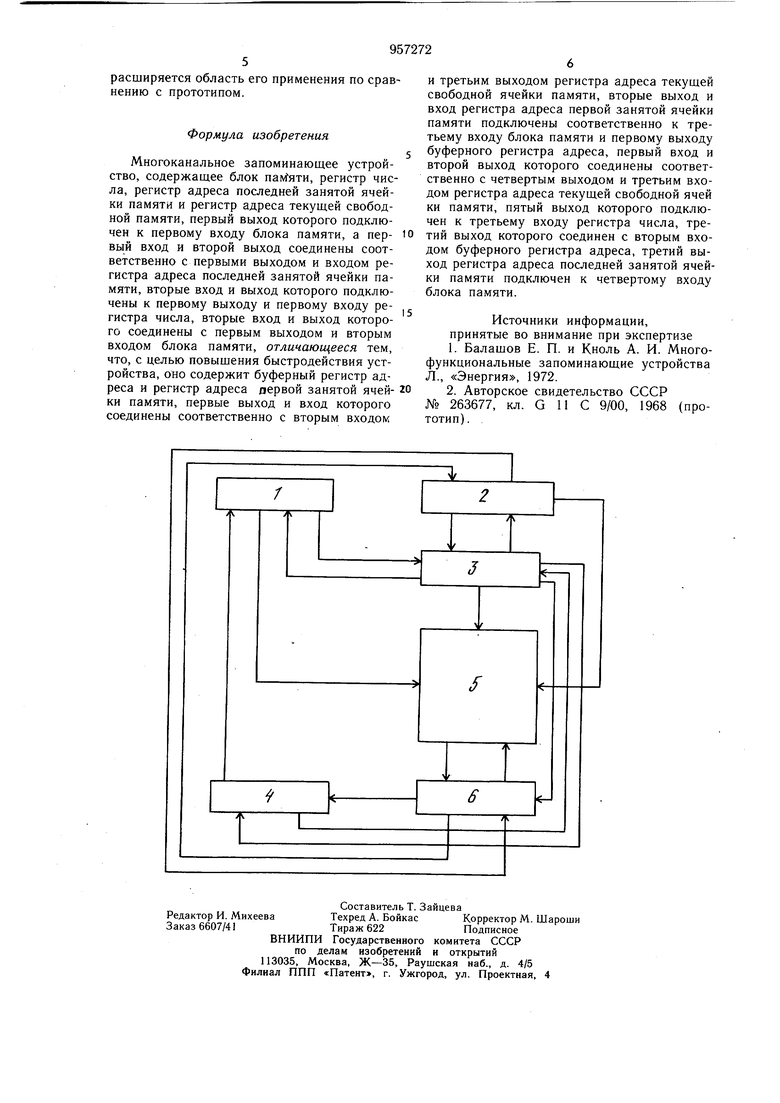

На чертеже представлена функциональная схема предложенного устройства.

Устройство содержит регистр 1 адреса первой занятой ячейки памяти, регистр 2 адреса последней занятой ячейки памяти, регистр 3 адреса текущей свободной ячейки, буферный регистр 4 адреса, блок 5 памяти и регистр 6 числа, состоящий из двух адресных и одной информационной частей. Каждая ячейка блока 5 памяти состоит из трех частей, двух адресных и информационной, регистры 1 и 2 состоят из нескольких частей, каждая из которых соответствует определенному каналу.

Устройство работает следующим образом.

Рассмотрим работу одного из каналов устройства.

Перед работой устройства производится разметка блока 5 памяти, в результате которой, в первой адресной части каждой его ячейки записан адрес следующей свободной ячейки. Для разметки блока 5 памяти в регистрах 2 и 3 устанавливается адрес первой ячейки блока 5. Затем в регистр 6 считывается содержимое ячейки, адрес которой указан в регистре 2, содержимое регистра 3 увеличивается на единицу. После этого содержимое регистра 3 записывается в первую адресную часть регистра 6, содержимое которого, в свою очередь, записывается в ячейку, адрес которой указан в регистре 2. Затем производится передача содержимого регистра 3 в регистр 2. Описанный процесс повторяется, пока не будут размечены все ячейки блока 5, после чего регистр 2 обнуляется, а в регистре 3 устанавливается адрес первой ячейки блока 5.

Запись в запоминающее устройство производится по адресу, содержащемуся в регистре 3, содержимое ячейки с этим адресом считывается в регистр 6, первая адресная часть которого передается в регистр 4, во вторую адресную часть ячейки записывается содержимое регистра 2, а в информационную часть - необходимый символ, после чего содержимое регистра 6 записывается

в блок 5 по адресу, содержащемуся в регистре 3.

Если записываемый символ является первым, то содержимое регистра 3 переписывается в регистры 1 и 2, в противном случае в регистр 6 считывается содержимое ячейки адрес которой указан в регистре 2. В первую адресную часть регистра 6 записывается адрес из регистра 3, далее содержимое регистра 6 записывается в блок 5 по адресу, содержащемуся в регистре 2, содержимое регистра 3 переписывается в регистр 2. Затем происходит передача содержимого регистра 4 в регистр 3.

Таким образом, в первой адресной части каждой занятой ячейки памяти блока 5 указывается адрес последующей занятой ячейки, что обеспечивает использование запоминающего устройства в режиме «бобслей, основанном на принципе «первым в память первым из памяти.

Во второй адресной части указывается адрес предыдущей занятой ячейки, что обеспечивает использование устройства в режиме «магазин, основанном на принципе «первым в память - последним из памяти.

Чтение из запоминающего устройства в режиме «бобслей производится по адресу, содержащемуся в регистре 1. Содержимое этой ячейки считывается в регистр 6. Затем содержимое первой адресной части регистра 6 пересылается в регистр 4, а содержимое регистров 1, 4 и 3 переписывается соответствелно в регистры 3, 1 и в первую адресную часть регистра 6, информационная часть которого обнуляется, после чего содержимое регистра 6 записывается в ячейку блока 5, адрес которой указан в регистре 3. Далее в регистр 6 считывается содержимое ячейки, адрес которой содержится в регистре 1, вторая адресная часть регистра 6 обнуляется и его содержимое записывается в блок 5 по адресу, находящемуся в регистре 1.

Чтение из запоминающего устройства в режиме «магазин производится по адресу, содержащемуся в регистре 2. Содержимое этой ячейки блока 5 считывается в регистр 6, в первую адресную часть которого записывается содержимое регистра 3. Затем содержимое регистра 2 пересылается в регистр 3, а содержимое второй адресной части регистра 6-в регистр 2, после чего информационная часть регистра 6 обнуляется и его содержимое записывается в блок 5 по адресу, находящемуся в регистре 2.

Работа устройства по нескольким независимым каналам выполняется аналогичным образом.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает два принципа выборки информации («бобслей и «магазин) по нескольким независимым каналам, за счет чего повыщается быстродействие и

расширяется область его применения по сравнению с прототипом.

Формула изобретения

Многоканальное запоминающее устройство, содержащее блок , регистр числа, регистр адреса последней занятой ячейки памяти и регистр адреса текущей свободной памяти, первый выход которого подключен к первому входу блока памяти, а первый вход и второй выход соединены соответственно с первыми выходом и входом регистра адреса последней занятой ячейки памяти, вторые вход и выход которого подключены к первому выходу и первому входу регистра числа, вторые вход и выход которого соединены с первым выходом и вторым входом блока памяти, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит буферный регистр адреса и регистр адреса первой занятой ячейки памяти, первые выход и вход которого соединены соответственно с вторым входом

и третьим выходом регистра адреса текущей свободной ячейки памяти, вторые выход и вход регистра адреса первой занятой ячейки памяти подключены соответственно к третьему входу блока памяти и первому выходу буферного регистра адреса, первый вход и второй выход которого соединены соответственно с четвертым выходом и третьим входом регистра адреса текущей свободной ячей ки памяти, пятый выход которого подключен к третьему входу регистра числа, третий выход которого соединен с вторым входом буферного регистра адреса, третий выход регистра адреса последней занятой ячейки памяти подключен к четвертому входу блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Балащов Е. П. и Кноль А. И. Многофункциональные запоминающие устройства Л., «Энергия, 1972.

2.Авторское свидетельство СССР

№ 263677, кл. G 11 С 9/00, 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Мультиплексный канал с динамическим распределением памяти | 1977 |

|

SU674010A2 |

| Процессор мультиобработки данных | 1975 |

|

SU590745A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для регистрации информации | 1974 |

|

SU506910A1 |

Авторы

Даты

1982-09-07—Публикация

1980-11-21—Подача