(54) МИКГОПЮ1ТАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство управления микропрограм-МНыМи пЕРЕХОдАМи | 1979 |

|

SU813428A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство управления контролем | 1985 |

|

SU1285471A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано при построении микропрограммных устройств управления многопроцессорных вычислительных систем и ЦВМ, проектируемых на однотипных БИС.

Известно микропрограммное устройство управления, содержащее арифметический блок, блоки памяти адресов и микроопераций, счетчик команд, регистры, дешифратор, логические элементы И и ИЛИ Ц.

Недостатком указанного устройства являются низкие функциональные возможности, обусловленные тем, что структура устройства не позволяет увеличивать объем реализуемых программ путем введения дополнительных однотипных устройств.

Из известных микропрограммных устройств управления наиболее близким по технической сущности и достигаемому положительному эффекту является устройство, содержащее арифметический блок, выход которого соединен с , первым входом первого блока злементов И, вькцрд которого соединен со входом блока

, памяти адресов, первый выход которого соединен со входом блока памяти микроопераций, выход которого соединен со входом арифметического блока и первыми входами второго и третьего блока элементов И, вьпсод второго блока элементов И через регистр адреса возврата соединен со вторым входсшд третьего блока элементов И, выход которого соединен с первым входом счетчика команд, выход кото-, рого соединен со вторым входом второго бло10ка элементов Ни первыми входами группы блоков элементов И, .выходы которой являются

; первыми выходами устройства, а вторые входы соединены с выходами .дешифратора, вход которого соединен с выходом регистра адреса передачи управления и со входом первого элемента ИЛИ, выход которого соецинен с инверсным входом четвертого блока элементов И, прямой вход которого соединен со вторым выходом 20 блока памяти адресов, а выход - со вторым . входом счетчика команд, треЬш вход которого

: соединен с выходом нятого блока элементов И, первый вход которого соединен с вьгходом первого элемента ИЛИ, а второй вход - с вы-ходом первого блока элементов ИЛИ, выходы которого являются первыми входами устройства 2. Недостатком данного устройства является низкое быстродействие. Многопроцессорная система, в которую входит устройство, состоит из однотипных микропрограммных устройств управления, что позволяет более гибко увеличивать вычислительные мощности системь. За счет подклта ния микропрограммных устройств управления можно наращивать математическое обеспечение, т. е. увеличивать число хранимых микропрограмм и программ. Низкое быстродействие многопроцессорной системы обусловлено тем, что рационально йспопвзуется каждое микропрограммное устройство управления. Структура микропрограммного устройства такова, что выполняются все микропрограммы, в том числе и автономные. Автономными будем называть такие микропрограммы, результаты которых не зависят от результатов решений выполнений других микро программ. После выполнения всех микропрограмм управление передается на аналогичное устройство, а данное микропрограммное устройство управления не функционирует. При реалиaaipnt программы работает только одно устройство, остальные микропрограммные устройства Згщйвлення Яростаивают. При вьшолнении микр программ в данном устройстве, другие микропрограммные устройства управления не реали зуют автономные микропрограммы, и данное устройство не передает на другие микрсшрограм мные устройства управления адфеса автономных микропрограмм для их реализации. Этим обуславливается большое время простоя устройства я многопроцессорной системы в целом. Цель изобретения.- повьпиение быстродействия устройства. Поставлентая itenb достигается тем, чта в микропрограммное ус ойство управления, содержащее арифметический блок, выход которого соединен с первым входом первого блока элементов И, выход которого соединен с адресным входом блока памяти адресов, первый выход которого соединен с адресным входсям бп(жа памяти микроопёрашй, выход которого соешшш со входом арифметического блока и первыми входами второго и третьего блоков элементов И, выход второго блока элементов И через регистр адреса возврата соединен со вторым входом третьего блока элементов И, выход которого соединен с информационным входом счетчика кстанд, выход которого соединен со вторым входом второго блока элементов И и первыми входами блоков элементов И группы, вторые входы которых подключены к выходам дешифратора соответственно, выходы блоков элементов И группы являются информационными выходами устройстеа, вход дешифратора соединен с выходом регистра адреса передачи управления, выходы дешифрато-. ра подключены к входам первого элемента ИЛИ, выход которого соединен с инверсным входом четвертого блока элементов И, прямой вход которого соединен со вторым выходом блока памяти адресов, а выход четвертого блока элементов И подключен к второму информационному входу счетчика команд, третий информационный вход которого соединен с выходом пятого блока элементо1в И, первый вход которого соединен с выходом первого элемента ИЛ1 второй вход - с выходом первого блока элементов ИЛИ, входы которого подключены к первым адресным входам устройства, дополнительно введены второй и третий блоки элементов ИЛИ, регистр автономных микропрограмм, буферный регистр, шесть блоков элеменг тов И, второй элемент ИЛИ, два элемента задержки, элемент НЕ, причем выход второго блока элементов ИЛИ соединен с вторым входом первого блока элементов И, первый вход второго блока элементов ИЛИ соединен с выходом счетчика команд, второй вход - с выходом регистра автономных микропрограмм, установочный вход которого соединен с установочным входом регистра адреса передачи управления, инверсным входом шестого блока элементов И и выходом второго элемента ИЛИ, вход которого соединен с выходом первого блока элементов ИЛИ, выход шестого блока элементов И соединен с первым входом третьего блока элементов ИЛИ, второй вход которого нодаслючен к выходу седьмого блока элементов И, третей вход - к второму адресному вховходу устройства, четвертый вход - к выходу восьмого блока элементов И, выход третьего блока элементов ИЛИ соединен с информациежным входом регистра автономных микропрограмм, третий выход блока памяти соедшея с первыми входами девятого, десятого и одтшадцатого и вторым входом шестого блоков элементов И, третий вход последнего соединен с выходом первого элемента ИЛИ, четвертый вход шестого блока элементов И соединен с четвертым выходом блока памяти адресов, пятъ1Й выход которого соединен с инверсным входом десятого блока элементов И, с первым входом восьмого блока элементов И, с вторым входом одан1пашатого блока элементов И и через последовательно соединенные элемент НЕ и первый элемент задержки - с установочным входсим буферного регистра, информационный вход которого подключен к выходу одиннадцатого блока элементов И, выход буферного регистра соединен с вторым входом BociiMoro блока элементов И, третий вход которого подключен к выходу арифметического блока, шестой выход блока памяти адресов

подключен к второму входу девятого блока эпементов И, выход которого является адресным выходом устройства, выход десятого блока эпементов И соединен с информационным Ьходом регистра адреса передачи управления, выход первого элемента ИЛИ через второй элемент задержки подключен jc первому входу седьмого элемента И, второй вход которого соединен с вторым выходом блока памяти адресов.

Сущность изобретения состоит в повышении быстродействия и производительности за счет гибкого распределения выполнения автономных микропрограмм между микропрограммными устройствами управления путем выполне11ия автоиомных микропрограмм при передаче управления на другие микропрограммные устройства ; управления, а также использования результатов выполнения автономных микропрограмм другими устройствами.

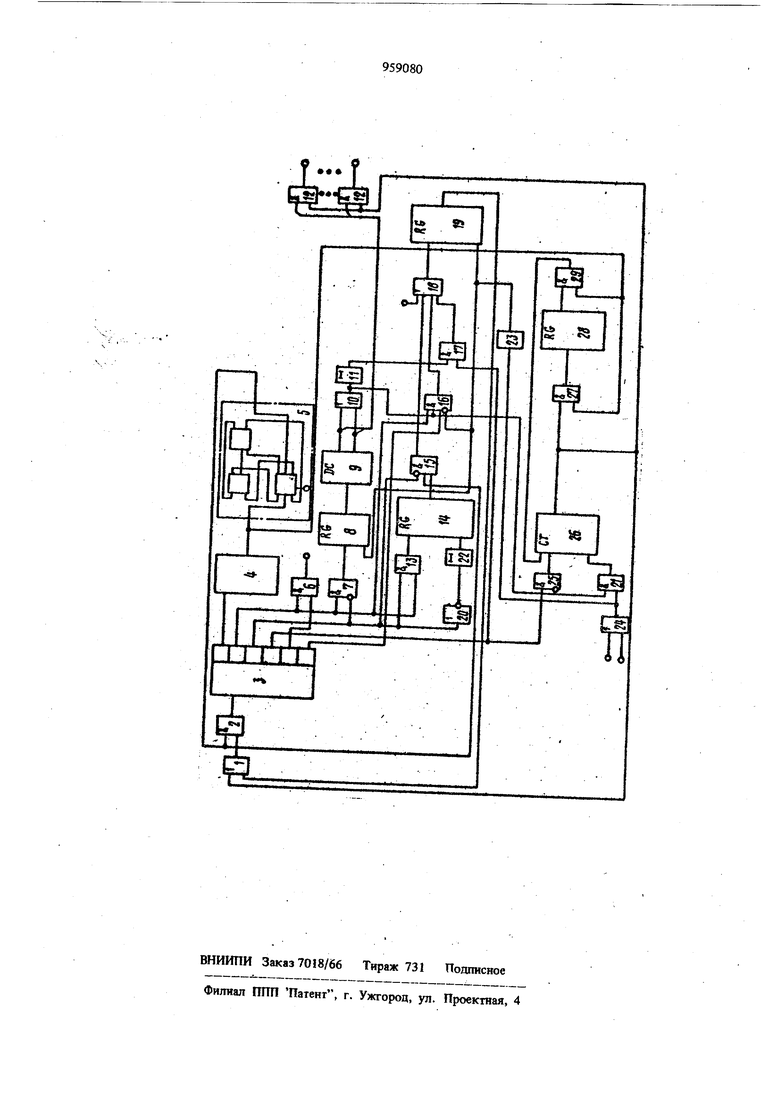

На чертеже изображена функциональная схема микропрограммного устройства управления.

Устройство содержит блок 1 элементов ИЛИ блок 2 элементов И, блок 3 памяти адресов с выходами, блок 4 памяти микроопераций, арифметический блок 5, состоящий из преобразователя кода, сумматора, блока регистров, блок 6 элементов И, блок 7 элементов И, регистр 8 адреса передачи управления, дешифратор 9, элемент ИЛИ 10, элемент 11 задержки, группа 12 блоков элементов И, блок 13 Элементов И, буферный регистр 14, блок 15 элементов И, блок 16 элементов И, блок 17 элементов И, блок 18 -элементов ИЛИ, регистр 19 автономны микропрограмм, элемент НЕ 20, блок 21 . .элементов И, элемент 22 задержки, элемент ИЛИ 23, блок 24 элементов ИЛИ, блок 25 элементов И, счетчик 26 команд, блок 27 эле. ментов И, регистр 28 адреса возврата, блок 29 элементов И.

Устройство работает в трех режимах:

, режиме выполнения микропрограммы (Т); выполнения автономной микропрограммы (11); режиме передачи адреса автономной микропрограммы на другое микропрограммное устройство управления (111).

Т режим. Счетчик 26 команд своим кодом выб1фает через блок t элементов ИЛИ и блок 2 элементов И определенные горизонтальные шины блокаЗ памяти адресов. Выбранная шина блока 3 памяти адресов выдает микрокоманду. Эта микрокоманда разбита на 6 частей: адрес операционной микрокоманды поступает в блок 4 памяти микроопераций; адрес следующей микрокоманды поступает на счетчик 26 ксяманд для выбора следующей микрокоманды; код выбора поступает в регистр 8 афеса передачи управления;. .

i Метки последней микрокоманды перед переходом к .другому устройству управления, перехода к другому устройству управления, окончания автономной микропрограммы управляют работой во втором и третьем режимах. Операционные микрокоманды поступают из блока 4 памяти микроопераций в арифметический блок 5.

i В арифметическом блоке обрабатьюается

и анализируется вся информация. Условия анализа передаются через блок 2 элементов И в блок 3 памяти адресов. По условию анализа осуществляется условный переход счетчика 26 команд на новый адрес. В другом случае осуществляется безусловный переход по адресу. Условные переходы в микропрограммном устройстве управления осуществляются с помощью анализа информации, которая преобразуется в арифметическом блоке 5. Эти условия передают.ся в блок 3 памяти адресов, из которого выбирается новый адрес в счетчике 26 команд через блок 25 элементов И, если код регистра 8 адреса передачи управления содержит нули. Этот код воздействует на блок 25 элементов И через элемент ИЛИ 10. Безусловные переходы в устройстве управления осуществляются аналогично за исключением того, что условия анализа не передаются в блок 3 памяти адресов и не влияют на выбор адреса. Для выхода на микропрограмму в микропрограммном устройстве, з правления используется регистр 28 адреса возврата, в который записываются адреса со счетчика 26 команд через блок 27 элементов И и там хранятся, пока не будет вьщолнен возврат их микропрограмм. Этот Zfspec с регистра 28 адреса : возврата пересылается.через блок 29 элементов И в счетчик 26 команд для продолжения выполнения основной микропрограммы. Если весь объем блока 3 памяти адресрв по количеству микрокоманд задействован, з нужно расишритй набор вьшолняемых программ нли микропрограмм (т. е. нарастить математическое обеспечеiffle), JO в блоке 3 памяти адресов в определенных щинах прошивается код выбора микропрограммного устройства управления который подается в регистр 8 адреса передачи управления. По этому коду осуществляется переход .к аналогичному устройству многопроцессорной снстемы. Если содержимое, регистра 8 равно нулю,; то продолжает работать данное устройство управления в соответствии с описанным алгоритмом.

При считыванни из блока 3 памяти адресов микрокоманды, предшествующей последней, на третьем выходе блока 3 памяти адресов появляеся сигнал, который разрещает запись косвенного

aдpeck автономной микропрограммы через блок 13 элементов И в i буферный регистр 14. При считывании последней микрокоманды косве1шый

; адфес автономной микропрограммы переписыва-. ется с буферного регистра 14 через бдок 15 элементов И и блок 18 элементов ИЛИ в регистр 19 автономных .микропрограмм. Код выбора с четвертого выхода блока 3 памяти адресов через блок 7 элементов И записывается в регистр 8 адреса передачи упргтлення О, при этом через элемент НЕ 20, элемент 22 задержки устанавливается в нуль буферный регистр 14. Код выбора далее поступает в дешифратор 9, где преобразуется в сигнал выбора конкретного устройства управления. Сигнал с дешифратора 9 поступает на соответствующий вход группы блоков 12 элементов И и через выбранный блок элементов И адрес со счетчика 26 команд данно микропрограммного устройства управления пере дается в счетчик команд аналогичного устройств управления. В дальнейшем работает выбранное устройство управления, которое передает на дру гие аналогичные микропрограммные устройства управления или на данное устройство управления адрес через блок 24 элементов ИЛИ и блок 21 элементов И. Сигнал с выхода элемента ИЛИ 10 поступает на блок 25 элементов И, запрещая установку . 26 комавд в новое состояние и на блок 21 элементов И, разрешая запись адреса в счетчик 26 команд с любого дрзтого устройства зшравления через блок 24 элементов ИЛИ. При этом устройство переходит в режим выполнения автономных микропрограмм. Т Г режим. Адрес автономной микропрограммы с регистра 19 автономных микропрограмм передается в блок 3.памяти адресов и далее выполняется как описано, но функций счетчика 26 команд вьтолняет регистр 19 автономных микропрограмм, блок 25 элементов И, блок 17 элементов И. При пост)тшенш1 последней микро команды автономной микропрограммы сигнал с шестого выхода блока 3 памяти адресов разрешает запись адреса новой автономной микропрограммы через блок 16 элементов И и блок 18элементов ИЛИ в регистр 19 с, четвертого выхода блока 3 памяти адресов, если нет сиг- ; нала на выходах блока 24 элементов ИЛИ. Если такой сигнал есть, то через элемент ИЛИ 23 - поступает импульс, который устанавливает . регистр ;8 адреса передачи управления и регистр 19в нуль. При этом прекращается вьшолнение автономных микропрограмм и решаются основы микропрограммы. П1 режим. При передаче функций по решению автономных микропрограмм на другие микропрограммные устройства управления сигнал на пятом вьрсоде блока 3 памяти адресов разрешает передачу косвенного адреса автономной микропрограммы через блок-6 элементов И данного устройства управлеш1я, блок. IS элементов ИЛИ в регистр автономиьа микропрограмм другого устройства управления. Подключенные микропрограммные устройства управления аналогичны предлагаемому устройству. Посредством связей этих устройств через группу блоков 12 элементов И и блок 24 элементов ИЛИ можно увеличивать количество и объем программ и микропрограмм. Формула изобретения Микропрограммное устройство управления, содержащее арифметический блок, выход которого, соединен с первым входом первого блока элементов И, выход которого соединен с адресным входом блока памяти адресов, первый выход которого соединен с адресным входом блока памяти микроопераций, выход которого соединен с входом арифметического блока и первыми входами второго и третьего блоков элементов И, , выход второго блока элемен тов И через регистр адреса возврата соединен со вторым входом третьего блока элементов И, выход которого соединен с первым информационным входом счетчика команд, выход которого соединен со вторым входом второго блока элементов И и первыми входами блоков элементов И rpyraibi, вторые входы которых подключены к выходам дешифратора соответственно, выходы блоков элементов И группы являются информационными выходами устройства, вход дешифратора соединен с выходом регистра адреса передачи управле.ия, выходы дешифратора подключены к входам первого элемента ИЛИ, выход которого соединен с инверсным входом четвертого блока элементов И, прямой вход которого соединен со вторым выходом блока памяти адресов, а выход четвертого блока элементов И подключен к второму информационному входу счетчика команд, третий информационный вход которого соединен с выходом пятого блока элементов И, первый вход которого соединен с выходом первого элемента ИЛИ, второй вход - с выходом первого блока элементов ИЛИ, входы которого подключены к первым адресным входам устройства, отдичающееся тем, что, с целью повышения быстродействия, устройство дополнительно содержит второй и третий блоки элементов ИЛИ, регистр автономных микропрограмм, буферный регистр, шесть блоков элементов И, второй элемент ИЛИ, два элемента задержки, элемент НЕ, причем выкод второго блока элементов ИЛИ соединен с вторым входом первого блока элементов И, первый вход второго блока элементов ИЛИ соединен с выходом счетчика команд, второй вход - с выходом регистра автоном1П)1х микропрограмм, установочный вход которого соединен с установочным входом регистра адреса

передачи управления, инверсным входом шесттого блока элементов И и выходом второго элемента ИЛИ, вход которого соединен с вы ходом первого блока элементов ИЛИ, выход UiecToro блока элементов И соединен с первым входом третьего блока элементов ИЛИ, второй вход которого подключен к выходу седьмого блока элементов И, третий вход - к второму адресному входу устройства, четвертый вход к выходу восьмого блока элемекгов И, выход третьего блока элементов ИЛИ (М)единен с информационным входом регистра автожмных микропрограмм, третий выход блока памяти адресов соединен с первыми входами девятого, десятого, одиннадцатого и вторым входом шеетого блоков элементов И, третий вход последнега соединен с выходом первого элемента ИЛИ четвертый вход шестого блока элементов И соединен с четвертым выходом блока памяти адресов, пятый выход которого соединен с инверсным входом десятого блока элементов И, с первым входом восьмого блока элементов И, с вторым входом одиннадцатого блока элементов И и через последовательно соединенные

элемент НЕ к первый элемент задержки с установочным входом буферного регистра, информационный вход которого подключен к выходу одиннадцатого блока элементов И, выход буферного регистра соединен с вторым входом восьмого блока элементов И, третий вход которого подключен к выходу арифметического блока, шестой выход блока памяти адресов подключен к второму входу девятого блока .элементов И, выход которого является адресным выходом устройства, выход десятого блока элементов И соединен с информационным входом регистра адреса передачи управления, выход первого элемента ИЛИ Через второй элемент задержки подключен к первому входу седьмого блока эле ментов И, второй вход которого соединен с вторым выходом блока памяти адресов.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1982-09-15—Публикация

1980-12-08—Подача