(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СВЯЗИ ДЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| Двухканальное устройство для ввода информации | 1985 |

|

SU1285453A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Стековое запоминающее устройство | 1979 |

|

SU881863A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

Изобретение относится к вычисли-тельной технике, предяазначенб для осуществления взаимосвязи модулей вычислительной системы и может быть использовано .при создании вычисли-тельных систем.

Известно устоойство связи шин, содержащее набор пассивных шин, соединенных двусторонними, связями с модулями вычислительной системы, блоки управления шинами и блок связи 111.

Известно также устройство связи, содержащее набор пассивных шин д 1нных, адреса ,и управления, соединенных - . двусторонними связями с модулями вычислительной систелш, при этом передачи информации между модулями выполняются в режиме разделения времениf2i.

Недостатками этих устройств является то,что для всех потоков информации имеется только один путь .Это приводит к недопустимо большому времени ожидания при «обмене данными по мере расширения вычислительной Ьистеки.

Наиболее близким к изобретению по технической сущности и дрстиг-аемому результату является устройство связи, содержащее, группу адаптеров, группу блоков памяти и блок синхронизации, первые входы-йыходы адаптеррв являются первыми входами-выходами устройства, а йторые входывыходы адаптеров - вторыми входалш-вшсодами устройства, первый выход блока синхронизации соединен с nepBHNBi входами адаптеров группы и перовыми управ ля юссими входами блоков памяти группы, второй выход блока

10 синхронизации соединен с вторыми управляющими входами блоков памяти группы, выход каждого предыдущего блока памяти группы соединен с информационным входом каждого последующего блока-памяти группы и вторым входом соответствующего адаптера группы, первый сигнальный вход каждого блока памяти группы подключен к первому ВЫХОДУ соответствующего адаптера группы, а второй сигналь20шли вход каждого блока, памяти группы подключен к второму выходу соответствующего адаптера группы Гз.

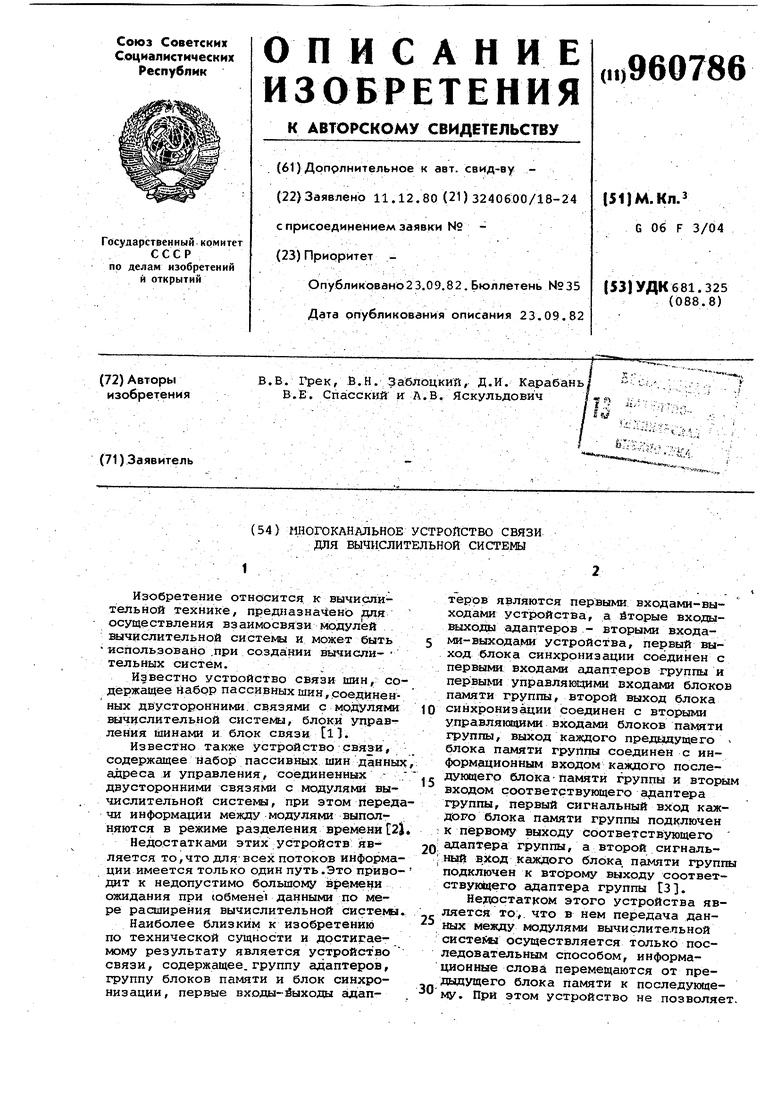

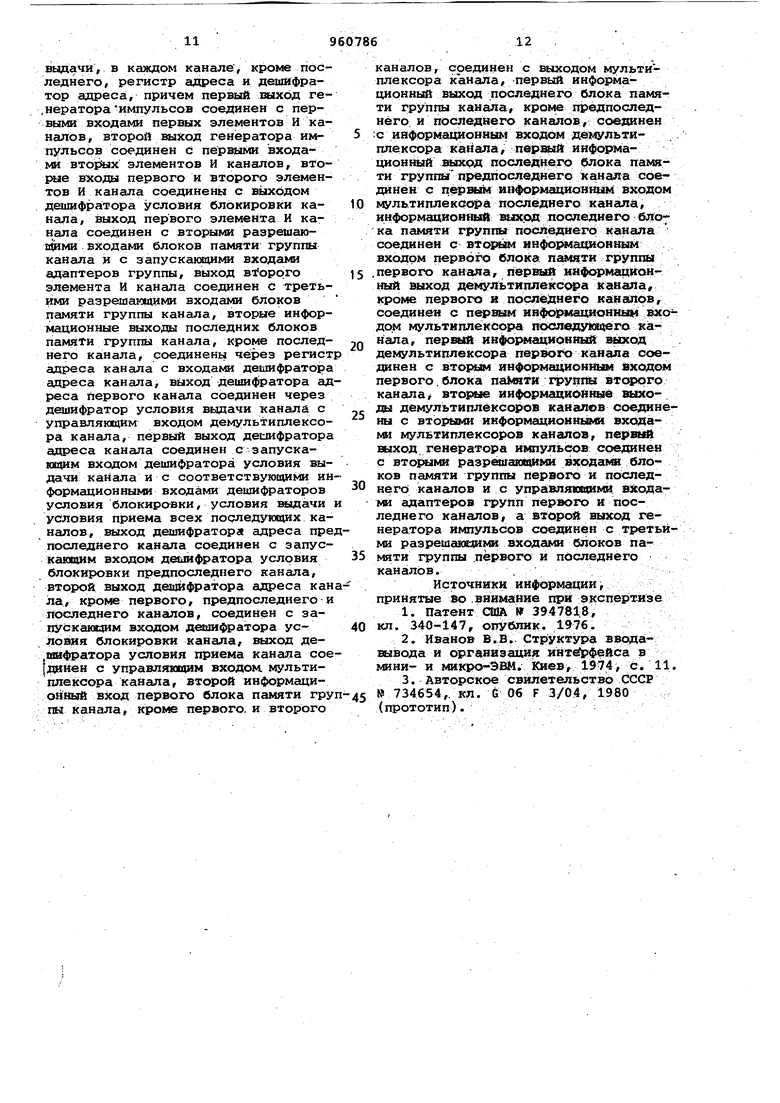

Недостатком этого устройства являетсй то,, что в нем передача дан25ных между модулями вычислите.пьной системы осуществляется только последовательным способом, информационные слова перемещаются от предыдущего блока памяти к последующе30му. При этом устройство не позволяет. производить ускоренную передачу данных группами модулей вычис лительной системы, которые больший -приоритет, что особенно необходимо при функциональной специализации различных групи модулей вычислительной системы. Это приводит к снижению быстродействия устройства и уменьшения обцей производительностичсистемы... Цель изобретения - пошзшение быст родействия. . Поставленная цель достигается ,тем, что в многоканальное устройство связи для вычислительной системы, содержащее генератор импульсов, а в каждом канале - группу блоков памяти и группу адаптеров, причем выход каждого блока группы блоков Пс1мяти канала соединен с первым информационным входом последующего бло ка памяти этой группы канала, выход блока группы блоков памяти канала соединен .с информещионным входом соответствующего адаптера группы адаптеров канала, информащионный и заданхднй адаптера группы адап теров канала соединены соответственно с ВТО1ШМ информационным и nepraiiM разрешающим входами соответствующего блока группы блоков памяти канала, sntIpaвляющий вход-дыход адаптера канала является соответствующим входом-выходом группы управляющих входов-выходов канала, информационный вход-выход адаптера канала является соответствующим входом-выходом группы информационгалх входов-выходов канала, в каждый канал кроме первого и последнего, введены первый и второ элементы И и дешифратор условия блокировки, в каждый канал, кроме, первого и второго, введены муль,типлексор и дешифратор условия приема, в каждый канал, кроме предпоследнего и последнего, введены демуль типлексор и дешифратор условия выдачи, в каждый канал, кроме последнего, введены регистр адреса и дешифратор адреса, причем первый выход генератора импульсов соединен с первыми входами первых элементов И кана лов, второй выход генератора импульсов соединен с первыми входами вторых элементов И каналов, вторые входы первого и второго элементов И канала соединены с выходе дешифратора условия блокировки канала, выход первого элемента И канала соединен с вторыми разрешаювтьга входами блоков группы блоков памяти канала и с зап ускакадикш входами адаптеров канала, выход второго элемента И канала соединен с третьими разрешгиощи ми входами блоков группы блоков памя ти канала, информационные выходы последнего блока группы блоков памяти канала, кроме поеледнего какала, соединены через регистр адреса канала со входакш дшлшфратора адреса канала, выход дшшфратора адреса первого канала соединен через дешифратор усло1з11я вслдачи канала с у правлякццим входом jcteMjrnbtH плексора какала, выхрл.даввифратора адреса канала соёдаяея с э пускакздим входом дшшфратора ус яоВИЯ канала и с сою1тветствуювб1ми ииформшдион оАш вхояцат раторов условия блокировок/ у повия выдачи и уйяопня приеме всех прследукедих каналов, jE|eintt$pa тора адреса npefmocaeUgs tft каваяа соединен с запускакицим входом is BOf dTopa условия блокз11Ювк11 пред- последнего каиала, второй вшеод неишфратора адреса канаяа, крш«е первого,. предпоследнего и последнего каналов, соединен с эапускальдам входом де9Е1ШфраТ( услови блокировки канала, выход центратора хслбвия приема канала соедшнеи с управляаш м входс мультиплексора канала/ второй . информационный вход nepBot o блока группы блоков п&мятя канала, кроме первого и втсфого каналов, с К1ХОДОМ мультиплексора .канала, первый информациоктйЕй выход последнего блока группы блоков памяти канала, последнего и предпоследнего канаЛов, соединен с ннформациотшм входам дeмyльтиnЛekcppa канала, первый информационный последнего блока груптш блоков памяти предпоследнее го канЕШа соединен с первым информационным входом мультиплексора последнего канала, информационный выход последнего бЛока группы блоков памяти последнего канала соединен с вторым информационным входом первого блока группы блоков памяти первого канала, первый информационный выход демультиплексора канала, кроме первого и последнего каналов, соединен .с первым информационным входом мультиплексора последующего каНсша, перга:1й информационный выход демультиплексора первого канала соединен с вторым информгщионным входом первого блока группы блоков памяти второго кангша, вторые информёщионтл& sttxona демультиплексоров каналов соединены с вторыми информационными входа а1 мультиплексоров каналов, первый выход генератора импульсов соединен с вторшми разрешаюцимн входами блоков групп блоков памяти первого и последнего каналов и с у1фавля10 | |ими входами адаптеров Прупп гщаптеров первого и последнего каналов, второй Я1ход генератора икшульсов соввяннен с третьими раз;;;Р0ша«№имя входами блоков группы блоков памяти первого и последнего каналов. На фиг. 1 приведена струкТ5 рная схема устройства на фиг. 2 - то

же, блока памяти и адаптера; на ,1фиг, 3 - то же блока управления; на фиг. 4 - то же, блока коммутации. : . .. :, ./.

Устройство связи для вычислительной системы содержит (фиг.. 1) каналы первый 1, второй 2, третий 3, предпоследний 4, предпоследний 5 и последний 6. Камсдай из каналов осздержит регистр 7 адреса/ дешифратор ;5 условия вьвдачи, дешифратор 9 условия приема, дешифратор :10 условия блокировки, дешифратор 11 адрееа элементы И 12 и 13, модули 14 ны числительной систему, генератор 15 импульсов. Кроме того/ каналы устjpoftcTBa содержат группу блоков 16 1И 17 памяти, группу адаптеров 18 и (19, демультйпленсор 20, мультиплексо ,21, входил-выходы 22,. составляицие группу управляквдих входов-выходов канйла входы-выходы 23, с:оста;вляювде группу информационных входоввыходов канала.

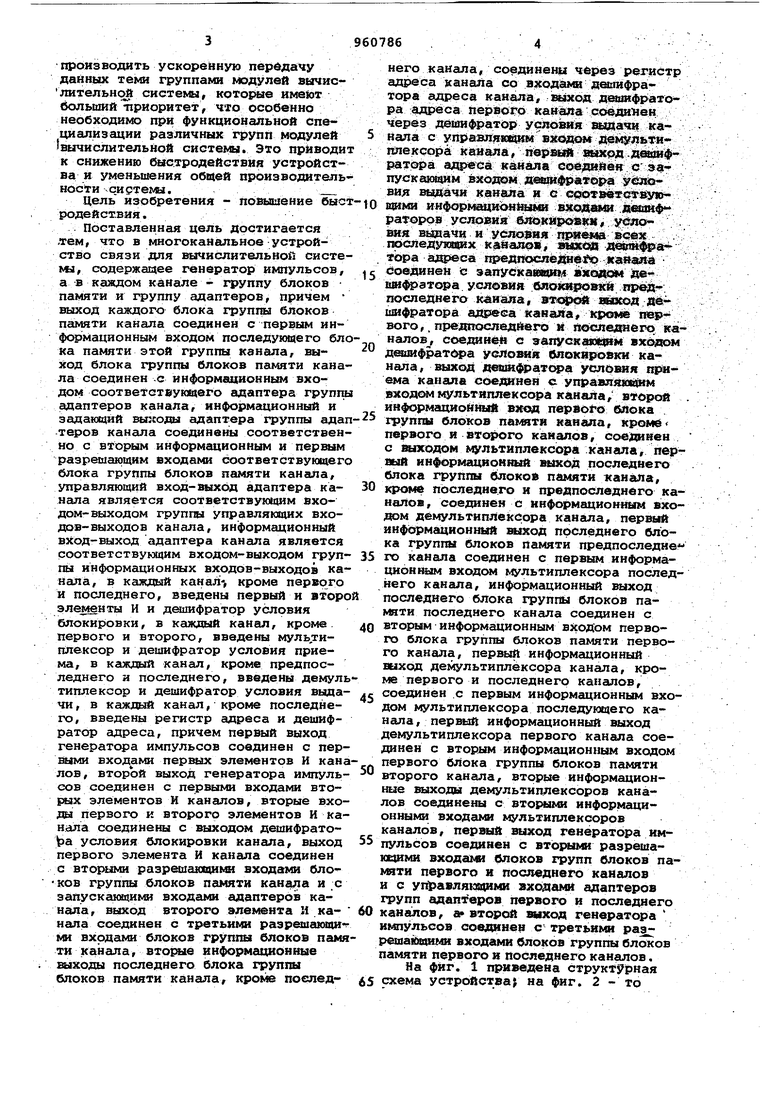

Блок памяти содержит (фиг. 2 приешый регистр 24, элемент ИЛИ 25, пвр1едакяций регистр 26, а адаптер содержит блок 27 управления, буферный регистр 28, блок 29 сравнения.

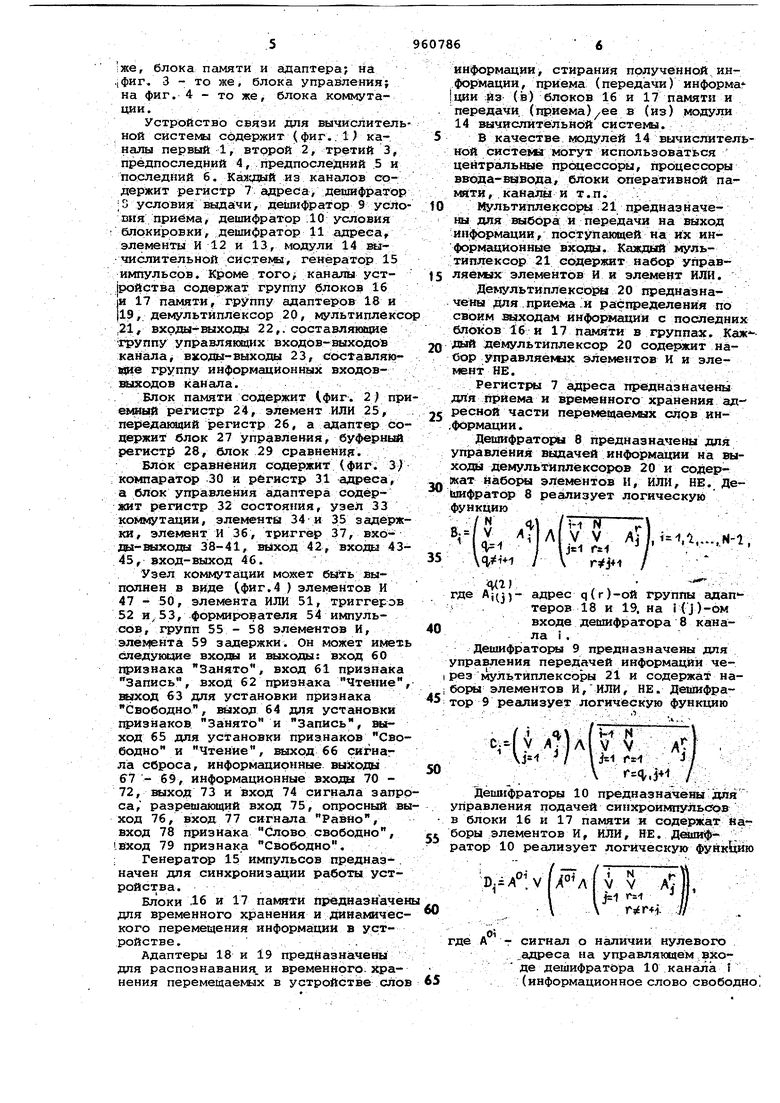

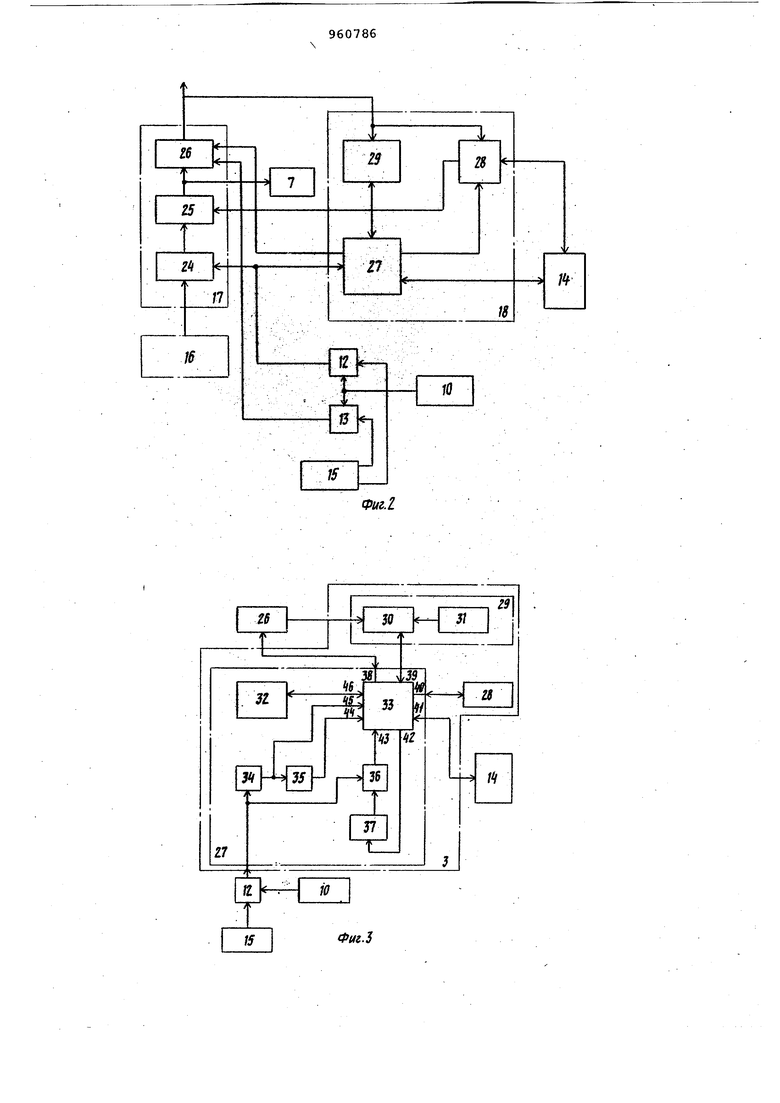

Блок сравнения содержит (фиг. 3) компаратор 30 и регистр 31 адреса, а блок управяения йдаптера содержит регистр 32 состояния, узел 33 коммутации, элементы 34-и 35 задержки, элемент И 36, триггер 37, вхЬдд-выходы 38-41, выход 42, входа 4345, вход-выход 46.

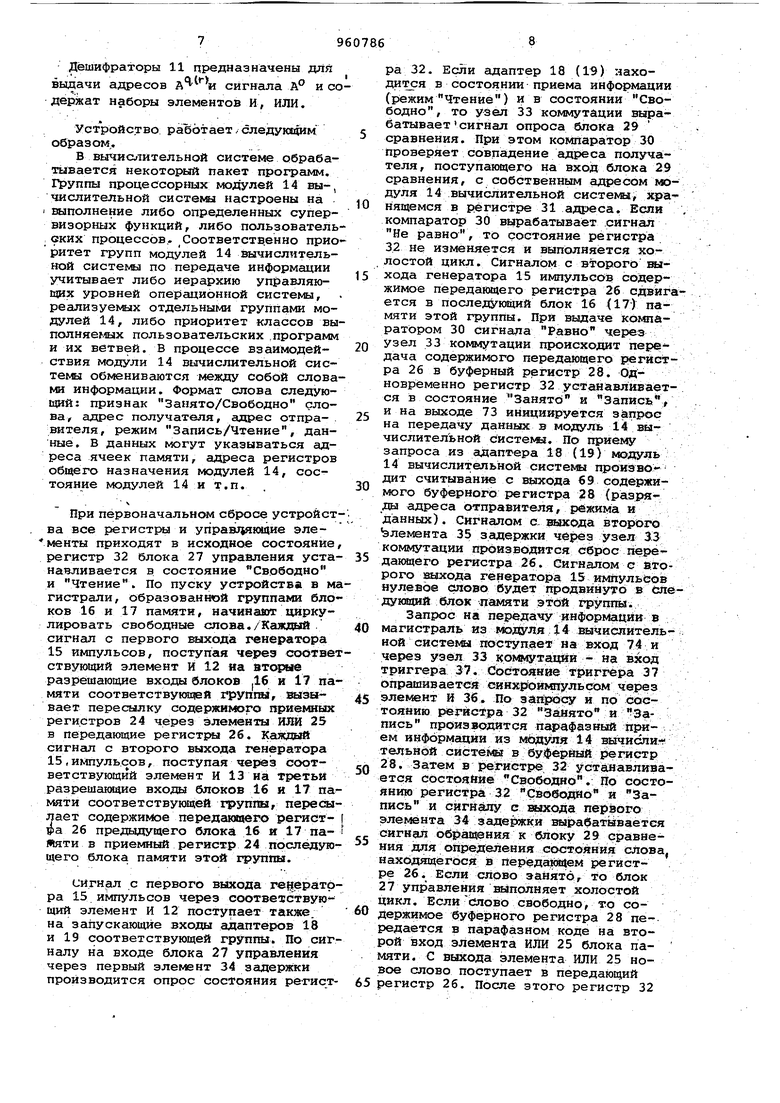

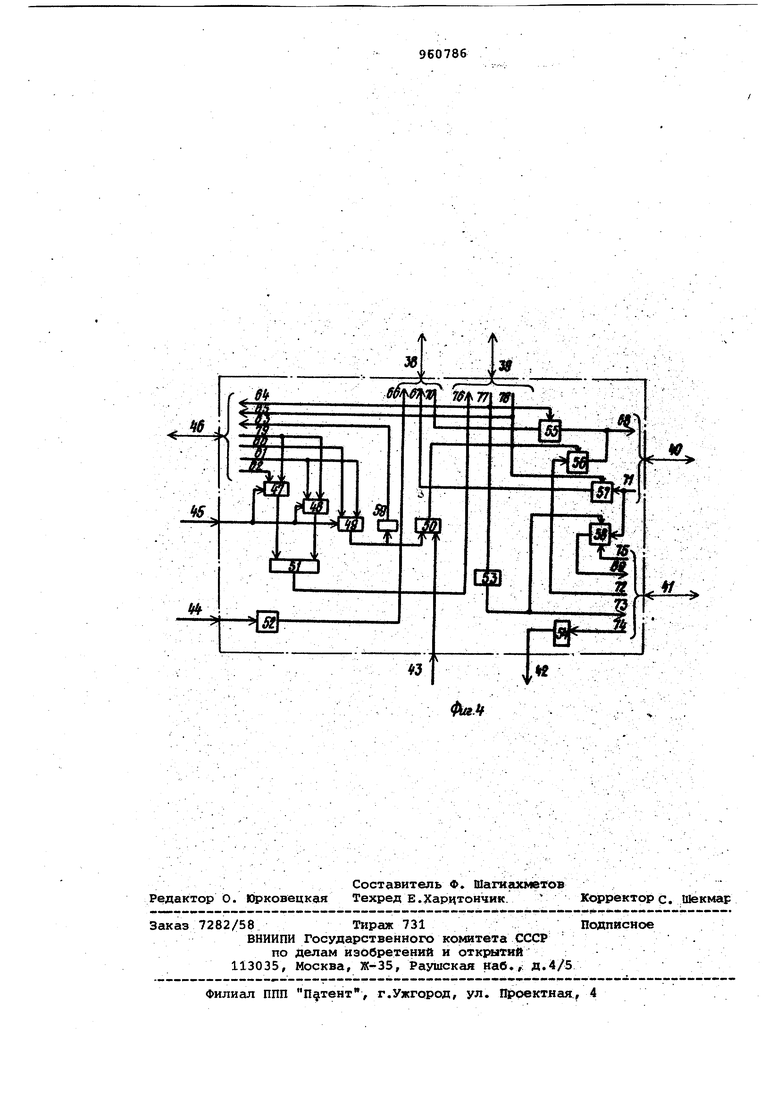

Узел коммутации может быть выполнен в виде ЧФИГ.4 ) злектентов И 47 - 50, ИЛИ 51, триггеров 52 , формирователя 54 импульсов, групп 55 - 58 элементов И, элемента 59 задержки. Он может иметь спедуюсдие вхолк и выходы: вход 60 признака Занято, вход 61 признака Запись, вход 62 признака Чтение, выход 63 для установки признака Свободно, выход 64 для установки признаков Занято и Запись, кигход 65 для установки признаков Свободно и Чтение, Кагход 66 сигнаг ла сброса, информационные выходы - 69, информационные входы 70 72, клход 73 и Вход 74 сигнала запроса, разрешающий вход 75, опросный выход 76, вход 77 сигнала Равно, вход 78 признака Слово свободно, ВХОД 79 признака Свободно. ; Генератор 15 импульсов преднаэ-. начен для синхронизации работы устройства.

Блоки .16 и 17 памяти йреднаэначен для временного хранения и динамического перемещения информации в устройстве.

Адаптеры 18 и 19 предназначены для распознавания, и временного Хранения перемещаемых в устройстве слов

информации, стирания полученной информации , приема (передачи) информа дай из (в) блоков 16 и 17 памяти и передачи (приема)уее в (из) модули 14 вычисуттельнбй системы.

В качестве модулей 14 вычислительной система могут использоваться центральные прсвдессоры, процессоры ввбда-ВЕавода, блоки оперативной памяти,,1саналы и т.п. ;

Мультишзексрра 21, пpeднaзнa:чeны для выбора: и передачи на выход информации, поступающей на их инФор14гщйонные входы. Каждый мультиплексор 21 содержит набор управляемых элементов И и элемент ИЛИ.

Демультиплексс ры 20 предназначены для. приема, и распределения по своим а: ходам информации с последних блоков 16 и 17 памяти в группах. Viax ДЕЛИ демультйплексор 20 н4бор управляемых элементов И и элемент- НЕ.

Регистры 7 адреса предназначены для приема и временного хранения адресной части перемещаемых сэдов ин.ФЬрмации.

Дешифраторы 8 предназначены для управления ввдачейинфо рмш{ии на выхода демультиплексоров 20 и содер;вкат наборы элементов И, ИЛИ, НЕ. Дешифратор 8 реализует логическук)

функцию . J : . .

.

q, / j+ /

4(гг. . . -,-; ,:

где А цj)- адрес q(г)-ой группы адап теров 18 и 19. на i(j)-OM входе дешифратора 8 канала i .

Дешифраторы 9 предназначены для управления передачей информации через мультиплексоры 21 и содержат набоЕ« элементов И,ИЛИ, НЕ. Деиифратор 9 реализует логическую функцию

;(Жл nri; At

I ГИ J

л ,l

50 Дешифраторы 10 предназначены для управления подачей сипхроимгг1шься в в блоки 16 и 17 памяти и содерз ат йа55 боры элементов И, ИЛИ, НЕ. ; ратор 10 реализует логическую функцию

D.A°:V(

60

А г сигнал о наличии нулевого

.адреса на управляющем дхо де дешифратора 10 канала Г (информационное слово свободно Дешифраторы 11 предназначены для выдачи адресов сигнала А° и со flepkai наборы элементов И, ИЛИ. Устройство работает/следукишм образом,. В вычиа/тительной системе обрабатывается некотоЕИй пакет программ. Группы процессорных модулей 14 вы-, числительной системы настроены на I выполнение либо определенных супервизорных функций, либо пользователь :ских процессов. Соответственно прио ритет групп модулей 14 вычислительной системы по передаче информации учитывает либо иерархию управляющих уровней операционной систеки, реализуемых отдельными группами модулей 14, либо приоритет классов вы полняе 4ых пользовательских .программ и их ветвей. В процессе взаимодействия модули 14 вычислительной системы обмениваются между собой слова ми информации. Формат слова следующий: признак Занято/Свободно слова/ адрес получателя, адрес отправителя, режим Запись/Чтение, данные. В данных могут указываться адреса ячеек памяти, адреса регистров общего назначения модулей 14, состояние модулей 14 и т.п. При первоначальном сбросе устроЙст ва все регистры и упраш яющив элементы приходят в исходное состояние регистр 32 блока 27 управления уста навливается в состояние Свободно и Чтение. По пуску устройства в м гистрали. Образованной группами бло ков 16 и 17 памяти, начинают циркулировать свободные слова./Каждый сигнал с первого выхода генератора 15 импульсов, поступая через соотве ствующий элемент И 12 на вторые разрешающие входы блоков ,16 и 17 па мяти соответствующей группа, вызывает пересылку содержимого приемных регистров 24 через элементы ИЛИ 25 в передающие регист1жа 26. Каждый сигнал с второго выхода генератора 15,импульсов, поступая соответствующий элемент И 13 иа третьи разрешанидие входы блоков 16 и 17 па мяти соответствующей группы, пересы лает содержи эе передаквдего региетВ а 26 предыдущего блока 16 и 17 паЛяти в приемный регистр 24 последую щего блока памяти этой группы. Сигнал с первого выхода ге||ератр ра 15 импульсов через соотвегЕСтвук} щий элемент И 12 поступает также, на запускающие входы адаптеров 18 и 19 соответствующей группы. По сиг налу на входе блока 27 управления через первый элемент 34 задержки производится опрос состояния ре-гист ра 32. Если адаптер 18 (1Э) находится в состоянии приема информации ( Чтение) ив состоянии Свободно, то узел 33 коммутации вырабатывает сигнал опроса блока 29 сравнения. При этом комйаратор 30 проверяет совпадение адреса получа:теля, поступающего на вход блока 29 сравнения, с собственным адресом модуля 14 вычислительной систеьжа, нящемся в регистре 31 адреса. Если , компаратор 30 вырабатывает сигнал Не равно, то состояние регистра 32 не изменяется и выполняется холостой цикл. Сигнё1лом с второго выхода генератора 15 импульсов содержимое передающего регистра 26 сдвигается в послегб юЩий блок 16 (17) памяти этой группы. При выдаче компаратором 30 сигнала Равно через узел 33 коммутации происходит передача содержимого передающего регистра 26 в буферный регистр 28. Одновременно регистр 32 устанавливается в состояние Занято и Запись, и на выходе 73 инициируется запрос на передачу данных в модуль 14 вычислительной систелвд. По приему запроса из адаптера 18 (19) квэдуль 14 вычислительной системы производит считывание с вь1хОда 69 содержимого буферного регистра 28 (разряды адреса отправителя, режима и данных). Сигналом с тагходд вторОгю Элемента 35 задержки через узел 33 коммутации производится сброс передающего регистра 26. Сигналом с йторого Ш4хода генератора 15 импуль зов нулевое ешоео будет продвинуто в сяедукадий блок памяти ЭТОЙ . Запрос на передачу инфор1 цйи в магистраль из Мойуля 14 Вычиснительной системы поступает на вход 74 и через узел 33 ко «У1утацйй. на вход триггера 37. Сосгтояние триггера 37 опрашиваете синхроймйульсом через элемент и 36, По зайросу и по сбетояйию регистра 32 Заиято и Запись производится ггар фазный прием информации из модуля 14 вычисли тельной систёлй в буферйый гистр 28, Затем в регистре 32 уст9-Н«1вливается состояййе Свободно. Йо состоянию регистра 32 Свободйо и Запись и сигналу с выхода первого элемента 34 з с1держк;и таарабатывается сигнал обращения к блоку 29 сравнения для определения состоян ия слов а, нахОдящёгосй в переда1 с«4ем регистре 26. Если слово эаня;т6, то блок 27 управления выполняет холостой цикл. Если Ьлово свободно, то содержимое буферного регистра 28 передается в парафазном коде на второй вход элемента ИЛИ 25 блока памяти. С выхода элемента ИЛИ 25 новое слово поступает в передающий регистр 26. После этого регистр 32

переводится в состояние Свободно и Чтение,

Обмен информацией между модулями

14различных групп производится следую11дам образом.

При передаче информационного слова КЗ приемного регкстра 24 в передеааш регистр 26 с выхода элемента ИЛИ 25 последиего блока 17 памя, ти в д анной группе снимается в пар Фазном коде адрес получателя и эаносит я в регистр 7 адфеса. Адрес получателя рааш1{фровывается д&з нфратс ом 11, определяющим номер груп-щ в которой находится мод1уль 14 получателя, На информационных вхо.jEtax каждюго деши Фратора 10 канала i совираются адреса обравдемий от всех предьйущих j -ых групп (j i)k

. (1,.. .jj , i +2,;.., N)-ым группам, Кроме того, на запускающий вход кажfyolpo двойфратора 10 канала I поступает сипгал о состоянии информационного слова (Занято / Свободно) в переданяцем регистре 26 последнего блока 17 памяти {jH)-oй группы. Если слово занято и есть обращения в предагяуютх j -ых группах k (1,..., j, ,,.. ,)-ым группам, то-на выходе д ияфратора 10 канала появляется сигнал блокировки синхроимпул сав, KOTO|%ie йоступагот с генератора

15и ЁrIyльcoв на разрешающие входы блоков 16 и 17 памяти и на запусканицие входда адаптеров 18 и 19 данной грунта). Таким образом, блокируется передача слова из менее приоритет№ОЛ группы (группы с большим номером) и освобождается первый блок 16 памяти в Группе, в которую пересылается слово информации из передакицего 26 последнего блока 17 памяти более приоритетной группы (группы с меньшим номером). Если последний блок 17 памяти менее приор|итётной свободен, то блокировка этой группы не производится

и происходит сдвиг информации внутри этой группы.

Управление к шачей информации через демультиплексоры 20 реализуют дёшифрато Н:1 8, выдача информаЦИ1И из последнего блока 17 памяти дайной группы разрешается только в том случае, если нет выдачи информации из групп с большим приоритете. В противном случае информация пересаылается через мультиплексор 21 в перилй блок 16 памяти следующей груптаа

Управление приемом информации через мультиплексоры 21 реализуют дешифраторы 9. Прием информации в первый блок 16 памяти данной группы разрешается только при передаче слова с адресом получателя, модуль 14 которого находится в данной; группе, Если слово пересылается из j-ой

группы в (1, 2,,..,3)-ую группу, то оно принимается сначгша в последнюю, N-ую rpyntiy и сдвигается дальше в первую группу.

Устройство обладает повшаенным

быстродействием за счет того, что кроме последовательной пересылки информации по магистрали организуется непосредственный обмен информаци- . ей между группами, в которые объединены блоки памяти, минуя модулей с промежуточными адресами, пусть, например, в устройстве имеется N групп блоков памяти по п блоJCOB в каждой группе, цикл передачи

информации 4eждy скюжными блоками памят,и равен- Т. Тогда можно оценить максимальное увеличение быстродействия по сравнению с известным устройством -при передаче слова , например, от первого блока памяти первой ppyiiпы, к последнему блоку N-ой труппы;

fltftt N

. Кроме того, предлагаемое 2гп 1 устройство позволяет повысить обадую

производительность системы за счет скоренной передачи данных по магистрали теня группами модулей вычислительной системы, которые имеют больший приоритет (меньший номер).

30

Формула изобретения

Многоканальное устройство связи для вычислительной системы, содержащее генератор импульсов,, а в каждом канале - группу блоков памяти и группу адаптеров, причем выход каждого блока памяти группы соединен с первым информациойным входом

последующего блока памяти этой группы канала, выход каждого блока памяти группы соединен с информациондаш входом соответствующего адаптер а группы адаптеров канала, информацИон;Ный и задающий выходы адаптеров группы соединены соответственно с информационным и первым разрешающим входами соответствующего блока памяти группы, управляющий вход-га ход

адаптера канала является соответст50

вующим входом-выходом группы управляющих входов- выходов канала, информационный вход-га :ход адаптера канала является соответствумщим входом-выходом группы информационных

55 входов-выходов канала, отличающееся тем, что, с целью повышения стродействия, оно содержит в каждом канале, кроме первого и последнего, пережди и второй элементы

60 и и дешифратор условия блокировки, в каждом канале, кроме первого и второго, мультиплексор и дешифратор условия приема, в каждом канале, кроме предпоследнего и последнего, дему65 льтиплексор и дешифратор условия Выдачи, в каждом канале, кроме последнего, регистр адреса и дешифратор адреса, причем первый хзыход ге.нератораимпульсов соединен с первыми входами первых элементов И каналов, второй выход генератора импульсов соединен с первыкда входами элементов И каналов, втоptte входы первого и второго элементов И канала соединены с выходом дешифратора условия блокировки канала, выход первого элемента И канала соединен с вторыми раэрешаю11|йми входами блоков памяти группы канала и с запускающими входсши адаптеров группы, выход второго элемента И канала соединен с третьими разрешаюишми входами блоков памяти группы канала, вторые информационные выходы последних блоков памяти группы канала, кроме последнего канала, соединены через регист адреса канала с входами дешифратора адреса канала, выход дешифратора ад реса первого канала соединен через дешифратор условия выдачи канала с управляющим входом демультиплексора канала, первый выход деьшфратора адреса канала соединен с запускаюошм входом дешифратора условия выдачи канала и с соответствующими ин формационными входами дешифраторов условия блокировки, условия выдачи условия приема всех последующих каналов, выход дешифратора адреса пре последнего канала соединен с запускающим входом дешифратора условия блокировки предпоследнего канала, второй выход дешифратора адреса кан ла, кроме первого, предпоследнего и последнего каналов, соединен с запускаккоим входом дешифратора усЛовия блокировки канала, выход де.шифратора условия приема канала сое динен с управляхжоим входом, мультиплексора канала, информационный вход первого блока памяти ГРУ пы: канала, кроме первого, и второго каналов, соединен с выходом мультигшексора канала, первый информационный выход последнего блока памяти группы канала, кроме предпоследнего и последнего каналов, соединен :синформационнь 1 входом демультиплексора кайала, перадй инфорвлационный ашод посдед1|е го блока памяти группы предпосяеднего xaiHctjia соединён с И1}формационшц4 входом мультиплекссфа последнего каналаj информацйойй|:Ш вшс;ОД поспеднехх) бло ка памяти груши посйеднегс) канала соединен с инфоЕ 1 онным входом первого блока пам«(ти групшл первого KaHcpia, первый информационный шдход демультиплексс а канаязг кроме первого и последнего каналов, соединен с ияф мащ{ 7Н1{нм входам мультиплексора яоспщ(УК(щего канала, перв&ш информационный выход демультиплексора первого канала соединен с ВТОР1ЛМ информационшш входом первого.блока пайяти : группы втсфрго канала, ииформациойныё выхо-, ды демультиплексоров каналов соеданены с вторыми информациОнньши входа вI мультиплексоров каналов, первк выход генератора И1«1ульсов соединен С втарымк разрешающими вХодакШ блоков памяти группы первого и последнего каналов и с упра1вля1011(имй в кодами адаптеров групп первого и последнего каналов, а второй выход генератора импульсов соединен с третьими разрешсшждами входами блоков памят: : группы .первого и последнего каналов.. Источники информации, принятые во .внимание щ)и эксперт-Изе 1.Патент США 3947818, кл. 340-147, опублик. . 2.Иванов В.В. Структуру вводавывода и организация в мини- и микро-ЭВМ. Киев, 1974, С. 11. 3.Авторское свилетельство СССР № 734654,. кл. G 06 F 3/04, 1980 (прототип).

:

Авторы

Даты

1982-09-23—Публикация

1980-12-11—Подача