4 4 Фь

;0 о

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Преобразователь кодов с иррациональным положительным основанием в коды с иррациональным отрицательным основанием | 1988 |

|

SU1566486A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907795A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Устройство для умножения | 1987 |

|

SU1444751A1 |

| Устройство для вычисления остатка по модулю 2 @ +1 | 1990 |

|

SU1734212A1 |

Изобретение относится к области вычислительной техники и может быть использовано для сопряжения устройств, функционирующих в фибоначчиевых кодах, например высокочастотных аналого-цифровых преобразователей, с устройствами, функционирующими в модулярном коде, например, высокопроизводительными процессорами. Цель изобретения - расширение области применения за счет возможности преобразования фибоначчиевого кода в модулярный код. Поставленная, цель достигается тем, что преобразователь чис ла в модулярный код, содержащий бло1 1 элементов И, сумматор 2 по модулю, накапливающий сумматор 3 по модулю, регистр 4 сдвига, блок 6 синхрониза- ции, содержит регистр 5 сдвига с соответствующими связями. 2 ил. с S (Л

7 в

(рчгЛ

Изобретение относится к вычислительной технике и может быть использовано для сопряжения устройств, функционирующих в фибоначчиевом коде, например, высокоточных аналого- цифровых преобразователей, с устройствами функционирующими в модулярных кодах, например, высокопроизводительными и высоконадежными процессорами,

Цель изобретения - расширение области применения за счет возможности преобразования фибоначчиевого кода в модулярный код.

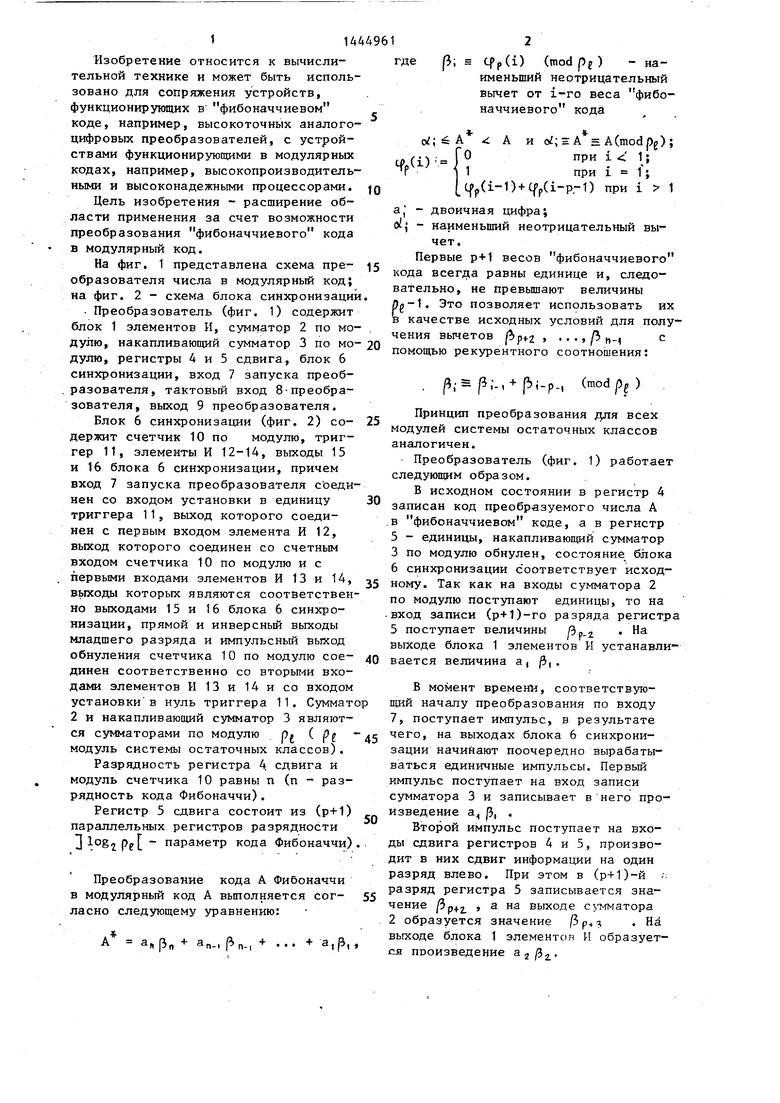

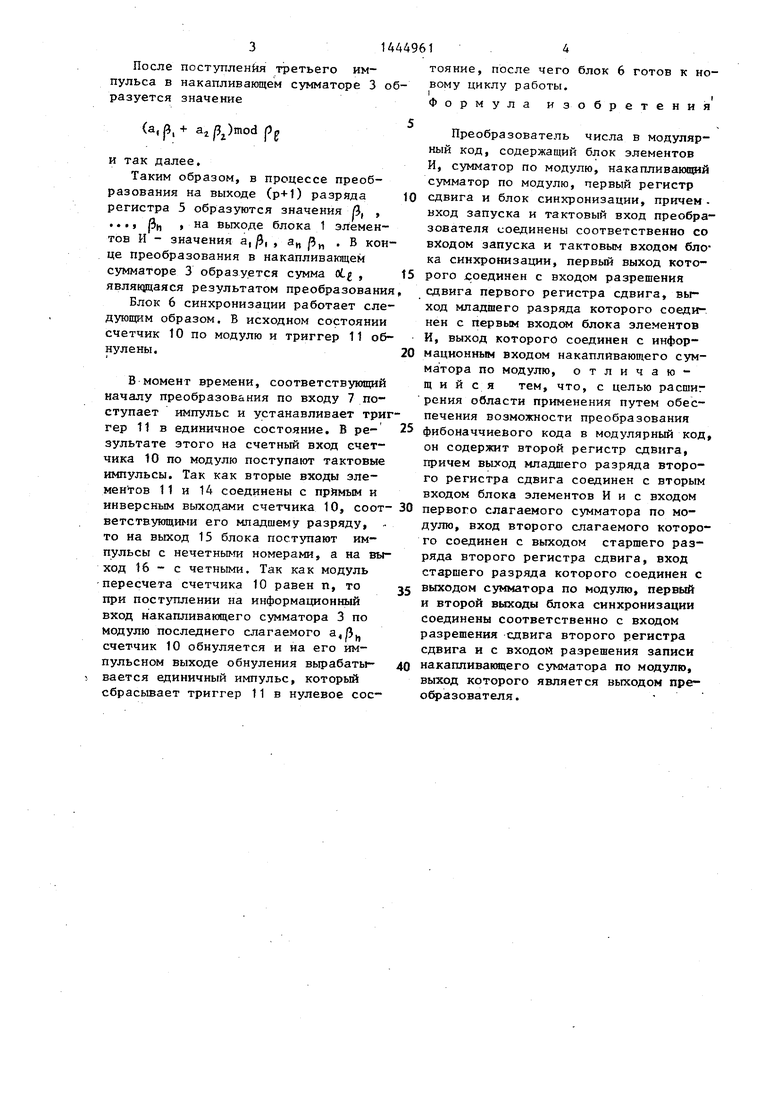

На фиг. 1 представлена схема пре- образователя числа в модулярный код; на фиг. 2 - схема блока синхронизации

Преобразователь (фиг. 1) содержит блок 1 элементов И, сумматор 2 по мо- дулю, накапливающий сумматор 3 по мо- дулю, регистры 4 и 5 сдвига, блок 6 синхронизации, вход 7 запуска преобразователя, тактовый вход 8-преобразователя, выход 9 преобразователя.

Блок 6 синхронизации (фиг. 2) со- держит счетчик 10 по модулю, триггер 11, элементы И 12-14, выходы 15 и 16 блока 6 синхронизации, причем вход 7 запуска преобразователя с оеди- нен со входом установки в единицу триггера 11, выход которого соединен с первым входом элемента И 12, выход которого соединен со счетным входом счетчика 10 по модулю и с первыми входами элементов И 13 и 14, вьпсоды которых являются соответственно выходами 15 и 16 блока 6 синхронизации, прямой и инверсный выходы младшего разряда и импульсный выход обнуления счетчика 10 по модулю сое- динен соответственно со вторыми входами элементов И 13 и 14 и со входом установки в нуль триггера 11. Суммат 2 и накапливающий cyi iaTOp 3 являются сумматорами по модулю . Pj ( pf модуль системы остаточных классов).

Разрадность регистра 4 сдвига и модуль счетчика 10 равны п (п - разрядность кода Фибоначчи).

Регистр 5 сдвига состоит из (р+1) параллельных регистров разрядности 1о§2рр - параметр кода Фибоначчи)

Преобразование кода А Фибоначчи в модулярный код А выполняется сог- 55 ласно следующему уравнению:

А

- а., ., + ... + а,/5,,

jg

5

. 0

25 30 5 О 5

0

5

где Р; н Cfpd) (mod P ) - наименьший неотрицательный вычет от i-ro веса фибоначчиевого кода

о;;бА xiA HA(modpg);

cp(i)

H pV { при i 1;

pd-D+q pd-p-D при i 1

aj - двоичная цифра; 0 - наименьший неотрицательный вычет.

Первые р+1 весов фибоначчиевого кода всегда равны единице и, следовательно, не превышают величины g-1. Это позволяет использовать их

качестве исходных условий для получения вычетов /ipt2 п-ч с помощью рекурентного соотношения:

, ,. S ;.,-ь , (modp )

Принцип преобразования для всех модулей системы остаточных классов аналогичен.

Преобразователь (фиг. 1) работает следующим образом.

В исходном состоянии в регистр 4 записан код преобразуемого числа А в фибоначчиевом коде, а в регистр

5- единицы, накапливающий сумматор 3 по модулю обнулен, состояние блока

6синхронизации Соответствует исходному. Так как на входы сумматора 2 по модулю поступают единицы, то на вход записи (р+1)-го разряда регистра 5 поступает величины /Зв.2 На выходе блока 1 элементов PI устанавливается величина а ,.

В момент времени, соответствующий началу преобразования по входу 7, поступает импульс, в результате чего, на выходах блока 6 синхронизации начинают поочередно вырабатываться единичные импульсы, Первьш импульс пост5Т1ает на вход записи сумматора 3 и записывает в него произведение а, р, .

Второй импульс поступает на входы сдвига регистров 4 и 5, производит в них сдвиг информации на один разряд влево. При этом в (р+1)-й : разряд регистра 5 записывается значение /Зр+2. , а на выходе с мматора 2 образуется значение /Зр+ч .На выходе блока 1 элементов И образуется произведение а 2 2.После поступления третьего импульса в накапливающем сумматоре 3 образуется значение

(а,|, + )mod р

и так далее.

Таким образом, в процессе преобразования на выходе (р+1) разряда регистра 5 образуются значения А, , БИ на выходе блока 1 элементов И - значения а,/3, , а„ . В конце преобразования в накапливающем сумматоре 3 образуется сумма ci. , являндааяся результатом преобразования

Блок 6 синхронизации работает следующим образом. В исходном состоянии счетчик 10 по модулю и триггер 11 обнулены.

В момент времени, соответствующий началу преобразования по входу 7 по ступает импульс и устанавливает триггер 11 в единичное состояние. В результате этого на счетный вход счетчика 10 по модулю поступают тактовые импульсы. Так как вторые входы элементов 11 и 14 соединены с прймым и

инверсным выходами счетчика 10, соот- 30 первого слагаемого сумматора по мо- ветствующими его младшему разряду, то на выход 15 блока поступают импульсы с нeчeтны fи номерами, а на выход 16 - с четными. Так как модуль пересчета счетчика 10 равен п, то при постзшлении на информационный вход накапливающего сумматора 3 по модулю последнего слагаемого а,, счетчик 10 обнуляется и на его импульсном выходе обнуления вьфабаты- вается единичный импульс, который сбрасывает триггер 11 в нулевое сосдулю, вход второго слагаемого которо го соединен с выходом старшего разряда второго регистра сдвига, вход старщего разряда которого соединен с

35 выходом сумматора по модулю, первый и второй выходы блока синхронизации соединены соответственно с входом разрешения -сдвига второго регистра сдвига и с входой разрешения записи

40 накапливающего сумматора по модулю, выход которого является выходом пре- о азователя.

тояние, после чего блок 6 готов к новому циклу работы.

Iг

Формула изобретения

Преобразователь числа в модулярный код, содержащий блок элементов И, сумматор по модулю, накапливаюирй сумматор по модулю, первый регистр сдвига и блок синхронизации, причем - вход запуска и тактовый вход преобразователя соединены соответственно со входом запуска и тактовым входом блока синхронизации, первый выход которого соединен с входом разрешения сдвига первого регистра сдвига, выход младшего разряда которого соеди-, нен с первым входом блока элементов И, выход которого соединен с инфор- мационньм входом накапливающего сумматора по модулю, отличающийся тем, что, с целью расщиг рения области применения путем обеспечения возможности преобразования фибоначчиевого кода в модулярный код, он содержит второй регистр сдвига, причем выход младщего разряда второго регистра сдвига соединен с вторым входом блока элементов И и с входом

первого слагаемого сумматора по мо-

дулю, вход второго слагаемого которого соединен с выходом старшего разряда второго регистра сдвига, вход старщего разряда которого соединен с

выходом сумматора по модулю, первый и второй выходы блока синхронизации соединены соответственно с входом разрешения -сдвига второго регистра сдвига и с входой разрешения записи

накапливающего сумматора по модулю, выход которого является выходом пре- о азователя.

Фиг. 2 .

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1012237A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| «РЕОБР'АЗОВАТеЛЬ ДВОИЧНОГО КОДА - | 0 |

|

SU374596A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-04-27—Подача