Изобретение относится к .автоматике и вычислительной технике.

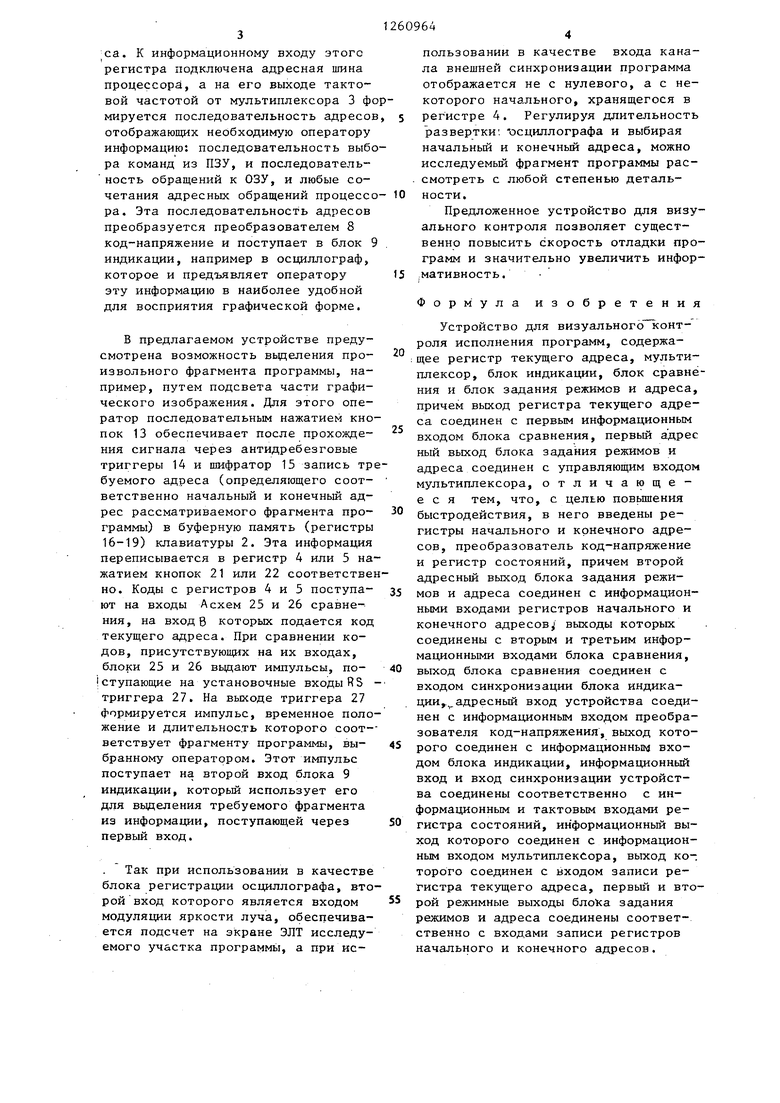

Цель изобретения - повьш1ение бы стродействия,

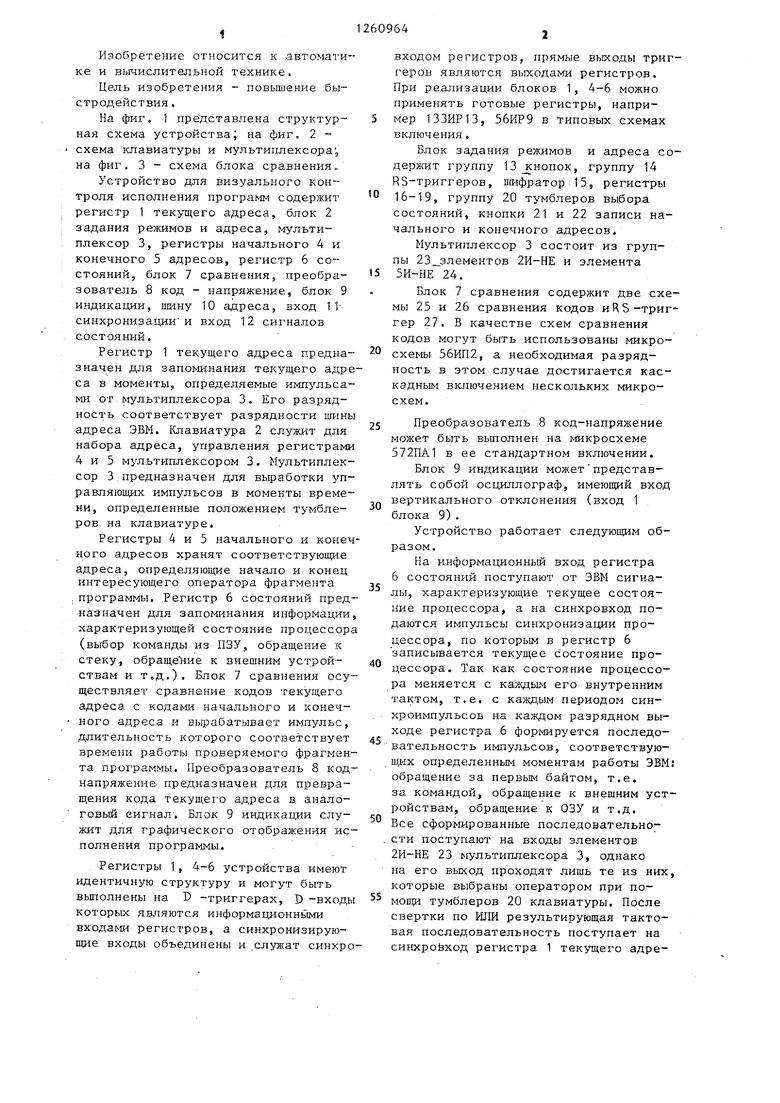

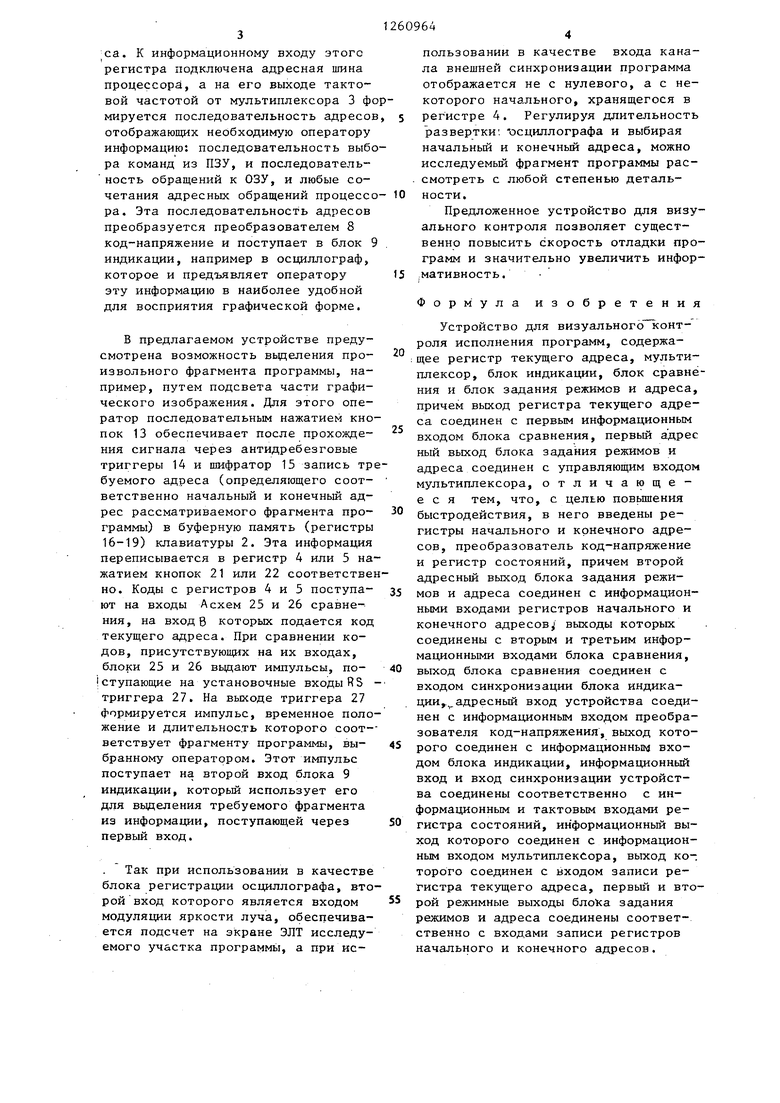

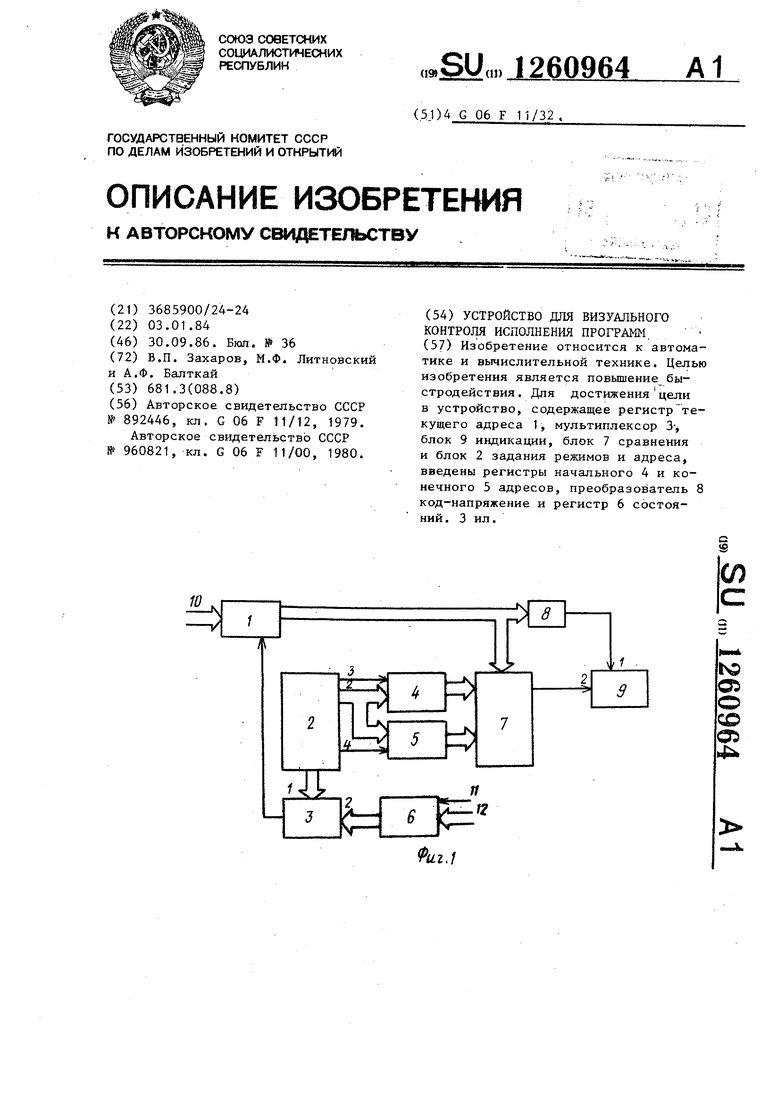

На фиг, I прё дставлена структурная схема устройстваJ на фиг, 2 - схема клавиатуры и мультиплексора на фиг, 3 - схема блока сравнения,.

Устройство для визуального контроля исполнения программ содержит регистр 1 текущего адреса, блок 2 задания режимов и адреса, мультиплексор 3, регистры начального 4 и конечного 5 адресов, регистр 6 состояний, блок 7 сравнения, преобразователь 8 код - напряжение, блок 9 индикации, шину 10 адреса, вход 11 синхронизации и вход 12 сигналов состояний.

Регистр 1 текущего адреса предназначен для запоминания текущего адреса в моменты, определяемые импульсами от.мультиплексора 3. Его разрядность соответствует разрядности шины адреса ЭВМ, Клавиатура 2 служит для набора адреса, управления регистрами 4 и 5 мультиплексором 3, Мультиплексор 3.предназначен для выработки управляющих импульсов в моменты времени, определенные положением тумблеров на клавиатуре.

Регистры 4 и 5 начального и конечного адресов хранят соответствующие

адреса, определяющие начало и конец интересующего оператора фрагмента

, программы. Регистр 6 состояний предназначен для запоминания информации характеризующей состояние процессора (выбор команды из ПЗУ, обращение к стеку, обраще ние к внешним устройствам и т.д.). Блок 7 сравнения осу- ществля.ет сравнение кодов текущего адреса с кодами начального и конеч ного адреса и вырабатывает импульс, длительность которого соответствует времени работы проверяемого фрагмента программы. Преобразователь 8 код- напряжение предназначен для превращения кода текущего адреса в анало говый сигнал-. Блок 9 индикации служит для графического отображения исполнения программы.

Регистры 1, 4-6 устройства имеют идентичную структуру и могут быть выполнены на D -триггерах, D -входы которых являются информационньми входами регистров, а синхронизирующие входы объединены и .служат синхровходом регистров, прямые выходы триггеров являются выходами регистров. При реализации блоков 1, 4-6 можно применять готовые регистры, напри- мер 133ИР135 56ИР9 в типовых схемах включения,

Блок задания, режимов и адреса содержит группу 13 кнопок, группу 14 RS-триггеров, пифратор:159 регистры 16-19, группу 20 тумблеров выбора состояний, кнопки 21 и 22 записи начального и конечного адресов.

Мультиплексор 3 состоит из группы 23 злементов 2И-НЕ и элемента 5И-НЕ 24,

Блок 7 сравнения содержит две схемы 25 и 26 сравнения кодов иВ5-триггер 27, В качестве схем сравнения кодов могут быть использованы микро- схемы 56ИП2, а необходимая разрядность в этом случае достигается каскадным включением нескольких микросхем,

Преобразователь В код-напряжение может быть выполнен на микросхеме 572ПА1 в ее стандартном включении.

Блок 9 индикации может представлять собой осциллограф, имеющий вход вертикального отклонения (вход 1 блока 9).

Устройство работает следующим образом.

На информационный вход регистра 6 состояний поступают от ЭВМ сигналы, характеризующие текущее состояние процессора, а на синхровход подаются импульсы синхронизации процессора, по которым в регистр 6 записывается текущее состояние процессора. Так как состояние процессора меняется с калодым его внутренним тактом, т,а, с каждым периодом син - кроимпульсов на каждом разрядном выходе регистра 6 формируется последовательность импульсов, соответствующих определенным моментам работы ЭВМ: обращение за первым байтом, т,е, за командой, обращение к внешним устройствам обращение к ОЗУ и т,д. Все сформированные последовательно- сти поступают на входы злементов 2И-НЕ 23 мультиплексора 3, однако на его выход проходят лишь те из них, которые выбраны оператором при по- мощи тумблеров 20 клавиатуры. После свертки по ИЛИ результирующая тактовая последовательность поступает на синхроЁход регистра 1 текущего адре

са. К информационному входу этого регистра подключена адресная шина процессора, а на его выходе тактовой частотой от мультиплексора 3 фомируется последовательность адресов отображающих необходимую оператору информацию: последовательность выбора команд из ПЗУ, и последователь- кость обращений к ОЗУ, и любые сочетания адресных обращений процессора. Эта последовательность адресов преобразуется преобразователем 8 код-напряжение и поступает в блок 9 индикации, например в осциллограф, которое и предъявляет оператору эту информацию в наиболее удобной для восприятия графической форме.

В предлагаемом устройстве предусмотрена возможность вьщеления произвольного фрагмента программы, например, путем подсвета части графического изображения. Для этого оператор последовательным нажатием кнопок 13 обеспечивает после прохождения сигнала через антидребезговые триггеры 14 и шифратор 15 запись требуемого адреса (определяющего соот- ветственно начальный и конечный адрес рассматриваемого фрагмента программы) в буферную память (регистры 16-19) клавиатуры 2. Эта информация переписывается в регистр 4 или 5 нажатием кнопок 21 или 22 соответственно. Коды с регистров 4 и 5 поступают на входы А схем 25 и 26 сравнения, на вход В которых подается код текущего адреса. При сравнении кодов, присутствующих на их входах, блоки 25 и 26 вьщают импульсы, по- I ступающие на установочные входы R 5 триггера 27. На выходе триггера 27 формируется импульс, временное положение и длительность которого соот- ветствует фрагменту программы, выбранному оператором. Этот импульс поступает на второй вход блока 9 индикации, который использует его для выделения требуемого фрагмента из информации, поступающей через первый вход.

Так при использовании в качестве блока регистрации осциллографа, второй вход которого является входом модуляции яркости луча, обеспечивается подсчет на экране ЭЛТ исследуемого участка программь, а при использовании в качестве входа канала внешней синхронизации программа отображается не с нулевого, а с некоторого начального, хранящегося в

регистре 4. Регулируя длительность развертки: осциллографа и выбирая начальный и конечный адреса, можно исследуемый фрагмент программы рас- смотреть с любой степенью детальности.

Предложенное устройство для визуального контроля позволяет существенно повысить скорость отладки программ и значительно увеличить инфор.мативность.

Формула изобретения

Устройство для визуального контроля исполнения программ, содержа- ; щее регистр текущего адреса, мультиплексор, блок индикации, блок сравнения и блок задания режимов и адреса, причем выход регистра текущего адреса соединен с первым информационным входом блока сравнения, первый адрес ный выход блока задания режимов и адреса соединен с управляющим входом мультиплексора, отличающееся тем, что, с целью повьппения

быстродействия, в него введены регистры начального и конечного адресов, преобразователь код-напряжение и регистр состояний, причем второй адресный выход блока задания режимов и адреса соединен с информационными входами регистров начального и конечного адресов выходы которых соединены с вторым и третьим информационными входами блока сравнения,

выход блока сравнения соединен с входом синхронизации блока индикации адресный вход устройства соединен с информационным входом преобразователя код-напряжения, выход которого соединен с информационным входом блока индикации, информационный вход и вход синхронизации устройства соединены соответственно с информационным и тактовым входами регистра состояний, информационный выход которого соединен с информационным входом мультиплексора, выход ко-, торого соединен с входом записи регистра текущего адреса, первый и второй режимные выходы блока задания режимов и адреса соединены соответственно с входами записи регистров начального и конечного адресов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для визуального контроля исполнения программ | 1985 |

|

SU1304028A2 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| УСТРОЙСТВО ДЛЯ ВИЗУАЛЬНОГО КОНТРОЛЯ ИСПОЛНЕНИЯ ПРОГРАММ | 1991 |

|

RU2012044C1 |

| Устройство для записи и коррекции программ | 1982 |

|

SU1149268A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство для контроля и диагностики блоков микроЭВМ | 1985 |

|

SU1374230A1 |

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является повышение быстродействия . Для достижения цели в устройство, содержащее регистр текущего адреса Г, мультиплексор 3-, блок 9 индикации, блок 7 сравнения и блок 2 задания режимов и адреса, введены регистры начального 4 и конечного 5 адресов, преобразователь 8 код-напряжение и регистр 6 состояний . 3 ил. Ю О О со 05 4

Редактор Л. Пчелинская

Составитель И. Сигалов

Техред М,Моргентал Корректор м. Максимипшнец

Заказ 5760, Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, Р. Ужгород, ул. Проектная, 4

(риг.З

| Устройство для контроля хода программы | 1980 |

|

SU892446A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1979 |

|

SU960821A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1984-01-03—Подача