Изобретение относится к запоминающим устройствам.

Известно устройство, содержащее блоки памяти, адресные входы которых подключены к регистру адреса, информационные входы через, последовательно соединенные элементы И и ИЛИ второй группы - к выходам перв.ых и вторых элементов И третьей группы, дополнительный регистр слова и дополнительные элементы НЕ, входы которых подключены к выходам дополнительного регистра слова и информационньм входам первых элементов И третьей группы, а выходы - к информационным входам вторых элементов И третьей группы 1.

Недостатком этого устройства является его сложность.

Наиболее близким техническим решением к изобретению является логическое запоминающее устройство, содержащее накопители, дешифраторы адреса, регистр адреса, первый и второй регистры слова, первую группу элементов И я элементы ИЛИ, причем адресные входы депифраторов адреса подключены к регистру адреса, а вы-. ходы - к входам накопителей, первые входы элементов И первой группы

подключены соответственно к шинам управления, вторые входы - к выходам второго регистра слова, а выходы к входам элементов ИЛИ.

Кроме того, оно содержит вторую и третью группу элементов И, при этом первые входы элементов И второй , группы соединены с одной из шин управления, а выходы - к информа10ционным входам накопителей, вторые входы одних из элементов И второй группы - к инверсным выходам первого регистра слова, прямые выходы накопителей соединены с первыми входами

15 одних из элементов И третьей груп-пы, а инверсные выходы с первыми входами других элементов И третьей группы, выходы элементов ИЛИ подключены к вторьм входам элементов И

20 третьей группы, выходы одних из которых соединены с входами установки первого регистра слова, выходы других - с входами установки

первого регистра слова 2.

О

Недостаток известного устройства

25 заключается в том, что для выполнения арифметических операций требуется относительно большое число обращений к накопителю, которое зависит от разрядности операндов и

также от количества переносов (при сложении) и заемов (при вычитании), за счет чего значительно снижается быстродействие устройства.

Целью изобретения является повышение быстродействия устройства путем обеспечения реализации за одно обращение к накопителю наряду с каждой из шестнадцати логических операций и арифметической операции сложения.

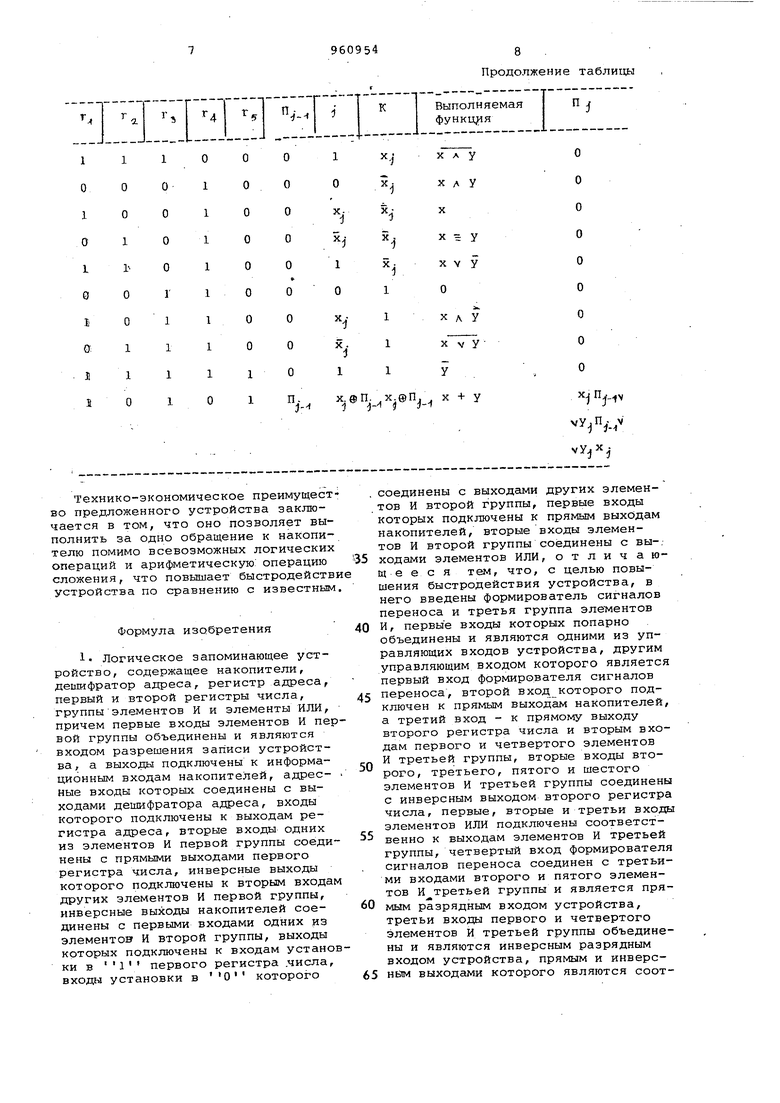

Поставленная цель достигается .тем, что в логическое запоминающее устройство) содержащее накопителиг дешифратор адреса, регистр адреса, первый и второйрегистры числа,группы элементов И и элементы ИЛИ, причем первые входы элементов И первой группы объединены и являются входом разрешения записи устройства, а выходы подключены к информационным входам накопителей, адресные входы которых соединены с выходами дешифратора адреса, входы которого подключены к выходам регистра адазеса, вторые входы одних из элементов И первой группы соединены с прямыми выходами первого регистра числа, инверсные -выходы которого подключены к вторым входам других элементов И первой группы, инверсные выходы накопителей соединены с первыми входами одних из элементов И второй группы, выходы которых подключены к входам установки в Ч, первого регистра числа, входы установки в О которого соединены с выходами других элементов И второй группы, первые входы которых подключены к прямым выходам накопителей, вторы входы элементов И второй группы соединены с выходами элементов ИЛИ, введены формирователь сигналов переноса и третья группа элементов И, первые входы которых попарно объединены и являются одними из управляющих Входов устройства, другим управляющим входом которого является первый вход формирователя сигналов переноса, второй вход которого подключен к прямым выходам накопителей, а третий вход - к прямому выходу второго регистра числа и вторым входам первого и четвертог элементов И третьей группы, вторые входы второго, третьего, пятого и шестого элементов И третьей группы соединены с инверсным выходом второго регистра числа, первые, вторые к третьи входы элементов ИЛИ подключены соответственно к выходам элементов И третьей группы, четвертый вход формирователя сигналов переноса соединен с третьими входами второго и пятого элементов И третье группы и является прямым разрядным входом устройства, третьи входи

первого и Четвертого элементов И третьей 1 группы объединены и являются инверсным разрядным входом устройства, прямым и инверсным выходами которого являются соответственно

первый и второй выходы формирователя сигналов переноса.

Кроме того, формирователь сигналов переноса содержит элементы И, элемент И-НЕ и элемент ИЛИ, выход

0 которого соединен с первыми входами первого элемента И и элемента И-НЕ, входы элемента ИЛИ подключены к выходам второго, третьего и четвертого :элементов И, вторые входы первого

5 элемента И и элемента И-НЕ объединены и являются первым входом формирователя, а выходы - соответствен но первым и вторым выходами формирователя, первые входы третьего и.

0 четвертого элементов И объединены и являются вторым входом формирова- теля, первый вход втррого элемента И и второй вход третьего элемента И объединены и являются третьим входом формирователя, четвертым входом которого являются Ьръединенные вторые входы второго и четвертого элементов И.

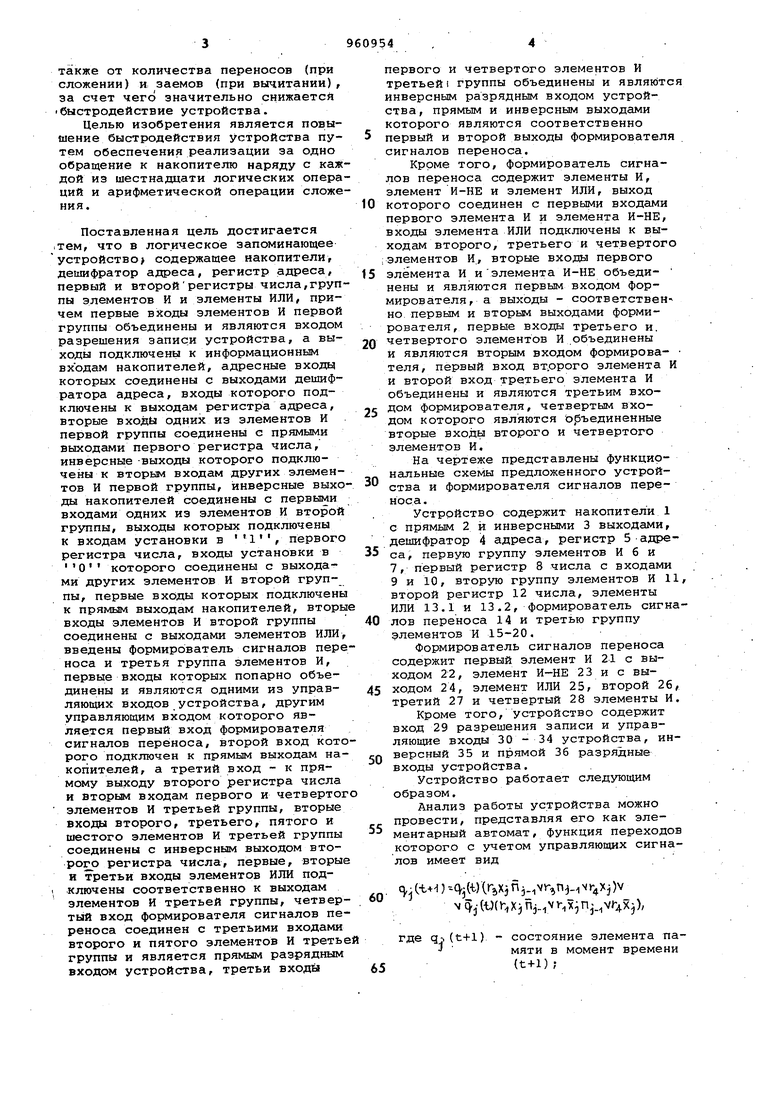

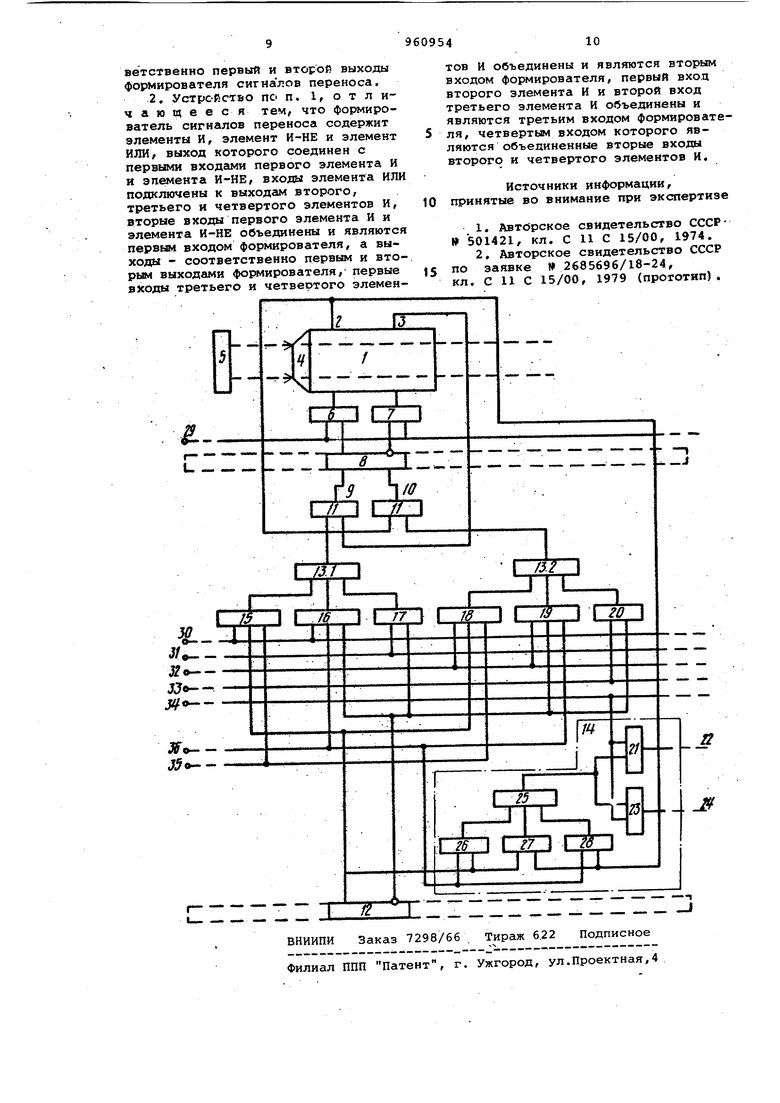

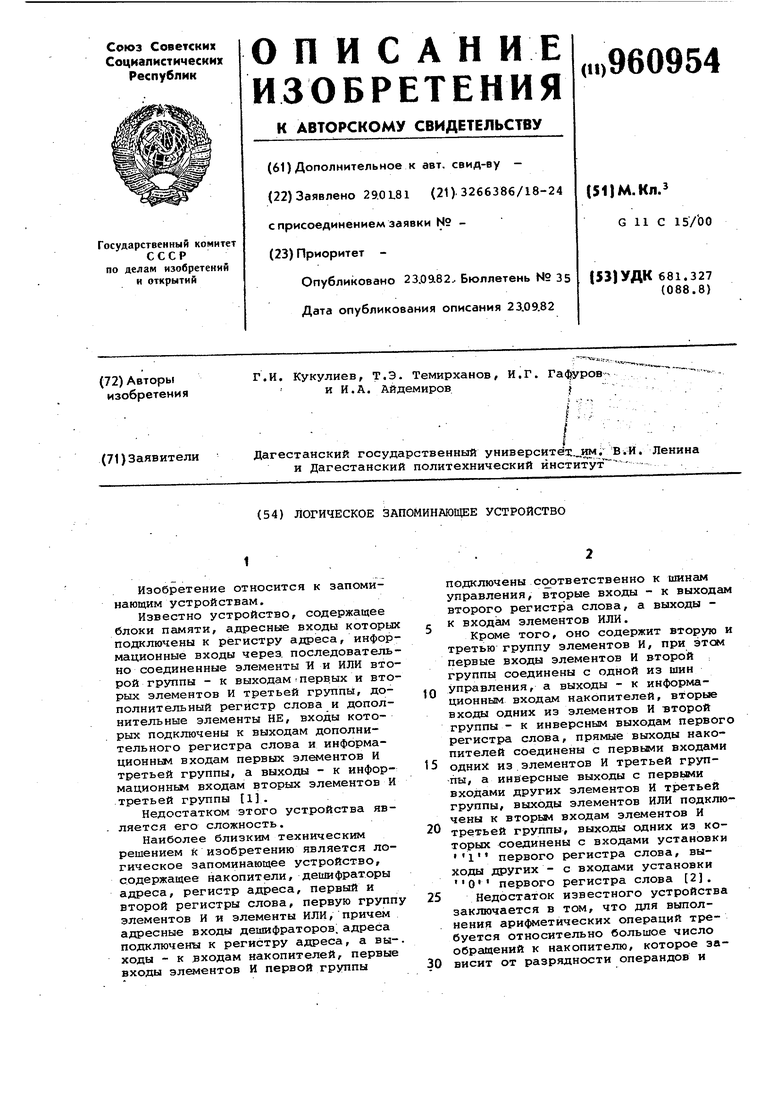

На чертеже представлены функциональные схемы предложенного устройства и формирователя сигналов переноса .

Устройство содержит накопители 1 с прямым 2 и инверсными 3 выходами, дешифратор 4 адреса, регистр 5 адреса, первую группу элементов И б и 7, первый регистр 8 числа с входами 9 и 10, вторую группу элементов И И, второй регистр 12 числа, элементы ИЛИ 13.1 и 13.2, формирователь сигналов переноса 14 и третью группу элементов И 15-20,

Формирователь сигналов переноса содержит первый элемент И 21 с выходом 22, элемент И-НЕ 23 и с выходом 24, элемент ИЛИ 25, второй 26, третий 27 и четвертый 28 элементы И.

Кроме того, устройство содержит вход 29 разрешения записи и управляющие входы 30 - 34 устройства, инвареный 35 и прямой 36 разрядные входы устройства.

Устройство работает следующим образом.

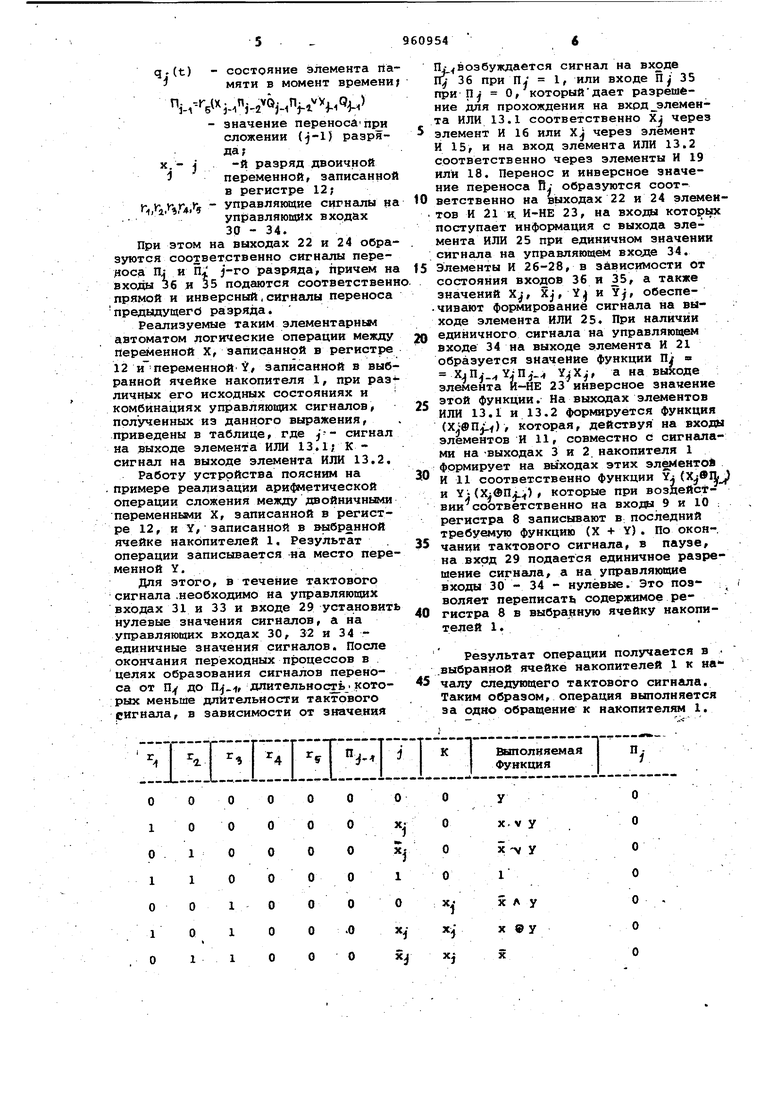

Анализ работы устройства можно провести, представляя его как элементарный автомат, функция переходов которого с учетом управляющих сигналов имеет вид

60 )(r xjnj-,vv-,n.))v

.,-(t)( nj..),

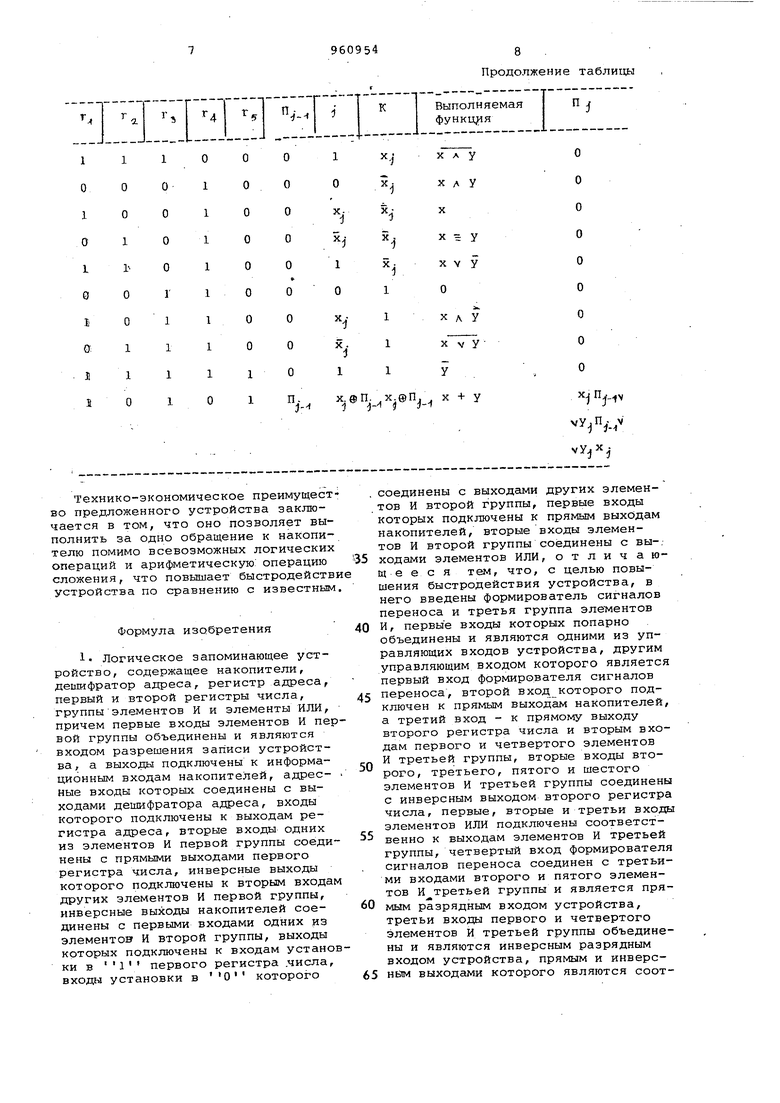

где g-,(t+l) - состояние элемента па мяти в момент времени (t+l); q.(t) - состояние элемента па мяти в момент времени 1--Гб н,. - значение переносапри сложении (j-1) разряда;-и разряд двоичной переменной/ записанно в регистре 12; Y- Уг.г-Гд.У, - управляющие сигналы н . управляющих входах 30 - 34. При этом на выходах 22 и 24 обра зуются соответственно сигналы переftoc i Ш и Пх j-ro разряда, причем н входы 36 и 35 подаются соответствен прямой и инверсный,сигналы переноса предыдущего разряда. Реализуемые таким элементарным автоматом логические операции между Переменной X, записанной в регистре 12 и -переменной1, записанной в выб ранной ячейке накопителя 1, при раз личных его исходных состояниях и комбинациях управляющих сигналов, полученных из данного выражения, приведены в таблице, где -- сигнал на выходе элемента ИЛИ 13.1; К сигнгш на выходе элемента ИЖ 13.2. Работу устройства поясним на примере реализации арифметической операции сложения между двойничными переменными X, записанной в регистре 12, и У, записанной в ВЫбранной ячейке накопителей 1. Результат операции записывается на место пере менной Y., Для этого, в течение тактового сигнала .необходимо на управляющих входах 31 и 33 и входе 29 установить нулевые значения сигналов, а на управляющих входах 30, 32 и 34 единичные значения сигналов. После окончания переходных процессов в целях образования сигналов переноса от П до , длительностьКОТОРЫХ меньше длительности тактового сигнала, в зависимости от значения

pj Т . П; возбуждается сигнал на входе П 36 при Пу 1, или входе Пу 35 при П 0, которыйдает разрешение для прохождения на вход элемента ИЛИ 13.1 соответственно Xj через элемент И 16 или Xj через элемент И 15, и на вход элемента ИЛИ 13.2 соответственно через элементы И 19 или 18. Перенос и инверсное значение переноса И; образуются соответственно на выходах 22 и 24 элементов И 21 и. И-НВ 23, на входы которых поступает информация с выхода элемента ИЛИ 25 при единичном значении сигнсша на управляющем входе 34. Элементы И 26-28, в зависимости от состояния входов 36 и 35, а также значений X,j, Xj, Y и Yj, обеспечивают формирование сигнала на выходе элемента ИЖ 25. При наличии единичного сигнала на управляющем входе 34 на выходе элемента И 21 образуется значение функции П в Y.-nj.4 Y.fX, а на выходе элемента И-НЕ 23 инверсное значение этой функции. На выходах элементов ИЛИ 13.1 и 13.2 формируется функция (Xifflnj.), которая, действуя на входы элементов И 11, совместно с сигналами на -выходах 3 и 2. накопителя 1 Формирует на выходах этих эл ентой И 11 соответственно функции YJ ( и Y (Х;ФП) , которые при воз| Jдеисти 10 : ВИИ соответственно на входы 9 регистра 8 записывают в последний требуемую функцию (X + Y) . По окон-, чании тактового сигнала, в паузе, на вход 29 подается единичное разрешение сигнала, а на управляющие входы 30 - 34 - нулевые. Это поз- ; воляет переписать содержимое регистра 8 в выбранную ячейку накопителей 1. Результат операции получается в выбранной ячейке накопителей 1 к началу следующего тактового сигнала. Таким образом, операция выполняется за одно обращение к накопителям 1.

Продолжение таблигул

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1982 |

|

SU1024988A1 |

| Логическое запоминающее устройство | 1981 |

|

SU970471A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ПРОГРАММНО-УПРАВЛЯЕМОЙ СРЕДЫ | 1997 |

|

RU2132081C1 |

| Логическое запоминающее устройство | 1978 |

|

SU780042A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Устройство поиска псевдослучайной последовательности | 1991 |

|

SU1788592A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Конвейерное вычислительное устройство | 1985 |

|

SU1322261A1 |

Технико-экономическое преимущест во предложенного устройства заключается в том, что оно позволяет выполнить за одно обращение к накопителю помимо всевозможных логических операций и арифметическую операцию сложения, что повышает быстродейст устройства по сравнению с известным Формула изобретения Логическое запоминающее устройство, содержащее накопители, дешифратор адреса, регистр адреса, первый и второй регистры числа, группыэлементов И и элементы ИЛИ, причем первые входы элементов И пер вой группы объединены и являются входом разрешения записи устройства , а выходы подключены к информационным входам накопителей, адресные входы которых соединены с выходами дешифратора адреса, входы которого подключены к выходам регистра адреса, вторые входы одних из элементов И первой группы соеди нены с прямыми выходами первого регистра числа, инверсные выходы которого подключены к вторым входа других элементов И первой группы, инверсные выходы накопителей соединены с первьЕМи входами одних из элементон И второй группы, выходы которых подключены к входам устано ки в 1 первого регистра .числа. которого входы установки в соединены с выходами других элементов И второй группы, первые входы которых подключены к прямым выходам накопителей, вторые входы элементов И второй группы соединены с вы-, ходами элементов ИЛИ, о т л и ч а ющ е ее я тем, что, с целью повышения быстродействия устройства, в него введены формирователь сигналов переноса и третья группа элементов И, первые входы которых попарно объединены и являются одними из управляющих входов устройства, другим управляющим входом которого является первый вход формирователя сигналов переноса, второй вход которого подключен к прямым выходам накопителей, а третий вход - к прямому выходу второго регистра числа и вторым входам первого и четвертого элементов И третьей группы, вторые входы второго, третьего, пятого и шестого элементов И третьей группы соединены с инверсным выходом второго регистра числа, первые, вторые и третьи входы элементов ИЛИ подключены соответственно к выходам элементов И третьей группы, четвертый вход формирователя сигналов переноса соединен с третьими входами второго и пятого элементов И третьей группы и является прямым разрядным входом устройства, третьи входы первого и четвертого элементов И третьей группы объединены и являются инверсным разрядным входом устройства, прямым и инверсным ВЫХОДс1МИ которого являются COOTветственио первый и второй выходы формирователя сигналов переноса,

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР по заявке №2685696/18-24,

кл. С 11 С 15/00, 1979 (прототип).

Авторы

Даты

1982-09-23—Публикация

1981-01-29—Подача