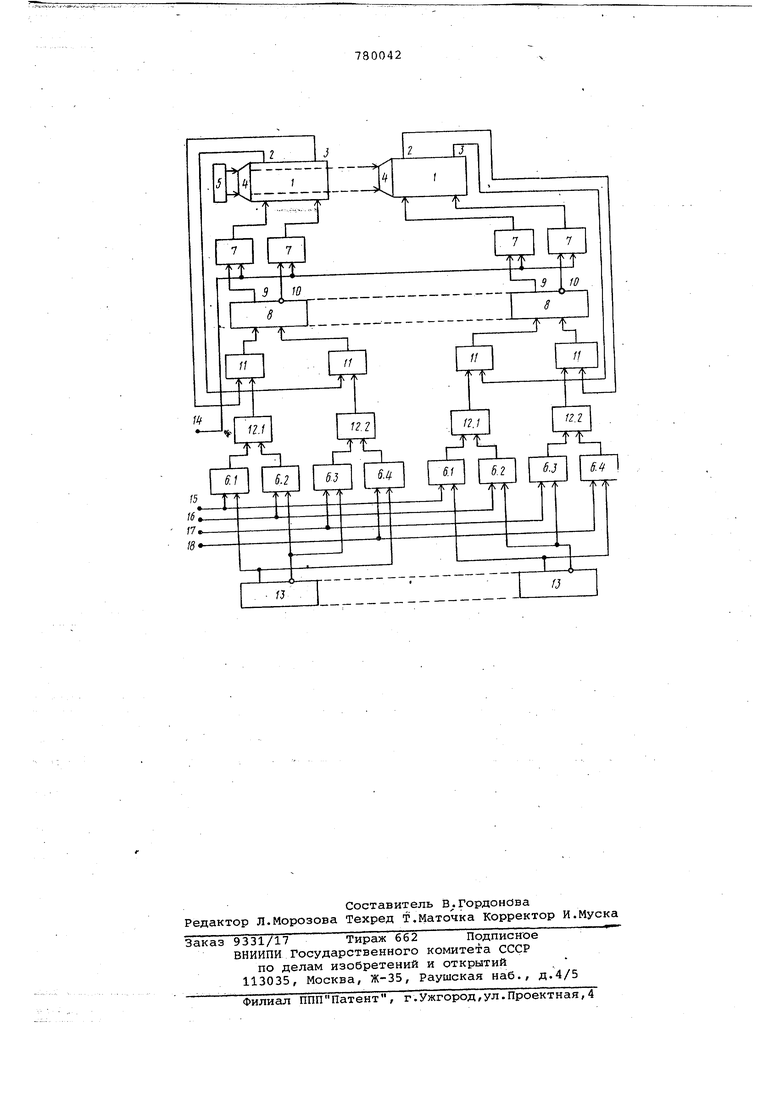

выходы, дешифраторы4 адреса, регис 5 адреса, первую 6,1-6,4 и вторую

7группы элементов И, первый регист

8слова, имеющий прямые 9 и инверс.ные 10 выходы, третью группу элементов и 11, элементы ИЛИ 12,1 и 12,2, второй регистр 13 слова, управляющие шины 14-18.

Адресные входы дешифраторов 4 адреса подключены к выходам регистр 5 адреса, а выходы - к входам накопителей 1. Первые входы элементов И первой группы 6,1-6,4 подключены соответственно к шинам 15-18 управления, вторые входы - к выходам второго регистра 13 слова, а выходы - к входам элементов ЯЛИ 12,1 и 12,2.

Прямые выходы 2 накопителей 1 соединены с первыми входами одних из элементов И 11 третьей группы,а инверсные выходы 3-е первыми входами других элементов И 11 третьей группы. Выходы элементов ИЛИ 12,1 и 12,2 подключены к вторым входам элементов И 11 третьей группы, выходы одних из которых соединены с входами установки в 1 первого регистра 8 слова, а выходы других с входами установки в О первого регистра 8 слова.

Первые входы элементов И второй группы 7 соединены с шиной 14 управления, а выходы - с информационными входами накопителей 1. Вторые входы одних из элементов И второй

группы 7 подключены к прямым выходам 9 первого регистра слова 8, а вторые выходы других элементов И второй группы 7 - к инверсным выходам 10 первого регистра 8 слова.

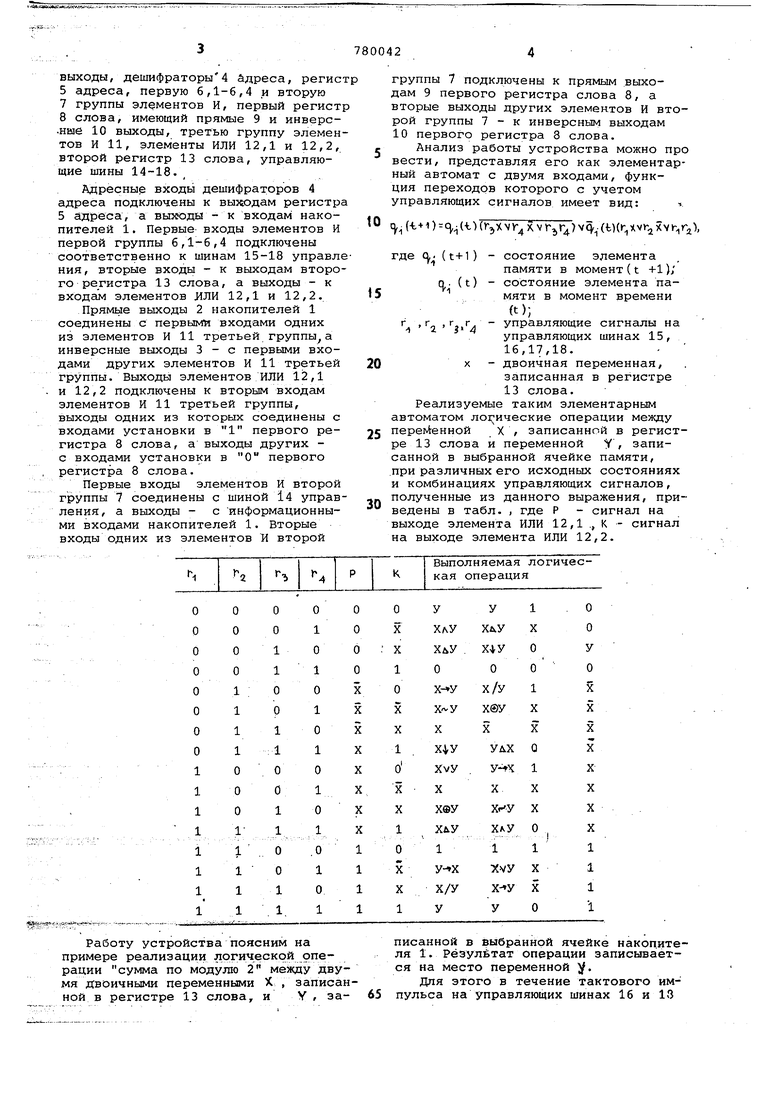

Анализ работы устройства можно пр вести, представляя его как элементарный автомат с двумя входами, функция переходов которого с учетом управляющих сигналов имеет вид:

tVi(,a)(rvrvr Vr)v.(t)(i-,v -2XVK-,

где (t+1) - состояние элемента

памяти в момент (t +1); q,. (t) - состояние элемента памяти в момент времени (t);

управляющие сигналы на

. управляющих шинах 15, 16,17,18.

X - двоичная переменная, записанная в регистре 13 слова.

Реализуемые таким элементарным автоматом ло:;;ические операции между переменной , X , записанной в регистре 13 слова и переменной У, записанной в выбранной ячейке памяти, при различных его исходных состояниях и комбинациях управляющих сигналов, полученные из данного выражения, приведены в табл. , где Р - сигнал на выходе элемента ИЛИ 12,1 ., к - сигнал на выходе элемента ИЛИ 12,2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU960954A1 |

| Логическое запоминающее устройство | 1981 |

|

SU970471A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Логическое запоминающее устройство | 1982 |

|

SU1024988A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1043750A1 |

| Логический запоминающий блок | 1975 |

|

SU553681A1 |

Работу устройства поясним на примере реализации логической операции сумма по модулю 2 между Двумя двоичными переменными К , записанной в регистре 13 слова, и У, записанной в выбранной ячейке накопителя 1 . Результат операции записывается на место переменной }(.

Для этого в течение тактового импульса на управляющих шинах 16 и 13

и шине 14, по которой поступает сигнал разрешения записи, необходимо установить нулевое значение сигналов а на управляющих шинах 15 и 17 - еди ичнoe значение сигналов. При этом ч;ерез элементы И 6,1 и ИЛИ 12,1 проходит сигнал, повторяющий переменную X , а через элементы И 6,3 и ИЛИ 12,2 проходит сигнал, повторяющий инверсное значение переменной X. В зависимости от значения переменной К, то есть от состояния выбранной ячейки памяти и, следовательно, прямых 9 и ин.версных 10 выходов накопителя 1 регистр 8 слова через элементы И 11 третьей группы записывается функция X, ®Y

По окончании тактового импульса, в паузе, на управляющую шину 14 (разрешения записи) подается единичное значение сигнала, а на управляющие шины 15,16,17,18 - нулевое. Это позволяет переписать содержимое регистра 8 слова в выбранную ячейку накопителя 1.

Результат операции получается в выбранной ячейке накопителя 1 к началу следующего тактового импульса. Таким образом, операция выполняется за одно обращение к накопителю 1.

Технико-экономическое пруимуществ предложенного устройства заключается в том, что оно обеспечивает выполнение каждой логической операции за время одного обращения к накопителю, за счет чего повышено быстродействие этого логического запоминающего устройства.

.Формула изобретения

.

Логическое запоминающее устройст во, содержащее накопители дешифраторы адреса, регистр адреса, первый и второй регистры слова, первую группу элементов И иэлементы ИЛИ, причем адресные входы дешифраторов адреса подключены к вы содам регистра адреса, а выходы - к входам накопителей, первые входы элементов И первой группы подключены соответственно к шинам управления, вторые входы, к выходам втор6г6 рёгйс;тра слбва, а вйходы -к входам элёмёнтЬв ИЛИ, ,

0 отличающе-еся тем, что, с целью повышения быстродействия устройства, оно содержит вторую и третью группы элементов И, причем первые входы элементов И второй группы сое5динены с одной из шин управления, а &ЫХОДЫ - с информационными входами накопителей, вторые входы одних из элементов И второй группы подключены к прямым выходам первого регистра

0 слова, а вторые выходы других элементов И второй группы - к инверсным выходам первого регистра слова, прямые выходы накопителей соединена с первыми входами одних из элементов и третьей группы, а-инверсные выходы 5с первыми входами других элементов И третьей группы, выходы элементов ИЛИ подключены к вторым входам элементов И третьей группы, выходы одних из которых соединены с входами уста0новки в 1 первого регистра слова, а выходы других - с входами установки в О первого регистра слова.

Источники информации,

5 принятые во внимание при экспертизе

0 (прототип) . ..

Авторы

Даты

1980-11-15—Публикация

1978-11-20—Подача