Изобретение относится к вычисли тельной технике и может быть исноль- зовано в высокопроизводительных и специализированных ЭВМ.

Цель изобретения - расширение функциональных возможностей за счет реализации онерации вычисления сумм в ЗДа

,., ,

,--1 )

где

- множество пар перемножаемых

К-разрядных чисел; L - количество одновременно суммируемых чисел в режиме умножения.

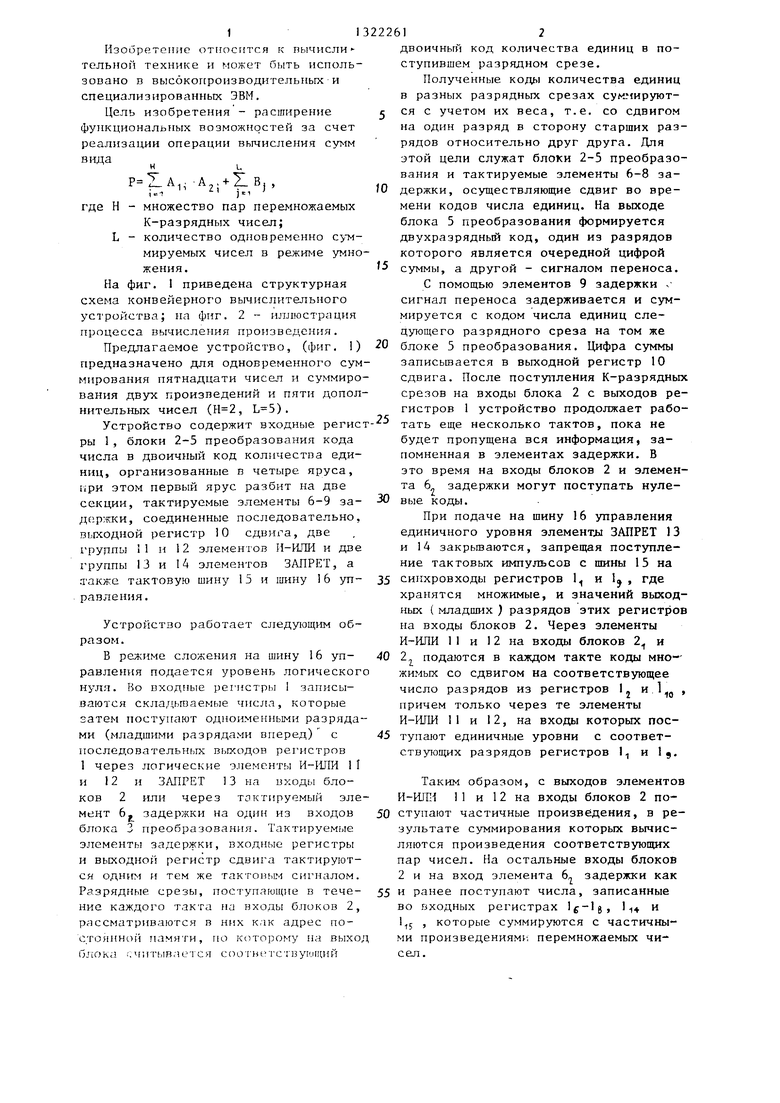

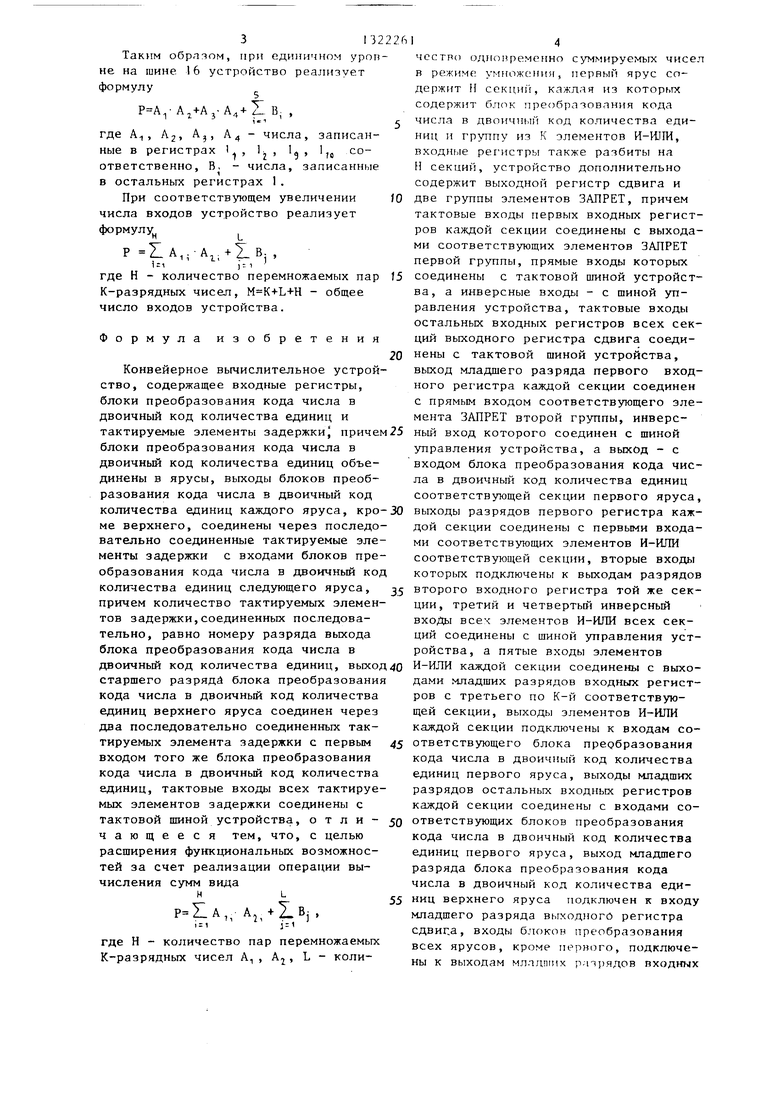

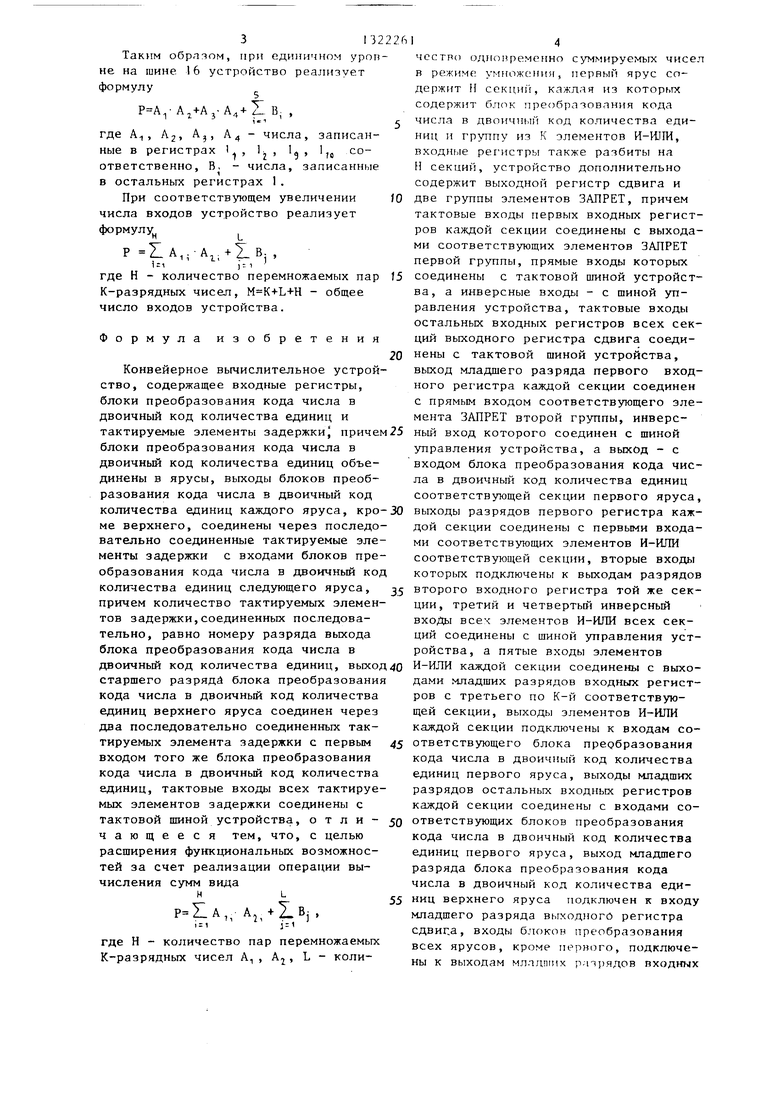

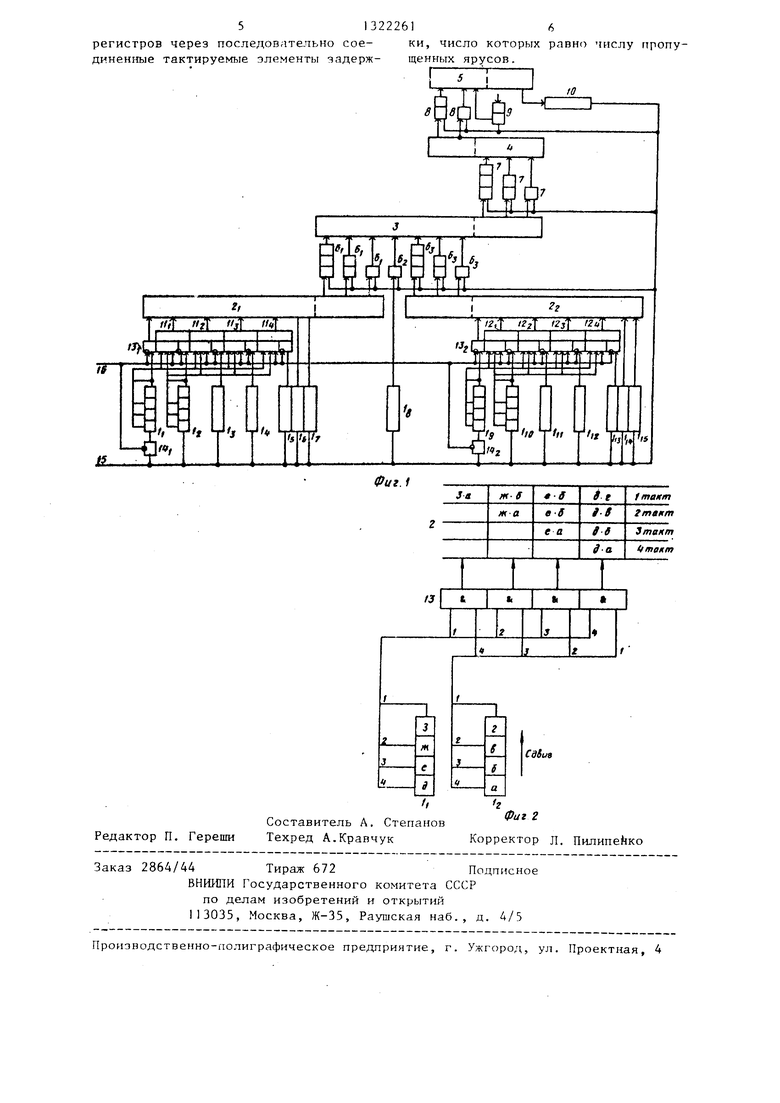

На фиг. I приведена структурная схема конвейерного вычислительного устройства; на фиг. 2 -- иллюстрация процесса вычисления произведения.

Предлагаемое устройство, (фиг. I) предназначено для одновременного суммирования пятнадцати чисел и суммирования двух произведений и пяти дополнительных чисел (, ).

Устройство содержит входные регис ры 1, блоки 2-5 преобразования кода числа в двоичный код количества единиц, организованные в четыре яруса, гфи этом первый ярус разбит на две секции, тактируемые элементы 6-9 за- дсфжки, соединенные последовательно, выходной регистр 10 сдвига, две 1 РУППЫ И и 12 элементов И-ИЛИ и две группы I3 и 14 элементов

ЗАПРЕТ, а

.также тактовую шину равления.

15 и шину 16 уп- 35 сипхровходы регистров L и L , где

9

хранятся множимые, и значений выхо ных ( младших ) разрядов этих регистр на входы блоков 2. Через элементы

Устройство работает следующим образом.

В режиме сложения на шпну 16 управления подается уровень логического нуля. Во входные регистры 1 записываются складьгоаемые числа, которые затем поступают одиоимеиными разрядами (младшими разрядами вперед) с последовательнг)1х выходов регистров 1 через логические элементы И-1ШИ 1I и 12 п ЗАПРЕТ 13 на входы блоков 2 или через тактируемый элемент 6 задержки на один из входов блока 3 преобразования. Тактируем)1е элементы задержки, входные регистры и выходной регистр сдвига тактируются одним и тем же тактовььм сигналом. Разрядные срезы, поступающие в течение каждого такта на входы блоков 2, рассматриваются в них как адрес по- стоиннон памяти, по кпторому на выход 6jiO ка :. ч I (тыв а е т с я со о тн е т с тв уклди и

5

0

-

0

двоичный код количества единиц в поступившем разрядном срезе.

Полученные коды количества единиц в разных разрядных срезах сумчируют- ся с учетом их веса, т.е. со сдвигом на один разряд в сторону старших разрядов относительно друг друга. Для этой цели служат блоки 2-5 преобразования и тактируемые элементы 6-8 задержки, осуществляющие сдвиг во времени кодов числа единиц. На выходе блока 5 преобразования формируется двухразрядный код, один из разрядов которого является очередной цифрой суммы, а другой - сигналом переноса.

С помощью элементов 9 задержки v- сигнал переноса задерживается и суммируется с кодом числа единиц следующего разрядного среза на том же блоке 5 преобразования. Цифра суммы записьшается в выходной регистр 10 сдвига. После поступления К-разрядных срезов на входы блока 2 с выходов регистров 1 устройство продолжает работать еще несколько тактов, пока не будет пропущена вся информация, запомненная в элементах задержки. В это время на входы блоков 2 и элемента 6 задержки могут поступать нулевые коды.

При подаче на шину 16 управления единичного уровня элeмeнт I ЗАПРЕТ 13 и 14 закрьшаются, запрещая поступление тактовых импульсов с шины 15 на

сипхровходы регистров L и L , где

9

хранятся множимые, и значений выходных ( младших ) разрядов этих регистров на входы блоков 2. Через элементы

И-ИЛИ 2

11 и 12 на входы блоков 2.

и

. подаются в каждом такте коды множимых со сдвигом на соответствующее число разрядов из регистров 1 и 1 , причем только через те элементы И-ИЛИ 11 и 12, на входы которых поступают единичные уровни с соответствующих разрядов регистров 1, и Ij.

Таким образом, с выходов элементов И-ИЛП 11 и 12 на входы блоков 2 по50 ступают частичные произведения, в результате суммирования которых вычисляются произведения соответствующих пар чисел. На остальные входы блоков 2 и на вход элемента 6 задержки как

55 и ранее поступают числа, записанные во входных регистрах If-lj, 11 и 1,5 , которые суммируются с частичными произведениямр; перемножаемьгх чисел.

3132

Таким обрл:1ом, при единичном уроп не на шине 16 устройство реализует формулу

,- А,+А,.

V

1 1 3 4 .- i

где А, А2, AJ, А - числа, записанные в регистрах 1 , 1 , Ц , 1, соответственно, В, - числа, записанные в остальных регистрах 1.

При соответствующем увеличении числа входов устройство реализует формулу

Р L А,.-А.+|l В. ,

Ui)-1

где Н - количество перемножаемых пар

К-разрядных чисел, - общее число входов устройства.

Формула изобретения

Конвейерное вычислительное устройство, содержащее входные регистры, блоки преобразования кода числа в двоичный код количества единиц и тактируемые элементы задержки) причем блоки преобразования кода числа в двоичный код количества единиц объединены в ярусы, выходы блоков преобразования кода числа в двоичный код количества единиц каждого яруса, кроме верхнего, соединены через последовательно соединенные тактируемые элементы задержки с входами блоков преобразования кода числа в двоичный код количества единиц следующего яруса, причем количество тактируемых элементов задержки,соединенных последовательно, равно номеру разряда выхода блока преобразования кода числа в двоичный код количества единиц, выход старшего разряди блока преобразования кода числа в двоичный код количества единиц верхнего яруса соединен через два последовательно соединенных тактируемых элемента задержки с первым входом того же блока преобразования кода числа в двоичный код количества единиц, тактовые входы всех тактируемых элементов задержки соединены с тактовой шиной устройства, о т л и - чающееся тем, что, с целью расширения функциональных возможностей за счет реализации операции вычисления сумм вида

Н

I:A,,-A,,-.IBJ,

Jгде Н - количество пар перемножаемых К-разрядных чисел А,, А, L - колиO

5

0

5 0 0 5 0

5

чество однонременно суммируемых чисел в режиме умножения, первый ярус содержит И секциГг, каждая из которьгх содержит блок преобратовлния кода числа в двоичный код количества единиц и группу из К элементов И-ШШ, входные рег истры также разбиты на Н секций, устройство дополнительно содержит выходной регистр сдвига и две группы элементов ЗАПРЕТ, причем тактовые входы первых входных регистров каждой секции соединены с выходами соответствующих элементов ЗАПРЕТ первой группы, прямые входы которьгх соединены с тактовой шиной устройства, а инверсные входы - с шиной управления устройства, тактовые входы остальных входных регистров всех секций выходного регистра сдвига соединены с тактовой шиной устройства, выход младшего разряда первого входного рег истра каждой секции соединен с прямым входом соответствующего элемента ЗАПРЕТ второй группы, инверсный вход которого соединен с шиной управления устройства, а выход - с входом блока преобразования кода числа в двоичный код количества единиц соответствующей секции первого яруса, выходы разрядов первого регистра каждой секции соединены с первыми входами соответствующих элементов И-ИЛИ соответствующей секции, вторые входы которьгх подключены к выходам разрядов второго входного регистра той же секции, третий и четвертьш инверсный вхоДы всех элементов И-ИЛИ всех секций соединены с шиной управления устройства, а пятые входы элементов И-ИЛИ каждой секции соединены с выходами младших разрядов входных регистров с третьего по К-й соответствующей секции, выходы элементов И-ИЛИ каждой секции подключены к входам соответствующего блока преобразования кода числа в двоичный код количества единиц первого яруса, выходы младших разрядов остальных входных регистров каждой секции соединены с входами соответствующих блоков преобразования кода числа в двоичный код количества единиц первого яруса, выход младшего разряда блока преобразования кода числа в двоичный код количества единиц верхнего яруса подключен к входу младшего разряда выход}югО регистра сдвиг.а, входы б.чокон преобразования всех ярусов, кроме первого, подключены к выходам младших разрядов входных

513222616

регистров через последовательно сое- ки, число которых равно числу пропу- диненные тактируемые элементы задерж- щенных ярусов.

I

5 i

snei

I

ПК Нг1 //jT tivl

ViVnVm i iTi i tirt

т

t M jr V «

- - T r т

7г

12 /гЯ

на. I., . Mj ATxAi jA flтгШтрУтр гтрУ

/j т

I I

frj

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования М чисел | 1984 |

|

SU1200281A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО МОДУЛЮ ОТ ЧИСЛА | 1996 |

|

RU2110147C1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ | 2021 |

|

RU2780985C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| Устройство для умножения элементов конечных полей | 1984 |

|

SU1226445A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Генератор случайных последовательностей | 1985 |

|

SU1327099A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2023 |

|

RU2809741C1 |

Редактор П. Гереши

Составитель А. Степанов Техред А.Кравчук

Заказ 2864/44 Тираж 672Подписное

ВНЮПта Государственного комитета СССР

по Д€1лам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д. Д/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг 2

Корректор л. Пилипейко

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения раствора для формования пленок | 1983 |

|

SU1206281A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-10-11—Подача