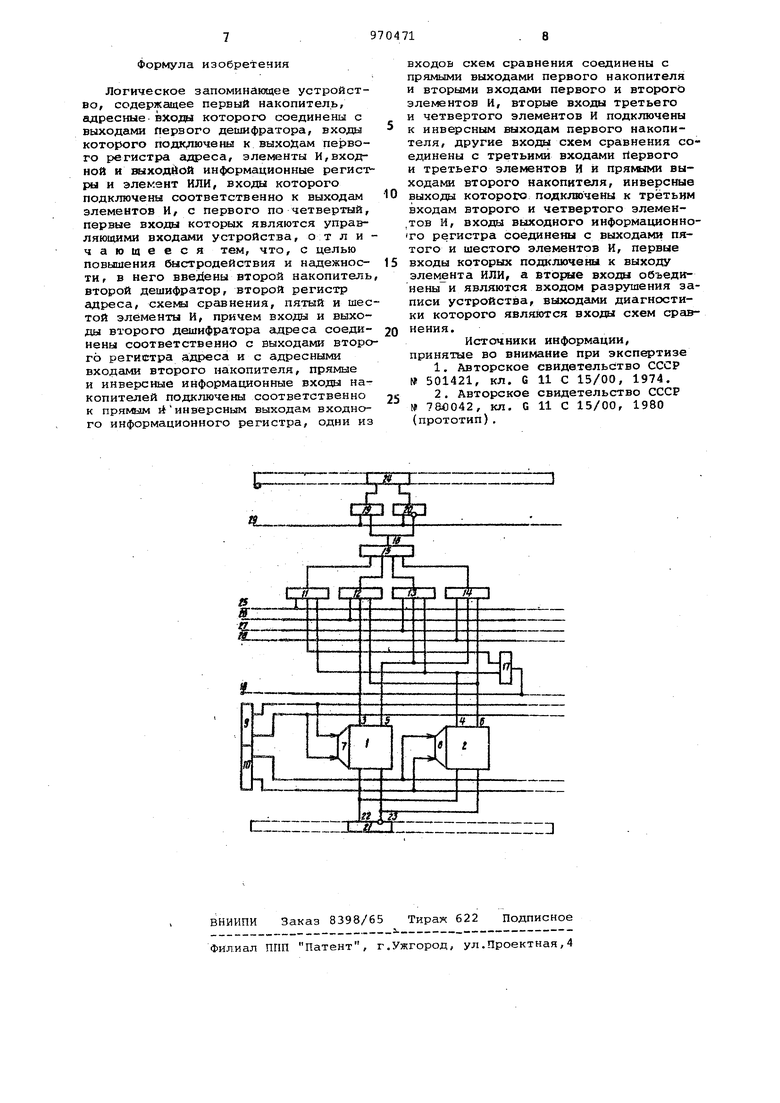

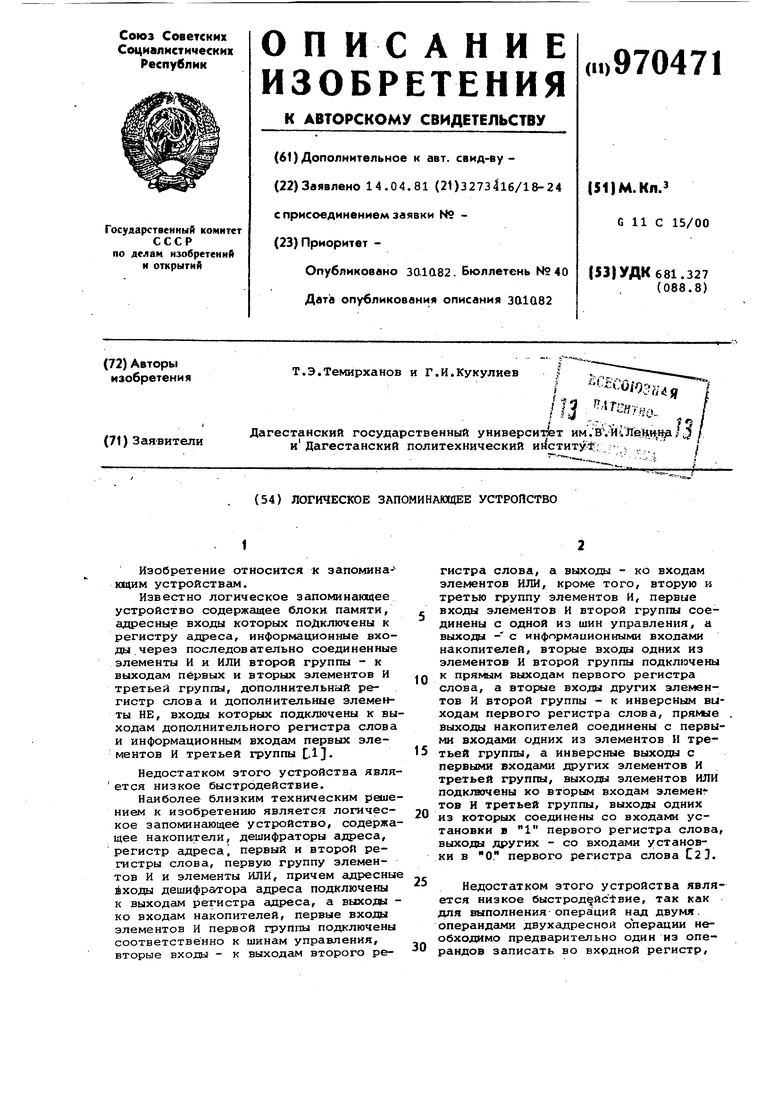

и только после этого выполняется требуемая операция. Цель, изобретения - повышение быст родействия устройтсва. Поставленная цель достигается тем, что в логическое запоминающее устройство, содержащее первый накопитель, адресные входы которого соединены с выходами первого дешифратора адреса, входы которого подключены к выходам первого регистра адреса, элементы И, входной и выходной информационный регистры и элементы ИЛИ, входы которого подключены соответственно к выходам элементов И с первого по четвертый, первые входы которых являются управляющими входами устройства, введены второй накопи тель, второй дешифратор, второй регистр адреса, схемы сравнения, пятый и шестой элементы И, причеМ входы и выходы второго дешифратора адреса соединены соответственно с выходами второго регистра адреса и с адресными входами второго накопителя, прямы и инверсные информационные входы накопителей -подключены соответственно к прямым и инверсным выходам входног информационного регистра, одни из входов схем сравнения соединены с прямыми выходами первого накопителя и вторыми входами первого и второго элементов И, вторые вжоды третьего и четвертого элементов И подключены к инверсныМ выходам первого накопителя другие входы схем сравнения соединен с третьими входами первого и третьего элементов И и прямыми выходами второго накопителя, инверсные выходы которого подключены к трегьим входам второго и четвертого элементов И,, входы выходного информационного ре гистра соединены.с выходами пятого и шестого элементов И, первые входы которых подключены к выходу элемента ИЛИ, а вторые входы объединены и являются входом разрешения записи устройства, выходами диагностики ко торого являются выходы схем сравнения , На чертеже представлена функциональная электрическая схема устройс ва. Устройство содержит первый 1 и второй 2 накопители с прямыми 3 и 4 и инверсными 5 и 6 выходами, первый 7 и второй 8 дешифраторы адреса, первый 9 и второй 10 регистры адреса, первый 11, второй 12, третий 13 и четвертый 14 элементы И, элемент ИЛИ 15 с выходом 16, схемы 17 сравнения с выходами 18, пятый 19 и шее той 20 элементы И, входной информационный регистр 21 с прямыми 22 и инверсными 23 выходами и выходной информационный регистр 24. На черте же обозначены управляющие входа 25и вход 29 разрешения записи устройства. Логическое запоминающее устройство работает следующим образом. Анализ работы устройства можно провести, представляя его как эл ментарный автомат, функция переходов которого с учетом управляющих сигналов имеет вид V ° l , У V S i Yi -Л N- Vi F-(x,), где S - выход i-Toro разряда лошки обрамления; . 1-тый разряд двоичной переменной, врзбуждаемой на выходах первой группы 1 накопителей и выбираемой по niepBOMy адресу, хранящейся в первой 9 половине регистра адреса; у. - 1гтый разряд двоичной пе ременной, возбуждаемой на выходах второй группы 2 накопителей и выбираемой по второму адресу, хранящейся во второй половине регистра адреса; F - значения сигнала на. шине Флаг диагностики ; г, , TI, -.управляющие сигналы . i Г| , г на управлякяцих шинах 2525-28, Работа устройства поясняется на примере реализации логической операции Сумма по модулю два. Для этого в течение тактового импульса на входах 25 и 28 устанавливается нулевое значение сигнешов, а на входах 26 и 27 и входе 29 - единичное значение сигналов. Наличие нулевого значения сигнала на входах 25 и 28 обеспечивает на выходах элементов И 11 и 14 также нулевые значения сигналов, а наличие одиночного значения сигналов на входах 26 и 27 формирует на выходах элементов И 12 и 13 соответственно функции ХЛУ и . Таким образом, на входах элемента ИЛИ 15 формируются соответственноt О, логическая функций логическая функция ХАУ и О. На выходе элемента ИЛИ 15 формируется функция S, равная S OV(XAT)V (XAY))V(XAY)«®Y. Наличие единичного значения сигнала на входе 29 обеспечивает на выходах элементов И 19 и 20 соответственно значения функций S и S, и информация записывается в регистр 24 парафазным кодом без предварительного стирания старой информации. Таким образом, по окончании тактового импульса в регистре 24 записан результат операции .

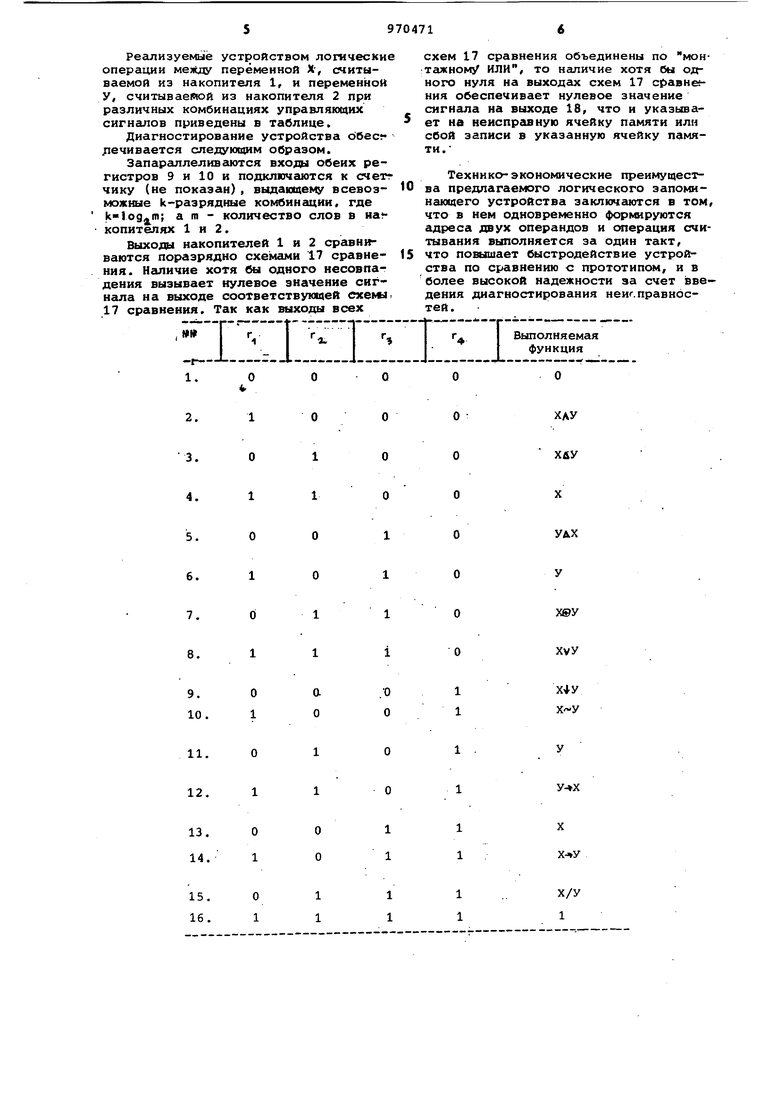

Реёшизуемыё устройством логически операции меящу перёмеиной Х, считываемой из накопителя 1, и перёмеиной У, считываемой из накопителя 2 при различных комбинациях управляющих сигиалов приведены в таблице.

Диагностирование устройства d6ecf лечивается следующим образом.

Запараллеливгиотся входы обеих регистров 9 и 10 и подключаются к счет чику (не показан) , В1 дакхцему всевозможные k-разрядные комбинации, где Ц«1одАП); am- количество слов в на копителях 1 и 2.

Выходы накопителей 1 и 2 срсШН1Гваются поразрядно схемами 17 сравнения. Наличие хотя бы одного несовпадения вызывает нулевое значение сиг нала на выходе соответствующей ехеки 17 сравнения. Так как выходы всех

схем 17 сравнения объединены по моитгикномУ ИЛИ, то наличие хотя бы одного нуля на выходах схем 17 сравнеения обеспечивает нулевое значение сигнала на выходе 18, что и указьшает не неиспргшную ячейку памяти или сбой записи в указанную ячейку памяти.

Технико-экономические преимущества предлагаемого логического запоминающего устройства заключсцотся в том, что в нем одновременно формируются адреса двух операндов и операция считывания выполняется за один такт,

5 что повышает быстродействие устройства по сравнению с прототипом, и в более высокой надежности за счет 1вве дения диагностирования неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1981 |

|

SU960954A1 |

| Логическое запоминающее устройство | 1982 |

|

SU1024988A1 |

| Логическое запоминающее устройство | 1978 |

|

SU780042A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

О

О 14.

О

15,

1 16.

1

О О

1

X

1 1

Х/У

1 1

1 Формула изобретения Логическое запоминающее устройство, содержащее первый накопитель, адресные входы которого соединены с выходами первого дешифратора, входы которого подколочены к выходам первого регистра адреса, элем«2Нты И,входной и илходйой информационные регист ры и элемент ИЛИ, входы которого подключены соответственно к выходам элементов И, с первого по четвертый, первые входы которых являются управляющими входами устройства, отли чающееся тем, что, с целью повышения Сйлстродействия и надежности, в него введены второй накопитель второй дешифратор, второй регистр адреса, cxe№i сравнения, пятый и шес той элементы И, причем входы и выходы второго дешифратора а,цреса соединены соответственно с выходами второ го регистра адреса и с адресными входами второго накопителя, прямые и инверсные информационные входил накопителей подключены соответственно к прямым it инверсным выходам входного информационного регистра, одни и входов схем сравнения соединены с прямыми выходами первого накопителя и вторыми входами первого и второго элементов И, вторые входы третьего и четвертого элементов И подключены к инверсным выходам первого накопителя, другие входы схем сравнения соединены с третьими входами rtepBoro и третьего элементов И и прямыми выходами второго накопителя, инверсные выходы которого подключены к третьим входам второго и четвертого элемен,тов И, входы выходного информационноiro регистра соединены с выходами пятого и шестого элементов И, первые входы которых подключены к выходу элемента ИЛИ, а вторые входы объединены и являются входом разрушения записи устройства, выходё ш диагностики которого являются входы схем сравнения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 501421, кл. G 11 С 15/00, 1974. 2.Авторское свидетельство СССР W 760042, кл. G И С 15/00, 1980 (прототип),

Авторы

Даты

1982-10-30—Публикация

1981-04-14—Подача