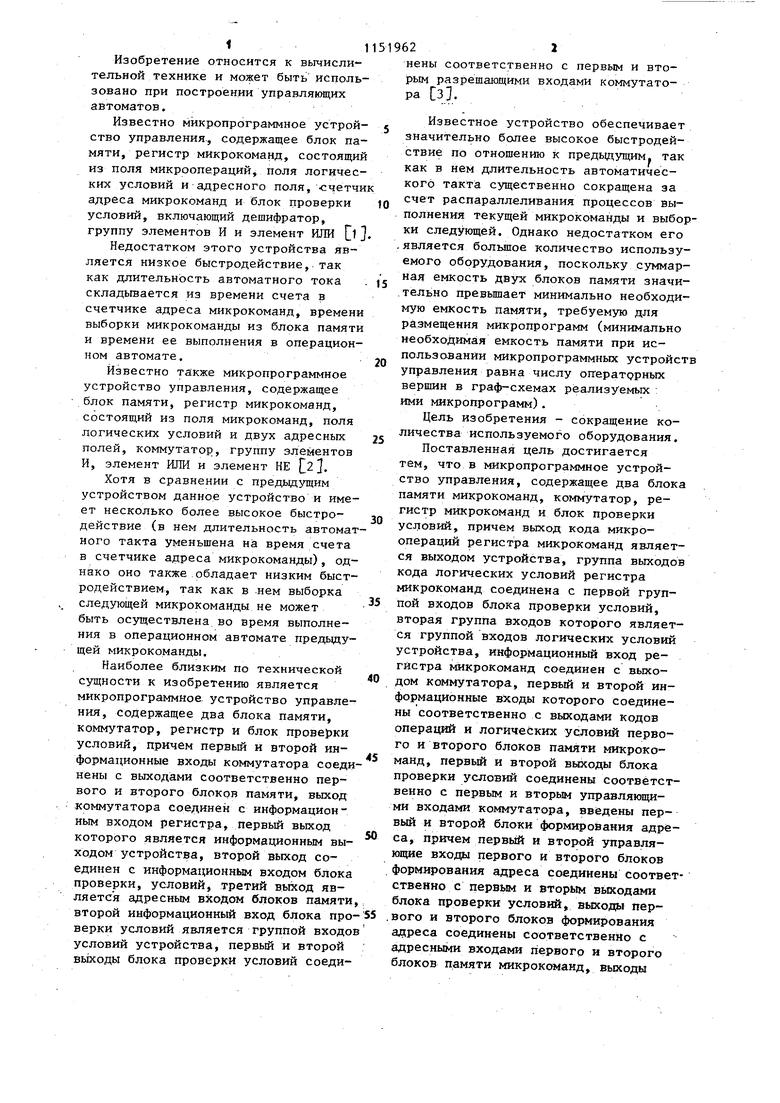

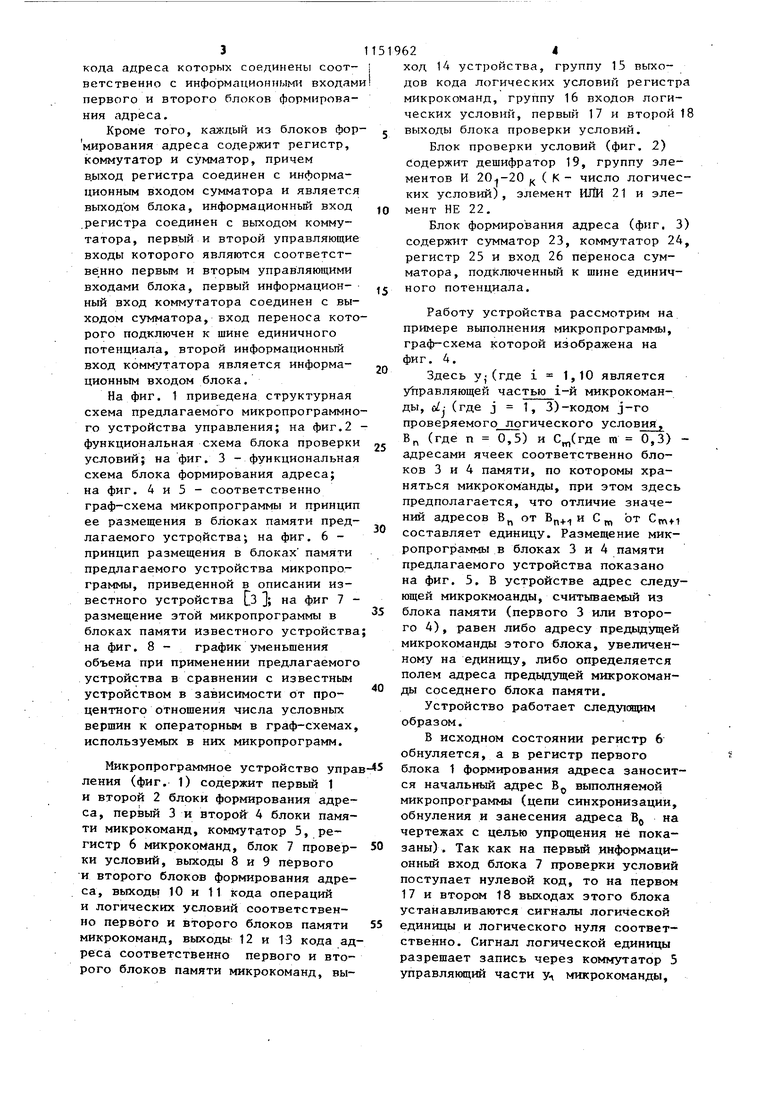

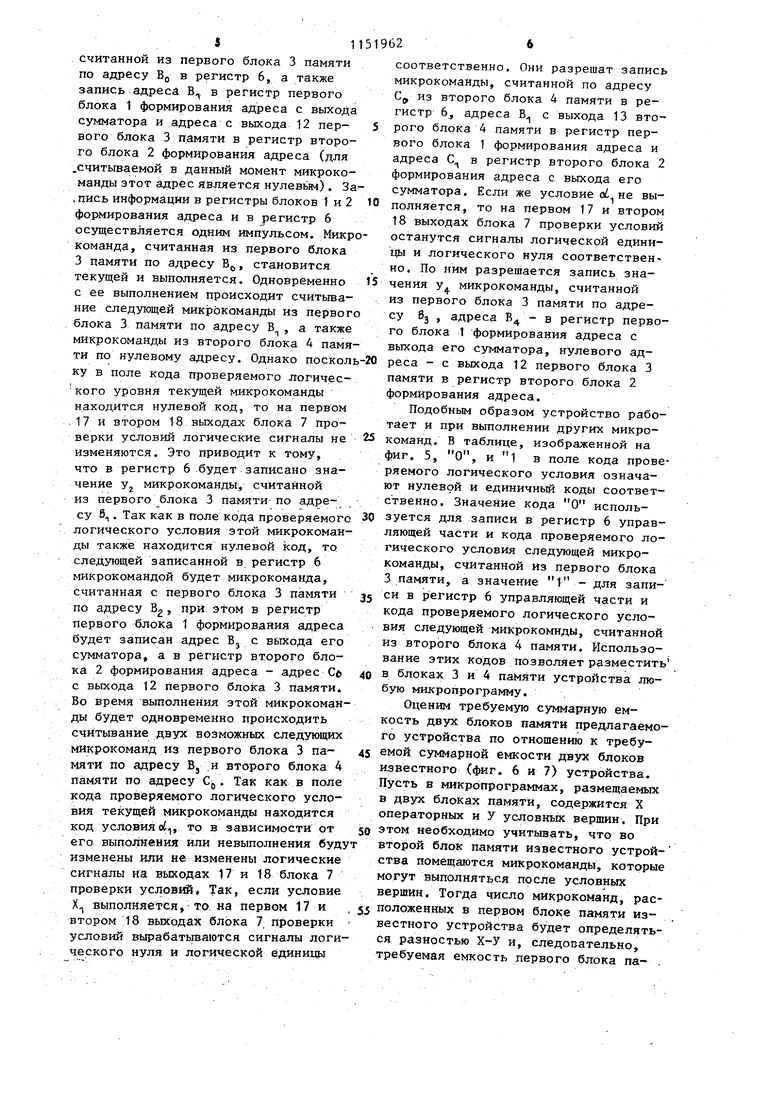

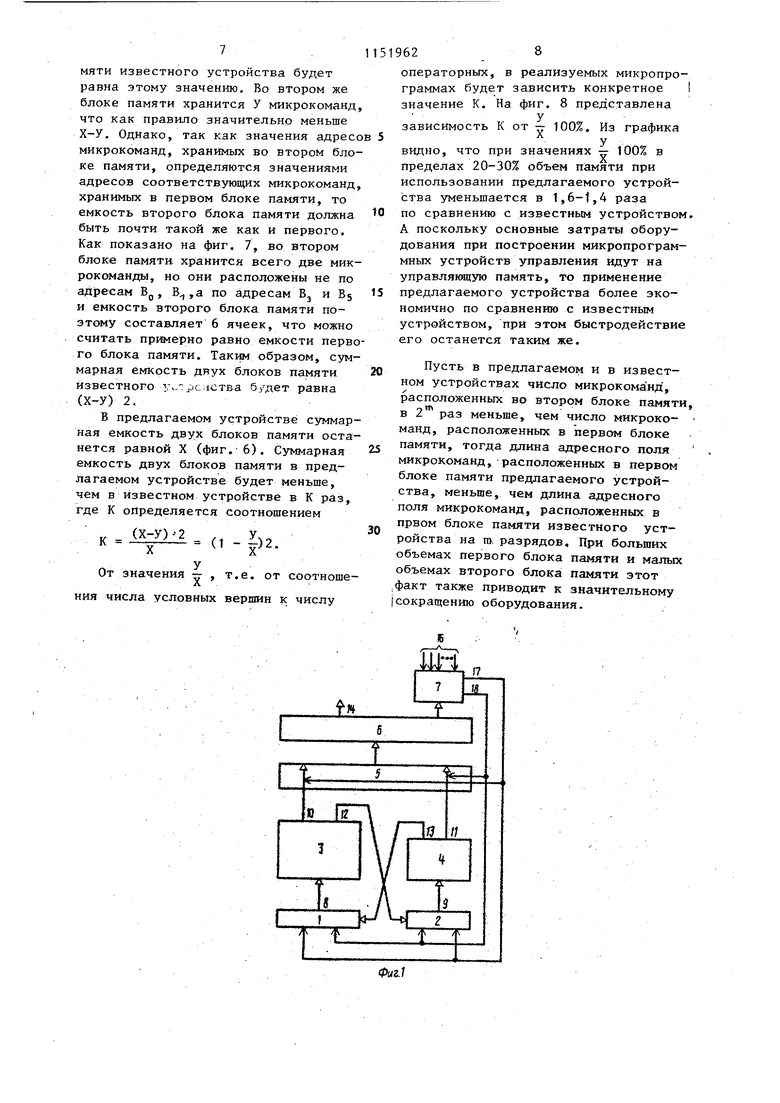

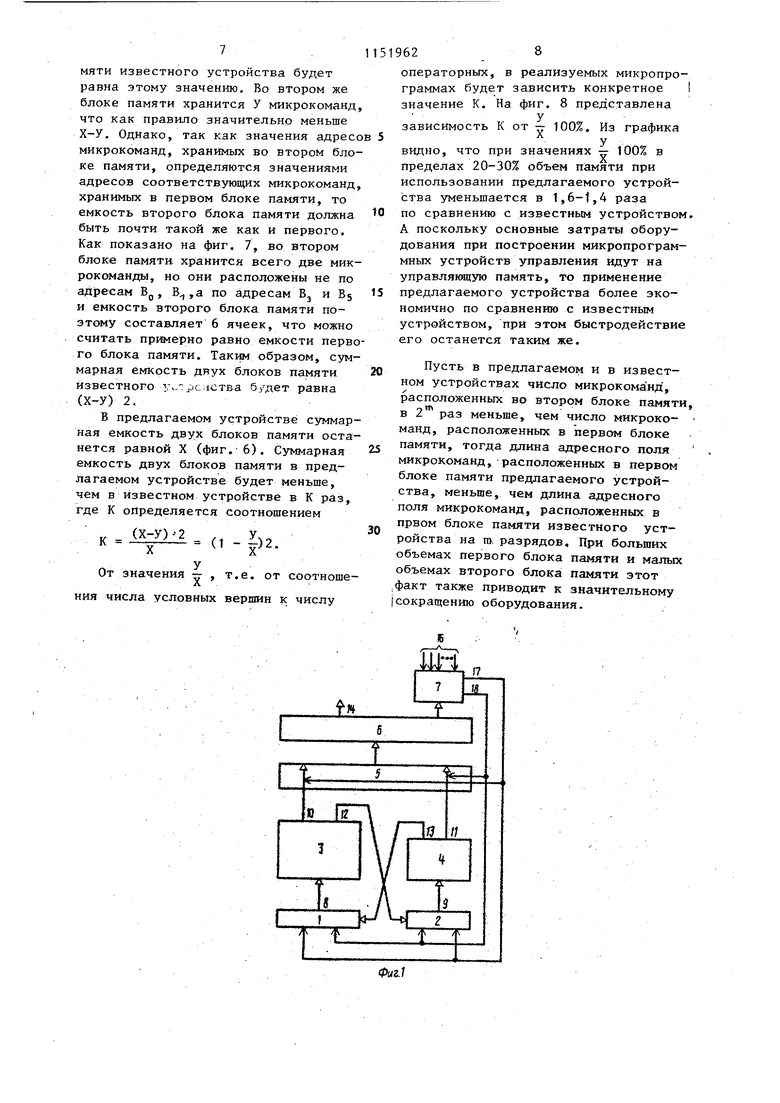

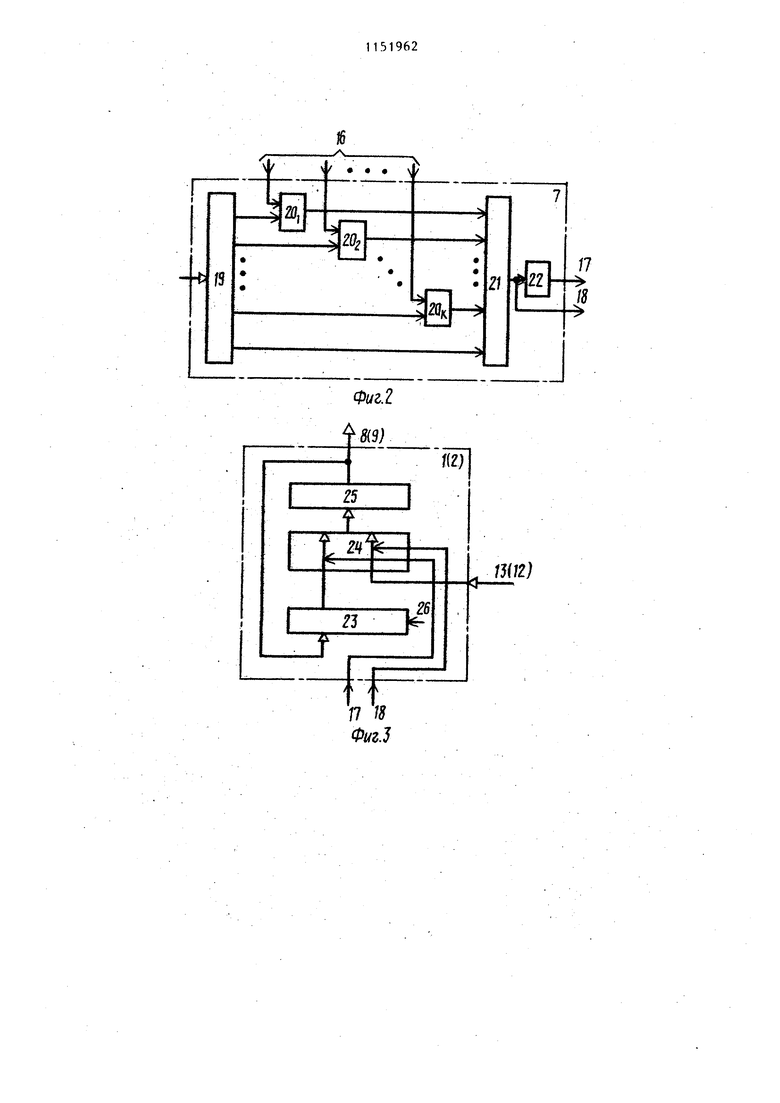

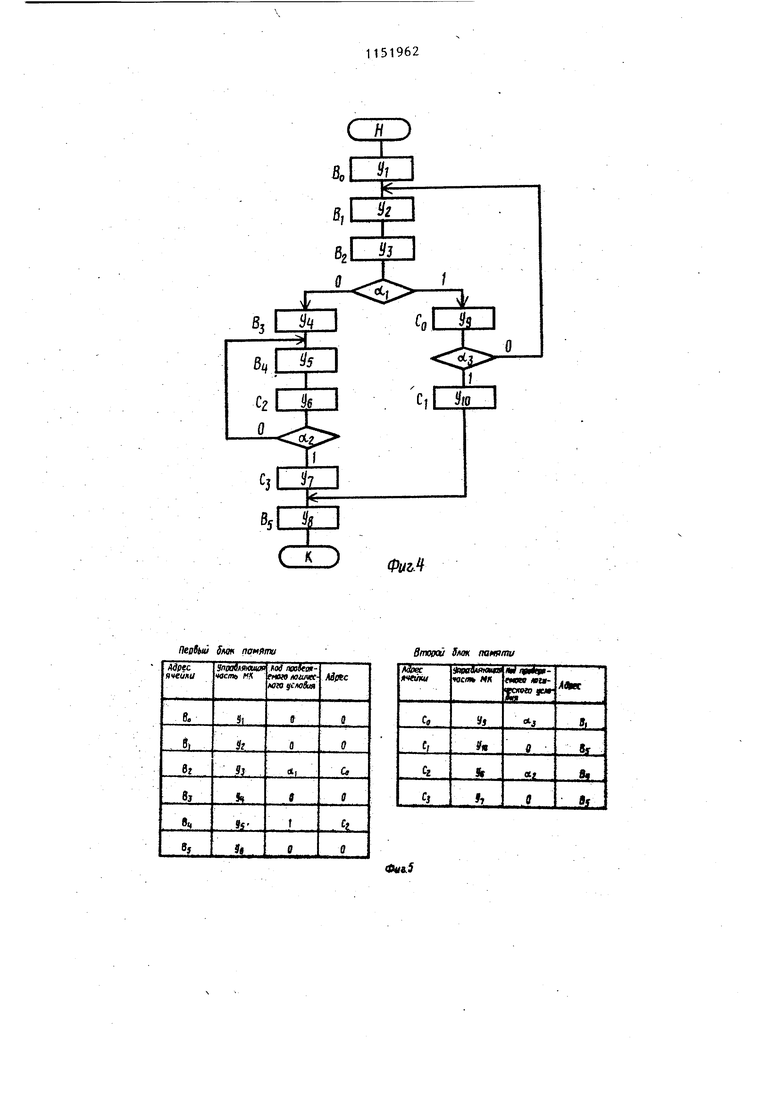

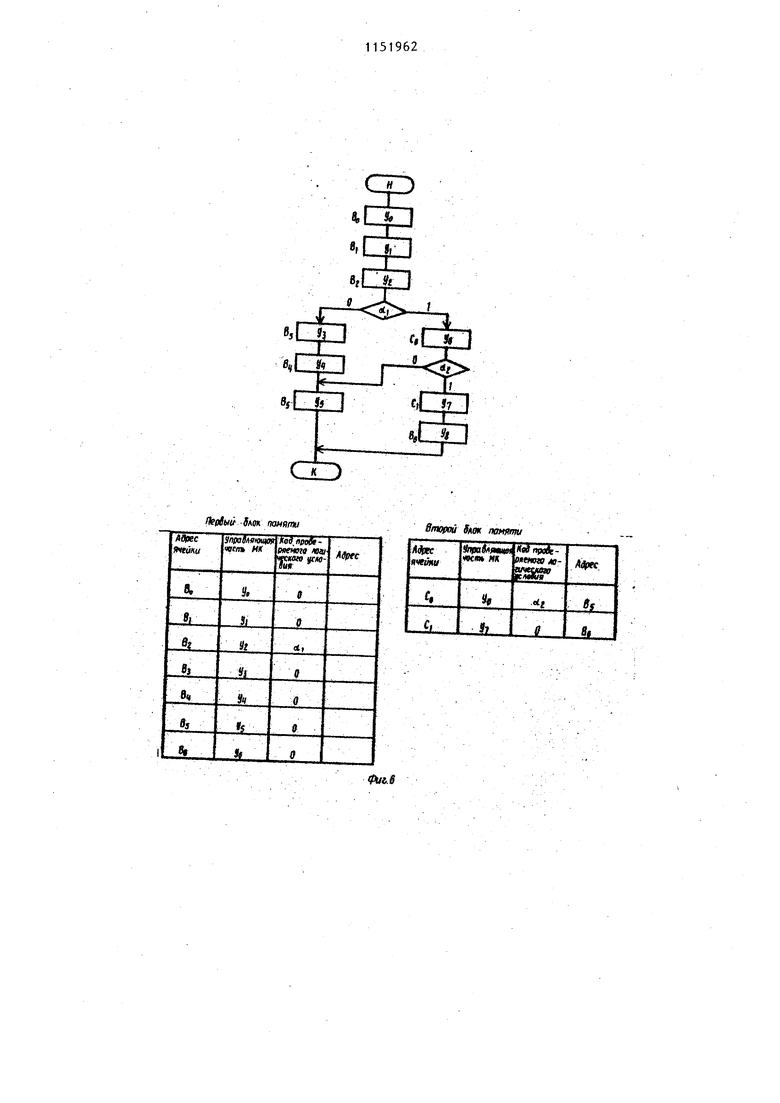

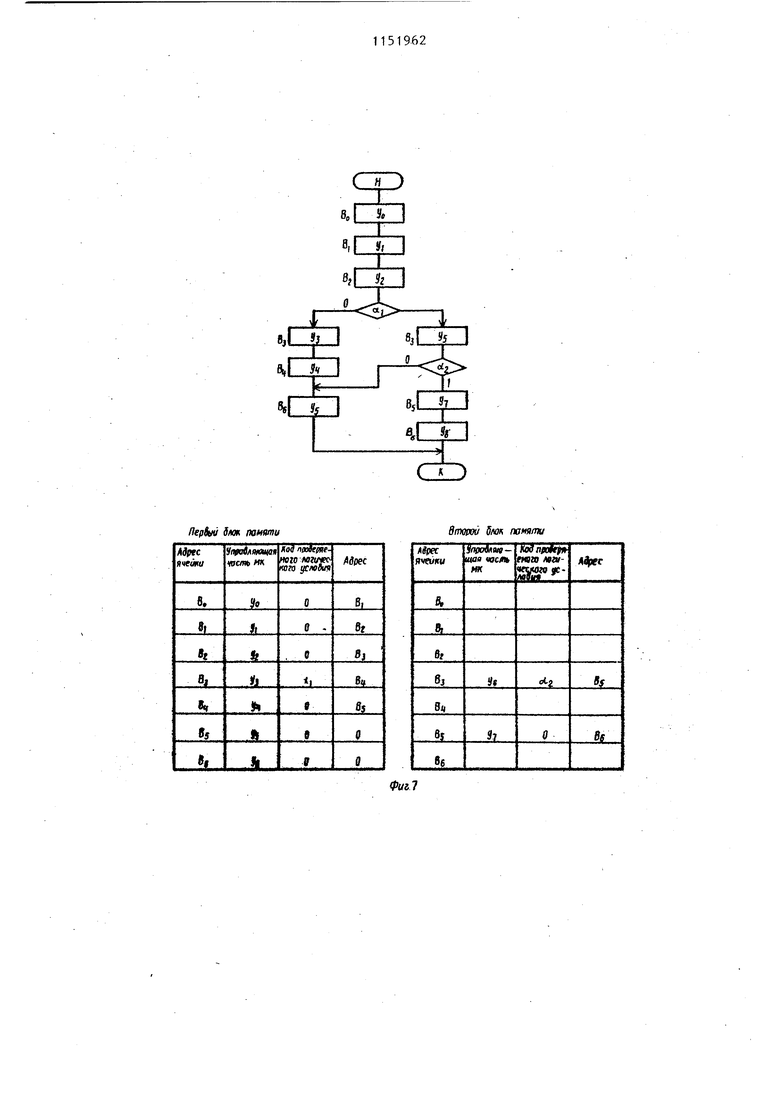

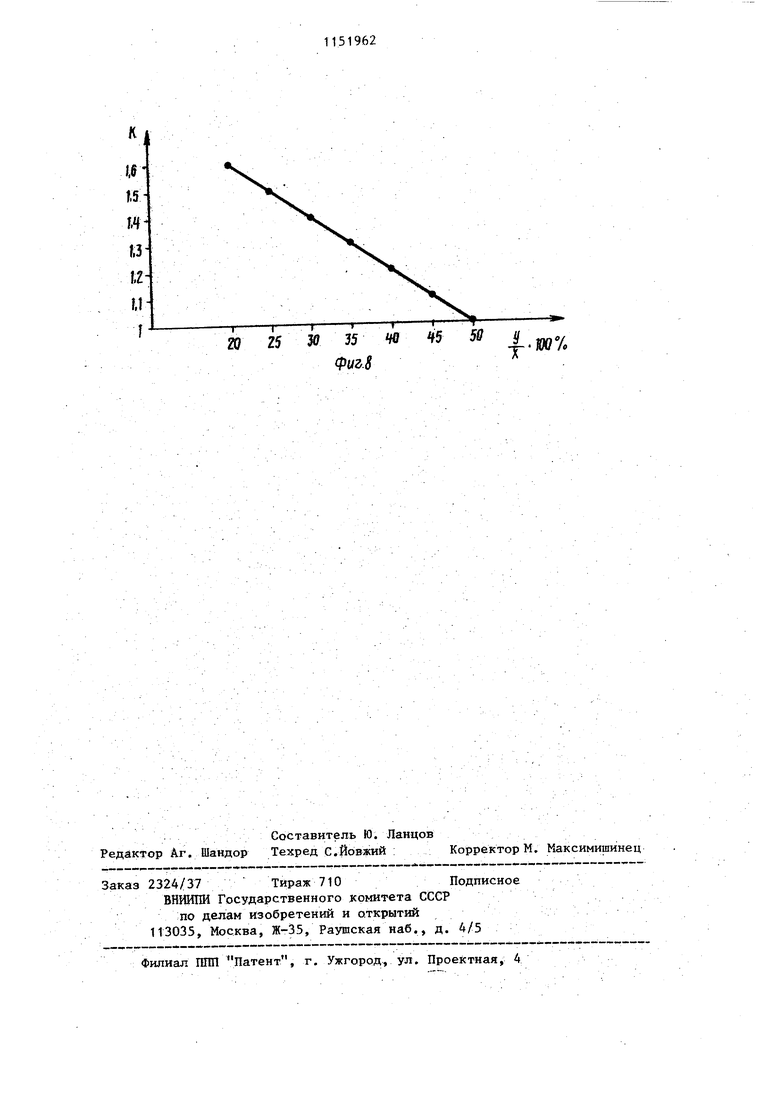

Изобретение относится к вычислительной технике и может быть использовано при построении управляющих автоматов. Известно микропрограммное устройство управления, содержащее блок памяти, регистр микрокоманд, состоящий из поля микроопераций, поля логических условий и адресного поля, счетчи адреса микрокоманд и блок проверки условий, включающий дешифратор, группу элементов И и элемент ИЖ 1 Недостатком этого устройства является низкое быстродействие,, так как длительность автоматного тока складьшается из времени счета в счетчике адреса микрокоманд, времени выборки микрокоманды из блока памяти и времени ее выполнения в операционном автомате. Известно также микропрограммное устройство управления, содержащее блок памяти, регистр микрокоманд, состоящий из поля микрокоманд, поля логических условий и двух адресных полей, коммутатор, группу элементов И, элемент ИЛИ и элемент НЕ L2J. Хотя в сравнении с предыдущим устройством данное устройство и имеет несколько более высокое быстродействие (в нем длительность автомат ного такта уменьшена на время счета в счетчике адреса микрокоманды), однако оно также обладает низким быстродействием, так как в нем выборка следующей микрокоманды не может быть осуществлена во время выполнения в операционном автомате предьщущей микрокоманды. Наиболее близким по технической сущности к Изобретению является микропрограммное устройство управления, содержащее два блока памяти, коммутатор, регистр и блок проверки условий, причем первый и второй информационные входы коммутатора соеди нены с выходами соответственно первого и второго блоков памяти, выход коммутатора соединен с информационным входом регистра, первый выход которого является информационным выходом устройства, второй выход соединен с информационным входом блока проверки, условий, третий выход является адресным входом блоков памяти второй информационный вход блока про верки условий является группой входо условий устройства, первый и второй выходы блока проверки условий соеди2Jнены соответственно с первым и втоipbiM разрешающими входами коммутатора 3J. Известное устройство обеспечивает значительно более высокое быстродействие по отношению к предыдущим, так как в нем длительность автоматического такта существенно сокращена за счет распараллеливания процессов выполнения текущей микрокоманды и выборки следующей. Однако недостатком его является большое количество используемого оборудования, поскольку суммарная емкость двух блоков памяти значительно превьшает минимально необходимую емкость памяти, требуемую для размещения микропрограмм (минимально необходимая емкость памяти при использовании микропрограммных устройств управления равна числу операторных вершин в граф-схемах рё ализуемых : ими микропрограмм). Цель изобретения - сокращение количества используемого оборудования. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее два блока памяти микрокоманд, коммутатор, регистр микрокоманд и блок проверки условий, причем выход кода микроопераций регистра микрокоманд является выходом устройства, группа вьпсодов кода логических условий регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, информационный вход регистра микрокоманд соединен с выходом коммутатора, первый и второй информационные входы которого соединены соответственно с выходами кодов операций и логических условий первого и второго блоков памяти микрокоманд, первый и второй выходы блока проверки условий соединены соответственно с первым и вторым управляющими входами коммутатора, вв1едены первый и второй блоки формирования адреса, причем первый и второй управляющие входы первого и второго блоков формирования адреса соединены соответственно с первым и вторым выходами блока проверки условий, выходь первого и второго блоков формирования адреса соединены соответственйо с адресными входами первого и второго блоков памяти микрокоманд, выходы кода адреса которых соединены соответственно с информационными входам первого и второго блоков формирования адреса. Кроме того, каждый из блоков фор мирования адреса содержит регистр, коммутатор и сумматор, причем В.ЫХОД регистра соединен с информационным входом сумматора и является выходом блока, информационньй вход регистра соединен с выходом коммутатора, первый и второй управляющие входы которого являются соответстве нно первым и вторым управляющими входами блока, первый информационный вход коммутатора соединен с выходом сумматора, вход переноса кото рого подключен к шине единичного потенциала, второй информационный вход коммутатора является информационным входом блока. На фиг. 1 приведена структурная схема предлагаемого микропрограммно го устройства управления; на фиг.2 функциональная схема блока проверки условий; на фиг. 3 - функциональная схема блока формирования адреса; на фиг. 4 и 5 - соответственно граф-схема микропрограммы и принцип ее размещения в блоках памяти предлагаемого устройства; на фиг. 6 принцип размещения в блоках памяти предлагаемого устройства микропрограммы, приведенной в описании известного устройства L3 J; на фиг 7 размещение этой микропрограммы в блоках памяти известного устройства на фиг. 8 - график уменьшения объема при применении предлагаемого устройства в сравнении с известным устройством в зависимости от процентного отношения числа условных вершин к операторным в граф-схемах используемых в них микропрограмм. Микропрограммное устройство упра ления (фиг. 1) содержит первый 1 и второй 2 блоки формирования адреса, первый 3 и второй 4 блоки памяти микрокоманд, коммутатор 5, регистр 6 микрокоманд, блок 7 проверки условий, выходы 8 и 9 первого и второго блоков формирования адреса, выходы 10 и 11 кода операций и логических условий соответственно первого и второго блоков памяти микрокоманд, выходы 12 и 1:3 кода ад реса соответственно первого и второго блоков памяти микрокоманд, выход 14 устройства, группу 15 выходов кода логических условий регистра микрокоманд, группу 16 входов логических условий, первый 17 и второй 18 выходы блока проверки условий. Блок проверки условий (фиг. 2) Содержит дешифратор 19, группу элементов И / ( К - число логических условий), элемент ИЛИ 21 и элемент НЕ 22. Блок формирования адреса (фиг, 3) содержит сумматор 23, коммутатор 24, регистр 25 и вход 26 переноса сумматора, подключенный к шине единичного потенциала. Работу устройства рассмотрим на примере выполнения микропрограммы, граф-схема которой изображена на фиг. 4. Здесь у{(где i 1,10 является Управляющей частью i-й 1 шкрокоман- ды, d: (где j 1, 3)-кодом j-ro проверяемого логического условия, В г, (где п 0,5) и С„(где m 0,3) адресами ячеек соответственно блоков 3 и 4 памяти, по которомы храняться микрокоманды, при этом здесь предполагается, что отличие значений адресов В„ от и С от С, составляет единицу. Размещение микponporpaMhfti в блоках 3 и 4 памяти предлагаемого устройства показано на фиг. 5, В устройстве адрес следующей микрокмоанды, считываемый из блока памяти (первого 3 или второго 4), равен либо адресу предыдущей микрокоманды этого блока, увеличенному на единицу, либо определяется полем адреса предыдущей микрокоманды соседнего блока памяти. Устройство работает следу1сяцим образом. В исходном состоянии регистр 6 обнуляется, а в регистр первого блока 1 формирования адреса заносится начальный адрес B,j выполняемой микропрограммы (цепи синхронизации, обнуления и занесения адреса В на чертежах с целью упрощения не показаны) . Так как на первый информационный вход блока 7 проверки условий поступает нулевой код, то на первом 17 и втором 18 выходах этого блока устанавливаются сигналы логической единицы и логического нуля соответственно. Сигнал логической единицы разрешает запись через коммутатор 5 управляющий части у микрокоманды. считанной из первого блока 3 памяти по адресу Bj, в регистр 6, а также запись адреса В. в регистр первого блока t формирования адреса с выхода сумматора и адреса с выхода 12 первого блока 3 памяти в регистр второго блока 2 формирования адреса (для .считываемой в данный момент микрокоманды этот адрес является нулевь м) . За , пись информации в регистры блоков f и 2 формирования адреса и в регистр 6 осуществляется одним импульсом. Микр команда, считанная из первого блока 3 памяти по адресу Ъ, становится текущей и выполняется. Одновременно с ее выполнением происходит считывание следующей микрокоманды из первог блока 3 памяти по адресу Б, а также микрокоманды из второго блока 4 памя ти по нулевому адресу. Однако поскол ку в поле кода проверяемого логического уровня текущей микрокоманды находится нулевой код, то на первом -17 и втором t8 выходах блока 7 проверки условий логические сигналы не изменяются. Это приводит к тому, что в регистр 6 будет записано значение у,, микрокоманды, считанной из первого блока 3 памяти по адресу 6,. Так как в поле кода проверяемого логического условия этой микрокоманды также находится нулевой код, то следующей записанной в. регистр 6 микрокомандой будет микрокоманда, считанная с первого блока 3 памяти по адресу В, при этом в регистр первого блока 1 формирования адреса будет записан адрес В с выхода его сумматора, а в регистр второго блока 2 формирования адреса - адрес Се с выхода 12 первого блока 3 Памяти. Во время выполнения этой микрокоманды будет одновременно происходить считывание двух возможных следующих микрокоманд из первого блока 3 памяти по адресу В, .и второго блока 4 памяти по адресу Cj. Так как в иоле кода проверяемого логического условия текущей микрокоманды находится код условияЫ, то в зависимости от его выполнения или невыполнения буд изменены или не изменены логические сигналы на вькодах 17 и 18 блока 7 проверки условий. Так, если условие Х выполйяется,-то на первом 17 и втором :i8 вь1ходах блока 7. проверки условий вырабатываются сигналы логи ческого нуля и логической единицы соответственно. Они разрешат запись микрокоманды, считанной по адресу С из второго блока 4 памяти в регистр 6, адреса В с выхода 13 второго блока 4 памяти в регистр первого блока 1 формирования адреса и адреса Ц в регистр второго блока 2 формирования адреса с выхода его сумматора. Если же условие oi не выполняется, то на первом 17 и втором 18 выходах блока 7 проверки условий останутся сигналы логической единицы и логического нуля соответственно. По ним разрешается запись значения у микрокоманды, считанной из первого блока 3 памяти по адресу Bj , адреса В. - в регистр первого блока 1 формирования адреса с выхода его сумматора, нулевого адреса - с выхода 12 первого блока 3 памяти в регистр второго блока 2 формирования адреса. Подобным образом устройство работает и при выполнении других микрокоманд. В таблице, изображенной на фиг. 5, О, и 1 в поле кода проверяемого логического условия означают нулевой и единичньй коды соответственно. Значение кода О используется для записи в регистр 6 управляющей части и кода проверяемого логического условия следующей микрокоманды, считанной из первого блока 3 памяти, а значение 1 - для записи в регистр 6 управляющей части и кода проверяемого логического условия следующей микрокомнды, считанной из второго блока 4 памяти. Использование этих кодов позволяет разместить в блоках 3 и 4 памяти устройства любую микропрограмму. Оценим требуемую суммарную емкость двух блоков памяти предлагаемого устройства по отношению к требуемой суммарной емкости двух блоков известного (фиг. 6 и 7) устройства. Пусть в микропрограммах, размещаемых в двух блоках памяти, содержится X операторных и У условньк вершин. При этом необходимо учитывать, что во второй блок памяти известного устройства помещаются микрокоманды, которые могут выполняться после условных вершин. Тогда число микрокоманд, расположенных в первом блоке памяти известного устройства будет определяться разностью Х-У и, следовательно, требуемая емкость первого блока па- . 7, мяти известного устройства будет равна этому значению. Во втором же блоке памяти хранится У микрокоманд что как правило значительно меньше Х-У, Однако, так как значения адресо микрокоманд, хранимых во втором блоке памяти, определяются значениями адресов соответствующих микрокоманд хранимых в первом блоке памяти, то емкость второго блока памяти должна быть почти такой же как и первого. Как показано на фиг. 7, во втором блоке памяти хранится всего две микрокоманды, но они расположены не по адресам В, В,а по адресам Bj и БЗ и емкость второго блока памяти поэтому составляет 6 ячеек, что можно считать примерно равно емкости перво го блока памяти. Таким образом, суммарная емкость двух блоков памяти Известного у,рсаства будет равна (Х-У) 2. В предлагаемом устройстве суммар ная емкость двух блоков памяти останется равной X (фиг.6). Суммарная емкость двух блоков памяти в предлагаемом устройстве будет меньше, чем в известном устройстве в К раз, где К определяется соотношением (Х-У)--2 (1 - )2. От значения - , Т.е. от соотношения числа условных вершин к числу операторных, в реализуемых микропрограммах будет зависить конкретное I значение К. На фиг. 8 представлена У зависимость К от - 100%. Из графика видно, что при значениях - 100% в пределах 20-30% объем памяти при использовании предлагаемого устройства уменьшается в 1,6-1,4 раза по сравнению с известным устройством. А поскольку основные затраты оборудования при построении микропрограммных устройств управления идут на управляющую память, то применение предлагаемого устройства более экономично по сравнению с известным устройством, при этом быстродействие его останется таким же. Пусть в предлагаемом и в известном устройствах число микрокома нд, расположенных во втором блоке памяти, в 2 раз меньше, чем число микроко- манд, расположенных в первом блоке памяти, тогда длина адресного поля микрокоманд, расположенных в первом блоке памяти предлагаемого устройства, меньше, чем длина адресного поля микрокоманд, расположенных в првом блоке памяти известного устройства на m разрядов. При больших объемах первого блока памяти и малых объемах второго блока памяти этот факт также приводит к значительному сокращению оборудования.

J6 /S---

N

-ф

/7

Zf

IS

I I

tf

(

Фиг.2 M-

flzj

i

im)

2S

fi

/7 /5 .5

CAD

ФцъЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1381503A1 |

| Многопрограммное устройство управления | 1984 |

|

SU1231501A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1257645A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU985787A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1015384A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

1. МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее два блока памяти, микрокоманд, коммутатор, регистр микрокоманд и блок проверки условий, причем выход кода микроопераций регистра микрокоманд является выходом устройства, группа выходов кода логических условий регистра микрокоманд соединена с первой группой входов блока проверки условий, вторая группа входов которого является группой входов логических условий устройства, информационный вход регистра микрокоманд соединен с выходом коммутатора, первый и второй информационные входы которого соединены соответственно с выходами кодов операций и логических условий первого и второго блоков памяти микрокоманд, первый и второй выходы блока проверки условий соединены соответственно с первым и вторым управляющими входами коммутатора, отличающееся тем, что, с целью сокращения оборудования, оно содержит первьй и в.торой блоки формирования адреса, причем, первый и второй управляющие входы первого и второго блоков формирования адреса соединены соответственно с первым и вторым выходами блока проверки условий, выходы первого и второго блоков формирования адреса соединены соответственно с адресными входами первого и второго блоков памяти микрокоманд, выходы кода адреса которых соединены соответственно с информационными вхо(Л дами первого и второго блоков формирования адреса. 2. Устройство по п. 1, отличающее с я тем, что каждый из блоков формирования адреса содержит регистр, коммутатор и сумматор, причем выход регистра соединен с информационным входом сумматора и являел ется выходом блока, информационный вход регистра соединен с выходом со коммутатора, первый и второй управОд ляющие входы которого являются соотtc ветственно первым и вторым управляющими входами блока, первый информационный вход коммутатора соединен с выходом сумматора, вход переноса которого подключен к шине единичного потенциала, второй информационный вход коммутатора является информа- ,ционным входом блока.

flepSbiu Sfw побита

второй SMK паняти

fkptuif памяти

Bmopw SKOK namtmu

В.1 9з I

ПерМ длаи паняти

-гул

ип

второй SflOK «7IW/W

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Майоров С.А., Новиков Г.И | |||

| Структура ЭВМ.Л., Машиностроение, 1979, с | |||

| Обогреваемый отработавшими газами карбюратор для двигателей внутреннего горения | 1921 |

|

SU321A1 |

| Счетный сектор | 1919 |

|

SU107A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электронные вычислительные устройства, Минск, Вышэйшая школа, 1981, с | |||

| Синхронизирующее устройство для аппарата, служащего для передачи изображений на расстояние | 1920 |

|

SU225A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-23—Публикация

1983-09-19—Подача