Изобретение относится к вычислительной технике и может применяться при пострюении высокопроизводительных вычислительных систем.

Известна вычислительная система, содержащая процессоры и групповой переключатель, через которьлй группа процессоров подключается к межгрупповой шине 1 .

Недостатками данной вычислительной системы являются длительное время и большая сложность процесса формиро-вания связи между процессорами, расположенными в разных группах/ что определяется централизацией функций управления обменом информацией чере,з . межгрупповую шину. По этой же причине уменьшается эффективность всей системы, поскольку сокращается удельный вес задач вычислительного характера, . решаемых группой - диспетчером, а также имеет место практическое ограничение числа групп процессоров, объединенных в систему с помощью меж-. групповой шины.

Наиболее близким по технической сущности к предлагаемому является вычислительная система, содержащая, вычислительные машины и модули комт«1утации 2 . ,

Недостатком системы является низкие эффективность и надежность, а также сложность наращивания ресурса, с так как требуются значительные затраты аппаратных и программных средств.

Цель изобретения - повышение надежности, гибкости и эффективности за счет возможности наращивания чис10ла вычислительных машин.

Поставленная цель достигается тем тем, что в многопроцессорную вычислительную систему, содержащую группы вычислительных машин и один уровень

15 модулей коммутации, причем вычислительные машины каждой группы соединенены через шины связи с соответствующим модулем коммутации, введены дополнительные уровни модулей коммута20ции, причем на каждом уровне модули коммутации объединены в группы и модули коммутации каждой группы более низкого уровня соединены через шины связи с соответствующим модулем ком25мутации более высокого уровня.

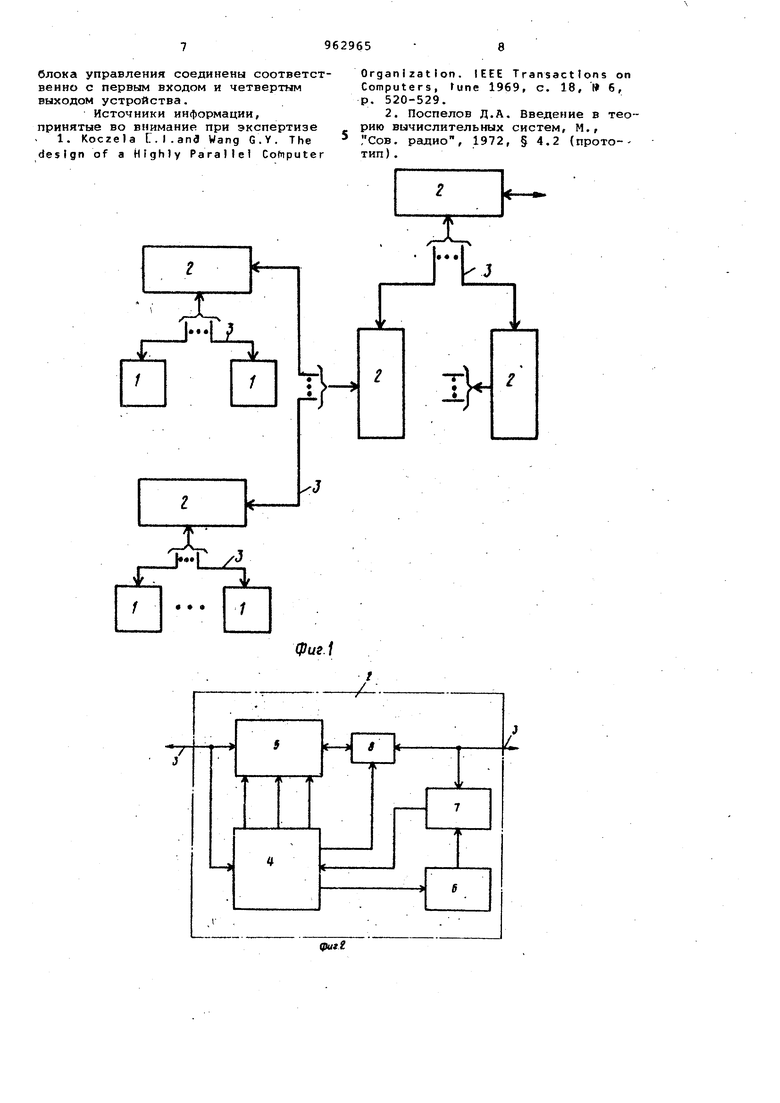

Каждый модуль коммутации содержит устройство управления коммутацией, управляемый двунаправленный коммутатор, память, блок сравнения и блок

30 элементов И, причем первые три выхода устройства управления коммутацией соед..нены с входами управляемоо двунаправленного коммутатора, соединенного двусторонней связью с блоком элементов И, вход которого соединен с четвертым выходом устройства 5

управления коммутацией, пятый выход которого через память соединен с входом блока сравнения, выход которого соединен с первым входом устройства управления коммутацией, второй 10 вход которого и управляемый двунаправленный коммутатор соединены с одной шиной связи модуля коммутации, блок сравнения и блок элементов И соединены с другой шиной связи моду- ля коммутации.

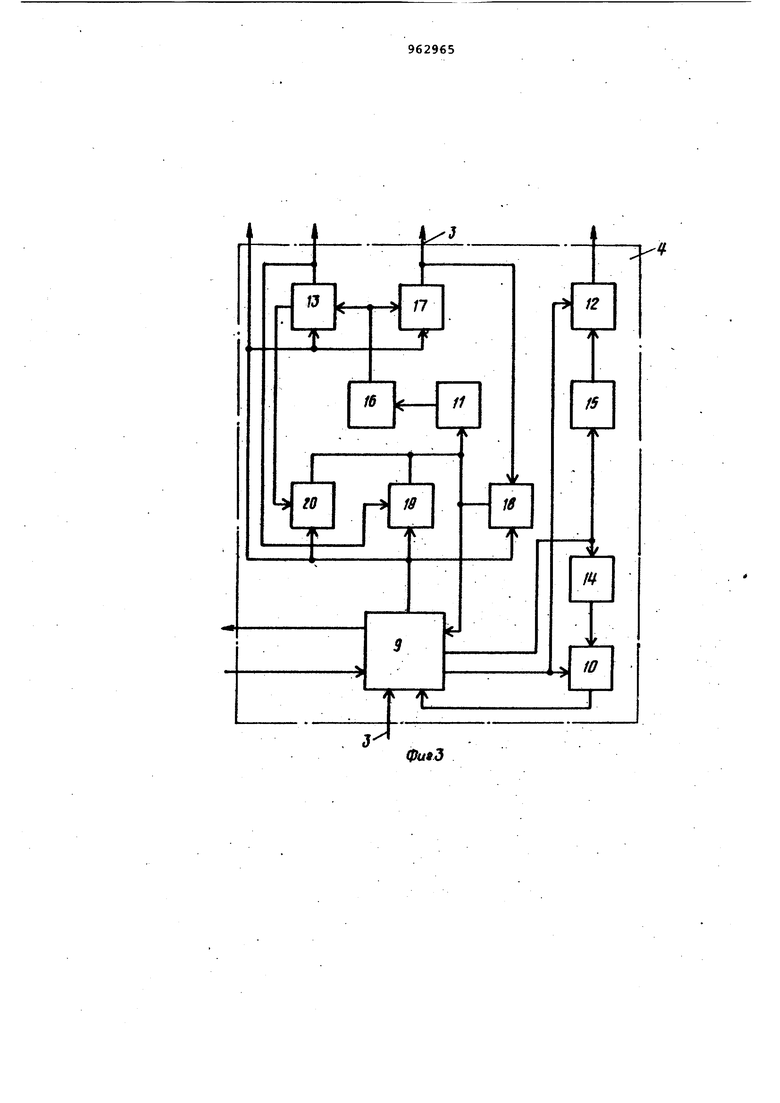

Устройство управления коммутацией содержит блок управления, первый вход которого соединен с вторым входом устройства, первый выход олока управления соединен с первым выходом уст- 20 ройства и первыми входами первого, второго и третьего элементов И, первого регистра указателей и регистра фиксации пути, выход которого соединен с третьим выходом устройства и 25

вторым входом первого элемента И,первый выход первого регистра указателей соединен с вторым выходом устройства и вторым входом второго, элемента И, второй выход первого регистра ука-30 зателей соединен с вторым входом третьего элемента И, выходы элементов И соединены с вторым входом блока управления и через последовательно соединенные первый приоритетный блок и 35 дешифратор с вторыми входами регистра фиксации пути и первого регистра указателей, второй выход блока управлеия соединен с.первыми входами второго приоритетного блока и узла опреДе-40 ления числа единиц, третий выход блока управления соединен с входами регистра свободных узлов и второго регистра указателей, выход которого через узел определения числа единиц г соединен с третьим входом блока управления, выход регистра свободных узлов через второй приоритетный блок соединен с пятым выходом устройства, . четвертые вход и выход блока управ-. „ ления соединены соответственно с пер-50 вым входом и четвертым выходом устройства.

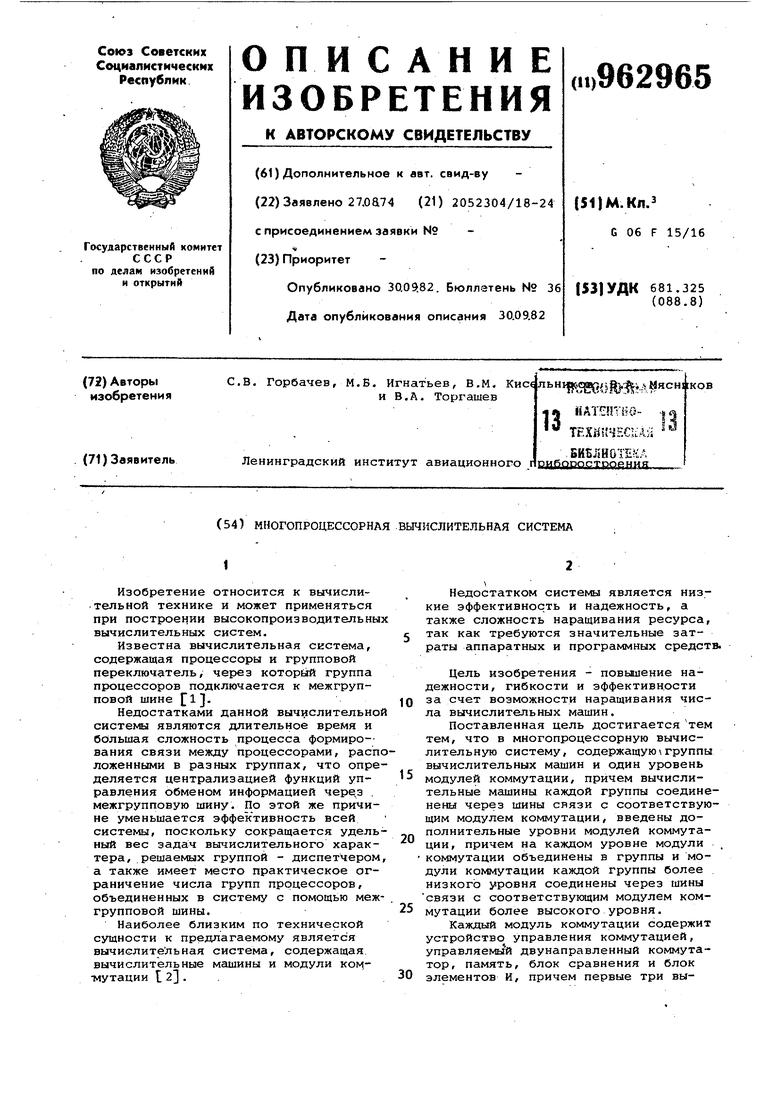

На фиг. 1 приведена структурная схема многопроцессорной вычислительной системы; на фиг. 2 - структурная 55 схема модуля 2 коммутации на фиг.Зструктуркая схема устройства управления коммутацией} на фиг. 4 - пример выполнения структурной схемы блока управления.60

Многопроцессорная вычислительная система содержит вычислительную машину 1, модуль 2 коммутации, шины 3 связи, модуль 2 коммутации содержит устройство 4 управления коммутацией, 65

управляемый двунаправленный коммутатор 5, память 6, блок 7 сравнения, блок 8 элементов И, устройство 4 управления коммутацией состоит из блока 9 управления, узла 10 определения числа единиц, приоритетных блоков , 11 и 12, регистров 13 и 14, регистра 15 свободных узлов, дешифратора 16, регистра 17 фиксации пути и элементов и 18-20, блок 9 управления состоит из регистра.21 микрокоманд, дешифратора 22, коммутаторов 23-26, моди фикатора 27 адреса и памяти 28.

Многопроцессорная вычислительная система работает следующим образом.

Модули 2 коммутации образуют многоуровневое устройство с регулярной структурой связей для коммутации вычислительных машин 1. Через шиныЗ к каждому модулю подключаются либо вычислительные машины 1, либр другие г эдули 2 более нижнего уровня. Активные процессори могут устанавливать соединения с свободными процес.сорами для подстройки внутренней структуры системы под структуру решаемой зддачи через модули 2 с помощью волновых команд поиска к свободным процессорам. При поступлении в модуль 2 по шине 3 волновых команд поиска пути блок 9 выдает их со своего выхода на приоритетный блок 11, который выделяет самую приоритетную входную линию и формирует ее двоичный код. Двоичный код приоритетного входа, по которому поступает волновая /команда поиска пут, преобразуется дешифратором 16 в унитарный код и записывается в, регистр 13.Код с выхода регистра 13. через элемент И 19 поступаем в блок 9 для передачи его в предшествующий модуль 2 коммутации более низкого уровня с целью подтверждения принятия к исполнению волновой команды. Инверсный код с выхода регистра 13 через элемент И 20 аналогичным образом передается в модули 2 коммутации предшествующего уровня в качестве квитанции отказа на установление соединения. Выделенная команда поиска через управляемый двунаправленный коммутатор 5 по всем свободным линиям выдается в модули 2 следующих уровней, где алгоритм ее обработки аналогичен описанному. После того, как команда поиска пути дойдет до свободного процессора, последний выдает команду фиксации пути, которая обеспечивает закрепление .соединения через управляемый двунаправленный коммутатор 5 посредством записи унитарного кода закрепляемой линии в регистре 17. Код с выхода регистра 17 через Элемент И 18 поступает в/блок 9 и используется для передачи в предшествующий модуль 2 для фиксации соединения. Таким образом всегда обеспечивается установление связи с ближайшим свободным процессором, поскольку команда фиксации пути от него придет раньше и заблокирует возможность установления соединений по дру .гим направлениям, которые в данном случае соответствуют более длинным связям. Для обеспечения возможности межпроцессорного обмена более двух процессоров в модуле 2 коммутации может быть организовано разветвление типа дерева. Для этого в соответствующий регистр памяти б записывается нрмер уровня, который хранится в регистре 13 и считывается блоком 9 через узел 10, а также номер очередного узла на данном уровне, который считывается из регистра 15 и выделяется приоритетным блоком 12. При обращении к соответствующему процессору по номеру узла на данном уровне блок 7 выявляет совпадение его с кодом, хранящимся в одном из регистров памяти 6, при этом на одном из ее вы ходов вырабатывается соответствующий сигнал. По этому сигналу блок 9 подключает через один из элементов И блока 8 выделенную ветку к основному каналу для обеспечения соединения ве дущего процессора с необходимым ему ведомым процессором, связь с которым была установлена ранее. Таким образом, изобретение облада ет высокой надежностью, поскольку от ,казы отдельных процессоров не наруша ют нормального функционирования всей системы в целом, а могут привести лишь к некоторым потерям в быстродей ствии или объеме оператив ой памяти. В изобретении обеспечивается гибкая перенастройка межпроцессорных связей для отображения в структуре вычислительной системы структуры, данных и программ на языке высокого уровня. За счет подключения неограниченного числа процессоров без изменения пара метров элементов системы и ранее существующей структуры связей между элементами в предлагаемом изобретении достигается значительное повышение эффективности вычислительной сиетемы. Формула изобретения 1. Многопроцессорная вычислительная система, содержащая группы вычислительных машин и один уровень модулей коммутации, причем вычислительные машины каждой группы соединены через шины связи с соответствующим модулем коммутации, отличающаяся тем, что, с целью повышения надежности, гибкости и эффективности за счет .возможности наращивания числа процессоров , в нее введены дополнительные уровни модулей коммутации, причем на каждом уровне модули коммутации объединены в группы и модули коммутации каждой группы более низкого уровня соединены через шины связи с соответствующим модулем коммутации более высокого уровня. 2.Система по п. 1,отличаю щ а я с я тем, что каждый модуль коммутации содержит устройство управления коммутацией, управляер.1ый двуна правленный коммутатор, память, блок сравнения и блок элементов И, причем первые три выхода устройства управления коммутацией соединены с входами управляемого двунаправленного коммутатора, соединенного двусторонней связью с блоком элементов И,вход .которого соединен с четвертым выходом устройства управления коммутацией, . пятый выход которого через память соединен с входом блока сравнения, выход которого соединен с первым входом устройства управления коммутацией, второй вход которого и управляющий двунаправленный коммутатор соединены с одной шиной связи модуля коммутации, блок сравнения и блок элементов И соединены с другой шиной связи модуля коммутации. 3.Система rfon. 2, отличающаяся, тем, что, устройство управления коммутацией содержит блок управления, первый вход которого соединен с Лорым входом устройства, первый выход блока управления соединен с первым выходом устройства и первыми входами первого, второго и третьего элементов И, первого регистра .указателей и регистра фиксации пути, выход которого соединен с третьим выходом устройства и вто рым входе первого элемента и, первый выход первого регистра указателей соединен с вторым выходом устрой ства и вторым входом второго элемента И, второй выход первого регистра |указателей соединен с вторым входом третьего элемента И, выходы элементов И соединены с вторым входом блока управления и через последовательно соединенные первый приоритетный блок и дешифратор с вторыми входами регистра фиксации пути и первого регистра указателей, второй выход блока управления соединен с первыми входами второго приоритетного блока и узла определения числа единиц, третий выход блока управления соединен с входами регистра свободных узлов и второго регистра указателей, выход которого через узел определения числа единиц соединен с третьим входом блока управления, выход регистра свободных узлов через второй приоритетный блок соединен с пятым выходом устройства, четвертые вход и выход блока управления соединены соответственно с первым входом и четвертым выходом устройства. Источники информации, принятые во внимание при экспертизе 1. Koczela Г.. l.ana Wang G.Y. The design of a Highly Parallel Cofnputer Organization. IEEE Transactions on Computers, tune 1969, c. 18, 6, p, 520-529. 2. Поспелов Д.A. Введение в теорию вычислительных систем, М., Сов, радио, 1972, § 4.2 {прото-тип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1976 |

|

SU983714A1 |

| Микропроцессор | 1980 |

|

SU955077A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| АДАПТИВНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2477882C2 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| РЕЗЕРВИРОВАННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2039372C1 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

:зс

Рг J и

:Ь

0

го

12

/7

11

15

18

1в

Л

/

Авторы

Даты

1982-09-30—Публикация

1974-08-27—Подача